Материал: mikroshemotehnika

Опірний транзистор Vоп |

закривається, переходячи до |

||||||

режиму відсічки. |

Загальний |

емітерний струм IE пере- |

|||||

микається до лівого плеча схеми, і на виходах ЛЕ |

|||||||

установлюються такі потенціали: |

|

|

|||||

|

|

U |

вих |

U0 |

( y 0), |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

Uвих |

U1 |

( y2 1). |

|

||

|

|

|

2 |

|

|

|

|

Отже, цей ЕЗЛ-елемент одночасно виконує дві логічні |

|||||||

операції: АБО НЕ за входом 1 і АБО за виходом 2. |

|||||||

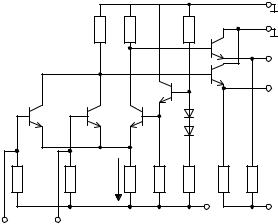

2.4.2 Базовий емітерно-зв’язаний логічний елемент |

|||||||

|

|

|

АБО НЕ/АБО |

|

|||

Схема базового ЕЗЛ-елемента |

АБО НЕ/АБО має ряд |

||||||

особливостей (рис. 2.22). Вона під’єднана до негативної |

|||||||

напруги джерела живлення E 5,2B 5%, |

а колекторні |

||||||

кола заземлюються, оскільки робочі потенціали схеми |

|||||||

стають негативними. |

|

|

|

|

|

||

|

|

|

R1 |

R2 |

|

R3 |

|

|

|

|

|

|

|

V5 |

y2 (АБО) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V6 |

y1(АБО –НЕ) |

|

|

|

|

V4 |

|

|

|

|

V1 |

V2 V3 |

|

VD1 |

|

||

|

|

|

|

|

|

VD2 |

|

|

R8 |

R7 |

IE |

R6 |

R5 |

R4 |

|

x1 |

x2 |

|

|

|

|

— E |

— Uзм |

|

|

|

|

|

|||

Рисунок 2.22 – Базовий ЕЗЛ-елемент АБО НЕ/АБО |

|||||||

|

|

|

|

81 |

|

|

|

Таке ввімкнення не змінює принципу дії елемента, однак заземлення позитивної шини живлення забезпечує

меншу залежність вихідної напруги U0 , U1 від наводок у колі живлення. Це особливо важливо, враховуючи малу величину логічного перепаду в ЕЗЛ-елементах (рис. 2.23).

0 |

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|||

|

|

U 1 |

|

|

|

|||

|

|

|

|

|

||||

-0,8 |

|

|

|

|

x1 |

|

y2 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

-1,2 |

|

U 0 |

x2 |

|

y1 |

|||

-1,8 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвх , В |

|

|

|

|

|

|

|

|

Рисунок 2.23 – Базовий ЕЗЛ-елемент і логічні рівні його потенціалів

Опірна напруга Uоп 1,2B створюється спеціальною

«вбудованою» температурно-компенсованою схемою на опірному транзисторі V3 (подільник R3, R4 , резистор R5,

термокомпенсувальні діоди Vg1, Vg2 , емітерний повторювач на транзисторі V4 ,), яка може живити опірною напругою кілька (до десяти) ЕЗЛ-елементів на одному кристалі.

Вихідні емітерні повторювачі (на V5 і V6 ) призначені

для підсилення вихідних сигналів за потужністю, забезпечення заданої навантажувальної здатності і зміщення рівня сигналів за напругою для забезпечення сумісності ІС за входом і виходом.

Особливістю їх є те, що навантажувальні резистори RH1 і RH2 номіналом 50 Ом, винесені за межі мікросхеми із

метою зниження розсіюваної потужності, можуть бути під’єднані до основного джерела живлення через високоомний резистор.

82

Узгодження вихідних і вхідних напруг рівнів ЕЗЛелементів при їх сумісній роботі забезпечується малим

вихідним опором |

схеми. |

Всі |

входи |

ЕЗЛ-елемента |

( x1,x2,...,xn ) через |

резистори |

R8 , |

R7 з |

опором 50 кОм |

під’єднані до джерела живлення E 5,2B.

Таке під’єднання дозволяє залишати незадіяні входи ІС ЕЗЛ неприєднаними.

З метою виключення впливу імпульсних завад, що виникають у колекторних колах емітерних повторювачів у момент перемикання схеми, використовуються дві роздільні шини «корпус»: одна – для вихідних емітерних повторювачів, друга – для логічної частини схеми.

Робота схеми. Елемент реалізує логічну операцію АБО НЕ/АБО у позитивній логіці з такими значеннями логічних рівнів (рис. 2.23):

|

|

|

Uвх0 1,8В, |

Uвх1 0,8В. |

|

||

Якщо |

x x |

U0 (на |

всі входи |

подаються логічні |

|||

|

|

1 |

2 |

|

|

|

|

«нулі»), |

а |

на |

базу опірного |

транзистора |

V3 прикладена |

||

напруга |

Uоп 1,2B, то вхідні транзистори V1, V2 закри- |

||||||

ваються, |

а транзистор V3 відкритий і працює в активному |

||||||

режимі. |

Через V3 |

протікає загальний емітерний струм IE , |

|||||

величина |

якого |

задається |

опором R6. Цей струм, |

||||

зменшений на величину струму IБ транзистора V3 , створює |

|||||||

на його |

колекторному навантаженні |

R2 |

спад напруги |

||||

UR2 0,8B . Напруга на виході 2 (вихід АБО) при цьому дорівнює

Uвих0 2 1,8В ( y2 0),

ана виході 1 (вихід АБО НЕ)

U1 |

0,8В |

(y 1). |

вих |

|

1 |

1 |

|

|

|

83 |

|

При подачі хоча б на один вхід ( x1 U1) логічної

«одиниці» вхідний транзистор (наприклад, V1) відкрива-

ється, а опірний транзистор V3 переходить до режиму відсічки, оскільки опірна напруга Uоп більш негативна, ніж мінімальне значення U1. При цьому струм IE протікатиме через відкритий вхідний транзистор і резистори R1, R6.

Негативний потенціал на об’єднаних колекторах вхідних транзисторів (вихід 1) набуде значення логічного «нуля»

Uвих0 1 1,8В,

анапруга на виході 2 підвищиться до рівня

Uвих1 2 0,8В.

Таким чином, за виходом 1 базовий ЕЗЛ-елемент виконує операцію АБО-НЕ, а за виходом 2 (транзистор V5 ) – операцію АБО. На основі розглянутого БЛЕ будуються серії 100, 500, К500.

2.4.3 Основні характеристики емітерно-зв’язаних логічних елементів

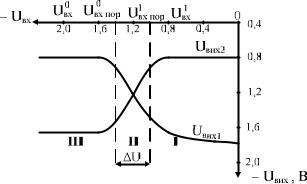

Типова СПХ ЕЗЛ-елемента зображена на рисунке 2.24. На СПХ можна виділити три характерні ділянки:

І – перший усталений режим U1 0,8B на виході 2;

U0 1,8B на виході 1; вхідні транзистори відкриті, в активному режимі, опірний транзистор у режимі відсічки, закритий.

ІІ – активна зона, в якій відбувається перемикання вхідних і опірного транзисторів (усі транзистори в активному режимі).

ІІІ – другий усталений режим:

Uвих1 U1 0,8B; Uвих2 U0 1,8B.

84

Один або всі вхідні транзистори закриті і працюють у режимі відсічки, а опірний транзистор відкритий, в активному режимі.

Рисунок 2.24 – СПХ ЕЗЛ-елемента |

За СПХ при E 5,2B можна визначити такі параметри ЕЗЛ-елемента.

1Логічні рівні: U0 1,6 1,9B , U1 0,8 0,9B.

2Логічний перепад Um U0 U1 0,8 1,0B.

3Порогові значення вхідного сигналу (межі активної

зони): Uвх1 |

пор 1,0В , Uвх0 |

пор 1,4В. |

|

||||||||

4 |

Ширина активної зони |

|

|

|

|

||||||

|

|

U |

|

Uвх1 |

пор Uвх0 |

пор |

|

0,3 0,4B . |

|||

|

|

|

|

||||||||

5 |

Статична завадостійкість |

|

|||||||||

|

|

Um |

|

Um |

U 0,15 0,2B . |

||||||

|

|

зав |

|

|

зав |

|

2 |

|

|

|

|

6 |

Величина напруги джерела опірної напруги |

||||||||||

|

|

Uоп |

1 |

1 |

|

|

0 |

|

|

|

|

|

|

|

2(Uвхпор Uвхпор) 1,2 |

В . |

|||||||

|

|

|

|

|

|

|

85 |

|

|

|

|