Материал: mikroshemotehnika

(переходить до режиму відсічки). Напруга колектора V2

зростає, а напруга емітера V2 зменшується. Транзистор V3

відкривається, і впродовж короткого часу (поки ще не закритий транзистор V4 ) через вихідний каскад протікає

значний струм. |

Для обмеження його призначений опір |

R4 50 500Ом. |

Далі транзистор V4 закривається і |

переходить до |

режиму відсічки, а транзистор V3 – |

відкритий і перебуває в активному режимі. Напруга на виході ТТЛ-елемента

Uвих UКEV4 E U U1,

де U – сумарний спад напруги на R4 , V3 і діоди Vg .

Оскільки U 1,4B, тому в цій схемі U1 3,6B.

Паразитна ємність Cвих швидко заряджається від джерела живлення E 5B через малий вихідний опір емі-

терного повторювача на транзисторі V3 (Rвих 15 200Ом).

Це зумовлює більш високу швидкодію даної схеми

порівняно зі схемою ТТЛ-елемента з простим інвертором.

Ця схема має і більш високу завадостійкість за рахунок наявності фазоінверсного каскаду, який впливає на збільшення крутизни СПХ логічного елемента, внаслідок чого схема відкривається при більшому значенні амплітуди завади Umзав .

Незалежно від стану ТТЛ-елемента один із транзисторів вихідного каскаду (або емітерний повторювач на V3 ,

або інвертор на V4 ) постійно буде проводити струм, забез-

печуючи надходження достатнього струму у навантаження і тим самим підвищуючи навантажувальну здатність даної схеми порівняно зі схемою з простим інвертором.

71

2.3.3Схеми базових елементів стандартних серій цифрових інтегральних схем (133 і 155)

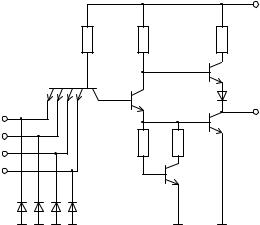

Базовий елемент І НЕ стандартних серій побудований за схемою рисунка 2.14.

|

|

|

|

|

|

+E |

|

|

|

|

R1 |

R2 |

R5 |

|

|

|

|

|

V1 |

V4 |

|

|

|

|

|

VD5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V2 |

x1 |

|

|

|

|

|

y |

|

|

|

|

|

V5 |

|

x2 |

|

|

|

|

|

|

|

|

|

|

R3 |

R4 |

|

x3 |

|

|

|

|

||

|

|

|

|

|

|

|

x4 |

1 |

2 |

3 |

4 |

|

V3 |

|

VD |

VD |

VD |

VD |

|

|

Рисунок 2.14 – Базовий логічний елемент І НЕ

133 і 155 серій

На входах ЛЕ, як правило, вмикаються діоди VD1 VD4 , що виконують демпфірувальну функцію – обмежують амплітуду негативних завад. Замість опору R3

(рис. 2.13) до бази вихідного транзистора V5 під’єднаний коригувальний ланцюжок (R3, R4,V3), що дозволяє

одержати СПХ за формою, наближеною до прямокутної (рис. 2.15), а це підвищує завадостійкість ТТЛ-елемента.

У схемі зі складним інвертором рисунка 2.13 СПХ має нахил на ділянці АВ (рис. 2.15). При вхідній напрузі Uвих 0,7B транзистори V2 і V4 закриті і перебувають у

режимі відсічки. Вихідна напруга Uвих U1 3,6B .

72

|

Uвих |

|

|

4 |

A |

|

|

|

Корекція |

|

|

3 |

|

|

|

2 |

B |

|

|

|

|

|

|

1 |

|

|

|

U0 |

|

|

Uвх |

0 |

0,7 1 1,4 2 |

3 |

|

Рисунок 2.15 – Корекція СПХ базового ЛЕ

Коли ж вхідна напруга досягає 0,7 В, транзистор V2

починає відкриватися, струм IK2 і спад напруги на опорі R2

зростають. Потенціал на колекторі V2 і відтак напруга UБЕ3

на базі V3 зменшуються, і оскільки транзистор V3 працює наразі в активному режимі як емітерний повторювач, то

напруга Uвих також зменшується (ділянка АВ |

на |

СПХ |

|||||||

рисунка 2.15). |

|

|

|

|

|

||||

|

Оскільки транзистор V4 наразі закритий, то струм IE |

||||||||

|

|

|

|

|

|

|

|

|

2 |

проходить |

через |

R3. Нахил СПХ на ділянці |

АВ |

тим |

|||||

більший (тобто Uвих зменшується тим швидше), чим менше |

|||||||||

відношення опорів |

R3 R2 . Тому для збільшення |

Uпор |

і |

||||||

|

|

|

|

|

|

|

|

1 |

|

U |

|

U |

пор |

U0 |

необхідно збільшувати опір |

R |

(щоб |

||

m |

|

|

|

|

3 |

|

|

||

зав |

|

|

1 |

|

|

|

|

|

|

вихідна напруга зменшувалась якомога повільніше, тобто щоб нахил ділянки був меншим). Проте збільшувати величину R3 недоцільно, тому що струм IБ4 буде

зменшуватися під час процесу розсмоктування неосновних носіїв у базі V4 при закриванні V4 (переходу транзистора з режиму насичення до режиму відсічки). Це впливає на зменшування швидкодії ЛЕ при переході U0 U1.

73

З цієї причини корекція форми СПХ (ліквідація ділянки нахилу АВ) здійснюється заміною опору R3 на коригувальний ланцюжок R3, R4 , V3 (рис. 2.14). Резистор

R3 в ньому має малий опір (200 400 Ом). Скоригована СПХ показана на рисунку 2.15 пунктиром. У цьому разі V2 ,

V5 і транзистор коригувального ланцюжка V3 відкри-

ваються практично при одній напрузі Uпор1 1,4B . Відтак завадостійкість Umзав зростає приблизно на 0,7 В: коригува-

льний ланцюжок R3, R4 , V3 зміщує поріг вмикання

елемента в бік більших напруг.

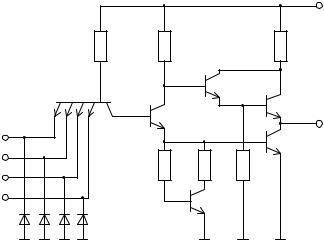

З метою підвищення навантажувальної здатності ТТЛ-елемента (збільшення коефіцієнта розгалуження) застосовується емітерний повторювач на складеному транзисторі V3 , V5 (рис. 2.16).

|

|

|

+E |

|

R1 |

R2 |

|

R6 |

|

V1 |

|

|

V3 |

|

|

|

V2 |

V5 |

|

|

|

y |

||

x1 |

|

|

||

|

|

V6 |

||

x2 |

|

|

||

R3 |

R4 |

R5 |

||

x3 |

||||

|

|

|

||

x4 |

|

|

V4 |

|

|

|

|

Рисунок 2.16 – ТТЛ-елемент на складеному транзисторі

74

2.3.4 Інші різновиди схем ТТЛ-елементів

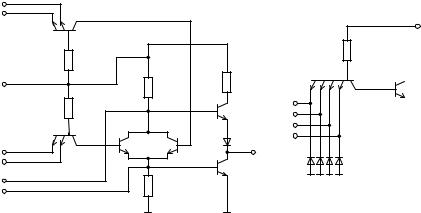

Крім ТТЛ елементів І НЕ, до складу серії входять і широко застосовуються базові ЛЕ І АБО НЕ (рис. 2.17 а). Такий елемент містить декілька схем І (багатоемітерні транзистори V1 і V2 , резистори R1, R2 ).

Виходи схем І (колектори багатоемітерних транзисторів) з’єднані з базами транзисторів V3 , V4 . З’єднані тран-

зистори V3 і V4 реалізують операцію АБО, а під’єднаний до їх виходу інвертор V5 – операцію НЕ.

Максимальне число об’єднань становить не більше 8. З метою розширення числа входів такого ЛЕ по АБО до точок А, В схеми можна під’єднати схему розширювача

логіки (рис. 2.17 б), який являє собою багатоемітерний транзистор, з’єднаний з транзистором V2 . При увімкненні

одного розширювача швидкодія ЛЕ погіршується приблизно на 5 нс, а споживана потужність збільшується на 5 мВт.

x1 |

|

|

|

x2 |

|

|

|

V1 |

|

|

|

R1 |

|

|

|

+E |

R3 |

|

R5 |

|

|

||

|

|

|

|

R2 |

|

|

V5 |

V2 |

|

|

VD |

x3 |

V3 |

V4 |

|

x4 |

|

|

V6 |

A |

R4 |

|

|

B |

|

|

|

|

|

|

R1 |

V1 |

+E

A

A

V2  B

B

а) |

б) |

Рисунок 2.17 – ТТЛ-елемент І АБО НЕ з можливістю розширення логіки за АБО

75