Материал: mikroshemotehnika

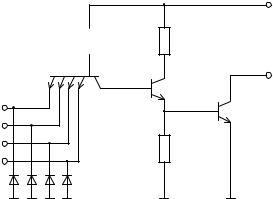

До складу стандартних ТТЛ-серій входять ЛЕ без колекторного навантаження вихідного ключа – інвертора – ЛЕ з так званим «відкритим» колектором (рис. 2.18). Ці логічні елементи призначені для роботи із зовнішнім навантаженням – індикаторними приладами, реле, лініями затримки тощо. Базовими ЛЕ деяких серій ЦІС (наприклад, 530, 531) є так звані ТТЛШ-елементи. Ці ЛЕ побудовані за такими самими схемотехнічними принципами, що і ТТЛелементи (наприклад, схема рисунка 2.16 зі складеним транзистором), однак замість звичайних транзисторів у них застосовуються транзистори з діодом Шотткі. Такі ТТЛШелементи мають підвищену швидкодію.

+E

R1 |

|

R2 |

|

|

|

V1

|

V2 |

|

x1 |

V3 |

|

x2 |

||

|

||

x3 |

R3 |

|

x4 |

||

|

Рисунок 2.18 – ЛЕ з «відкритим» колектором

2.3.5 Основні характеристики і параметри ТТЛ-елементів

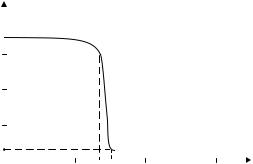

СПХ ТТЛ елемента І НЕ зі складним інвертором (рис. 2.13) показана на рисунку 2.19.

Характерними ділянками на ній є:

І – закритий стан транзистора V2 ; Uвих U1 3,6B .

ІІ – транзистор V2 відкритий, а транзистор V4 – ще закритий.

76

ІІІ – транзистор V2 , |

V3 і |

V4 |

відкриті, в активному |

|||||||

режимі. |

|

|

|

|

|

|

|

|

|

|

ІV – транзистори V2 |

і V4 |

в режимі насичення, V3 – |

||||||||

закритий. Uвих U0 |

0,2B. |

|

|

|

|

|

||||

Uвих |

|

В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

U1 |

|

I |

|

|

|

|

|

|

|

|

3 |

|

|

II |

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

III |

|

|

|

|

|

|

U0 |

|

|

|

|

|

IV |

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвх,В |

|

0 |

|

U0 |

1 Uпор1 Uпор2 |

2 |

U1 |

3 |

|

|||

|

|

|

||||||||

Рисунок 2.19 – СПХ ТТЛ-елемента зі складним інвертором

Параметри БЛЕ І НЕ можуть бути визначені за СПХ

(E 5B).

Логічні рівні: U0 0,2 0,4B, |

U1 2,4 3,6B . |

|||||||

Пороги перемикання Uпор |

1,4B , Uпор |

2 |

1,5B . |

|||||

|

|

|

1 |

|

|

|

|

|

Ширина |

активної |

області |

|

(зона неозначеності) |

||||

U 0,1 0,2B. |

|

|

|

|

|

|

|

|

Статична |

завадостійкість |

(у |

|

діапазоні |

температур |

|||

60... 125°C) Um |

0,4 1,0B ; Um |

0,4 0,6B . |

||||||

|

зав |

|

|

|

зав |

|

|

|

Коефіцієнт об’єднання за входом Kоб 8. |

|

|||||||

Коефіцієнт розгалуження за виходом Kроз 10. |

||||||||

Швидкодія: |

tз |

10 30нс; |

|

|

|

|

||

- для ТТЛ |

|

|

|

|

||||

|

|

сер |

|

|

|

|

|

|

- для ТТЛШ |

tз |

5нс . |

|

|

|

|

||

|

|

сер |

|

|

|

|

|

|

|

|

|

77 |

|

|

|

|

|

Споживана потужність Pсер 20 40мВт,

для 134 серії Pсер 2мВт.

Чим більша частота перемикання БЛЕ, тим більша їх споживана потужність.

2.4 Емітерно-зв’язані логічні елементи

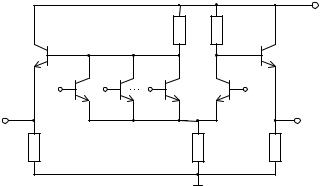

Основна перевага емітерно-зв’язаних логічних елементів (ЕЗЛ) перед ТТЛ-елементами – це більша швидкодія (наприклад, серія 500 із часом затримки на каскад 2 нс). Основу будови БЛЕ ЕЗЛ-типу складають описані у 2.2.2 потенціальні інвертори з перемиканням емітерного струму. Такий ПІ має два виходи – прямий та інверсний, що дозволяє розширити логічні можливості елемента.

Висока швидкодія ЕЗЛ-елементів зумовлена роботою біполярних транзисторів, що входять до складу перемикачів струму, в ненасиченому (лінійному, активному) режимі. Зменшення часу затримки передавання сигналу досягається також за рахунок обмеження логічного перепаду вихідної напруги. Проте ця обставина приводить до зменшення завадостійкості ЛЕ.

2.4.1 Основна схема емітерно-зв’язаного логічного елемента АБО-НЕ/АБО

Принцип будови і функціонування ЕЗЛ-елемента розглянемо на прикладі його основної схеми, яка реалізує операцію АБО НЕ/АБО (рис. 2.20).

Схема побудована на базі перемикача емітерного струму (транзистори V1, V2 , …, Vn і Vоп ). В одне плече схеми паралельно ввімкнено кілька біполярних транзисторів (V1,V2 , …, Vn ), число яких дорівнює кількості входів ЛЕ. Вхідні сигнали подаються на їхні бази. Vоп – опірний транзистор, на базу якого подається опірна напруга Uоп .

78

RK |

RK |

+E |

|

||

Vвих1 |

|

Vвих2 |

x1 V1 x2 V2 xn Vn |

V0n |

U0n |

|

|

|

y1 |

|

y2 |

+ |

|

|

RE1 |

RE |

RE2 |

— |

|

|

Рисунок 2.20 – Основна схема ЕЗЛ-елемента АБО НЕ/АБО

Емітери транзисторів Vоп , V1, V2 , …, Vn з’єднані між собою і під’єднані до спільного резистора RE . Вихідні сигнали знімають з колекторів плечей схеми через емітерні повторювачі Vвих1 і Vвих2 . Емітерні повторювачі забезпечу-

ють сумісність ЛЕ за вхідними і вихідними рівнями напруги, а також зменшують вихідний опір ЛЕ з метою підвищення його навантажувальної здатності і швидкодії.

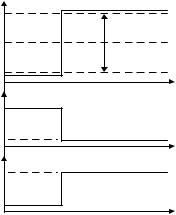

Розглянемо роботу ЕЗЛ-елемента в позитивній логіці: E U1 Uоп – високий потенціал; U0 Uоп – низький потенціал (рис. 2.21). Логічні рівні U1 і U0 необхідно вибирати симетричними стосовно напруги Uоп , а величина логічного перепаду Umвх повинна перевищувати ширину

активної зони U (рис. 2.21), тобто

Umвх U1 U0 U .

Нехай на всі входи ЕЗЛ-елемента надходять логічні «нулі», тобто

x1 x2 ... xn U0 .

79

Усі вхідні транзистори V1, V2 , …, Vn закриваються і переходять до режиму відсічки, а опірний транзистор Vоп –

відкритий і працює в активному режимі. Через нього протікає весь струм IE .

U1 |

Uвх |

|

|

U0n |

ΔU |

|

|

U0 |

t |

0 |

|

Uвих1 |

|

U1 |

|

U0 |

t |

0 |

|

Uвих2 |

|

U1 |

|

U0 |

t |

0 |

Рисунок 2.21 – Діаграми напруг основної схеми ЕЗЛ-елемента

На виходах ЛЕ установлюються потенціали

Uвих1 E U1 ( y1 1),

Uвих2 E IERK U0 ( y0 0).

Якщо хоча б на один із входів ЕЗЛ-елемента подається

логічна «одиниця» (наприклад, x U1 |

E ), а на решту |

1 |

|

входів – логічні «нулі» ( x2 x3 ... xn U0 ), то вхідний транзистор V1 відкривається і переходить до активного режиму, шунтуючи решту транзисторів V2 , V3 , …, Vn .

80