Материал: mikroshemotehnika

ЕЗЛ-елементи є найбільш швидкодійними з усіх існуючих ЦІС, працюють при частоті перемикання, яка перевищує 100 МГц. Однак велика споживана потужність і низька завадостійкість обмежують їх застосування і зумовлюють необхідність ужиття спеціальних заходів їх захисту від наводок. ЦІС ЕЗЛ-типу несумісні за напругою живлення і логічними рівнями з ЦІС інших типів. Для усунення цього недоліку до складу серій входять допоміжні ІС (перетворювачі логічних рівнів).

Логічні елементи на МОН-структурах з індукованим p-каналом мають підвищену завадостійкість, але низьку швидкодію і велике енергоспоживання. Для їх роботи потрібні високовольтні (до – 27 В) джерела живлення і високі рівні логічних сигналів. Тому ЛЕ МОН-типу несумісні з усіма розглянутими типами ЛЕ.

Логічні елементи на КМОН-структурах істотно відрізняються за своїми властивостями від логічних елементів на МОН-структурах. Вони мають позитивну напругу живлення, споживають на кілька порядків меншу потужність, мають більшу швидкодію і завадостійкість. Функціональний склад серій на КМОН-структурах відрізняється різноманітністю, що дозволяє застосовувати ці серії для побудови будь-яких цифрових вузлів із тактовою частотою до 5 МГц.

Логічні елементи з інжекційним живленням мають швидкодію на порядок нижчу від швидкодії ЕЗЛ-схем, але приблизно однакову з ТТЛ- і КМОН-елементами. Завадостійкість їх найменша серед усіх типів ЛЕ. Проте за малими рівнями споживаної потужності цей тип ЛЕ може бути порівняний лише з ЛЕ на КМОН-структурах. Не меншою перевагою ЦІС з інжекційним живленням є те, що вони мають найбільшу серед усіх типів розглянутих схем щільність пакування, а тому найменші габарити.

101

Таким чином, для проектування та експлуатації електронних систем необхідним є всебічне урахування основних властивостей застосовуваної елементної бази з метою досягнення високих техніко-економічних показників.

3 Схемотехніка комбінаційних схем на програмованих логічних матрицях

3.1 Призначення і сфера застосування

Програмовані логічні матриці (ПЛМ) являють собою логічну схему для перетворення множини вхідних значень

у відповідну множину вихідних даних

у відповідну множину вихідних даних

у двійковому коді. Правило перетворення вхідних змінних у функціях задається таблицею істинності. ПЛМ реалізує систему булевих функцій.

у двійковому коді. Правило перетворення вхідних змінних у функціях задається таблицею істинності. ПЛМ реалізує систему булевих функцій.

Програмовані логічні матриці широко застосовуються в програмованих логічних інтегральних схемах (ПЛІС). Наприклад, ПЛІС із плавкими запобіжниками за технологією ТТЛШ, в складі яких уже давно відомі ПЛМ К556РТ1,

КР556РТ2, КР556РТ21.

Де можливе застосування ПЛІС?

По-перше, під час розроблення оригінальних і нестандартних пристроїв у комп’ютерах та системах керування, а також для заміни звичайних інтегральних мікросхем малого і середнього ступенів інтеграції. При цьому значно зменшуються розміри, потужність споживання й збільшується надійність пристроїв і систем, де вони використовуються.

По-друге, використання ПЛІС дає можливість значно зменшити час та затрати на проектування схем, розширити можливості розроблення модифікацій комп’ютерів.

По-третє, при проектуванні на основі ПЛІС пристроїв для захисту програмного забезпечення виробів від несанкціонованого доступу і копіювання ПЛІС має таку технологічну особливість, як «біт секретності», після програмування якого схема стає недоступною для читання.

102

Але найбільш широко ПЛІС використовують у мікропроцесорній та обчислювальній техніці. На їх основі розробляють контролери, адресні дешифратори, логіку обладнання мікропроцесора та ін. На основі ПЛІС часто виготовляють мікропрограмні автомати, спеціалізовані пристрої, схеми обробки сигналів і відображення, процесори швидкого перетворення Фур’є і т. д.

3.2 Принципи побудови базової програмованої логічної матриці

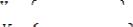

Виготовлювані електронною промисловістю ПЛІС мають у собі базову структуру програмованої логічної матриці, яка включає матрицю кон’юнкторів (матриця «І») і матрицю диз’юнкторів (матриця «АБО»). Принцип побудови таких ПЛМ розглянемо на ПЛІС серії К556РТ1.

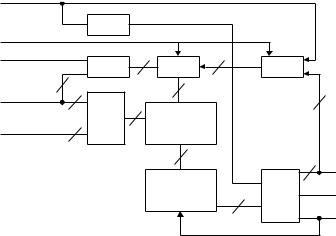

Ця ПЛІС (рис. 3.1) включає матрицю кон’юнкторів (матриця «І»), матрицю диз’юнкторів (матриця «АБО»), блок вхідних підсилювачів (ВП), блок вихідних каскадів (ВК), схему дозволу вибірки кристалу (ДВ), програмований дешифратор, програмовані адресні формувачі (АФ1, АФ2). Вхідні підсилювачі формують прямі та інверсні значення вхідних змінних з усіх шістнадцяти входів (А1…А16).

Програмований дешифратор (DC) і програмовані адресні формувачі (АФ1, АФ2) використовують у режимах програмування і контролю ПЛІС.

Для наочності і більш повного розуміння принципу побудови ПЛМ розглянемо базову функціональну схему ПЛІС серії К556РТ1, яка містить у собі лише основні вузли схеми матриці «І», «АБО», вхідні і вихідні каскади

(рис. 3.2).

103

CS (ДВ ) |

|

|

|

|

|

|

РП |

|

ДВ |

|

|

|

|

|

|

|

|

|

|

|

Uп |

|

АФ 1 |

DC |

АФ 2 |

|

|

|

|

|

|

|||

А1 … _А6 |

6 |

12 |

48 |

12 |

|

|

ВП |

|

|

|

|||

Матриця |

|

6 |

|

|||

А7 … _А16 |

6 |

|

|

|

||

10 |

32 |

«I» |

|

|

|

|

|

|

48 |

|

|

|

|

|

|

|

|

|

В1 |

|

|

|

|

Матриця |

ВК |

|

|

|

|

|

6 |

В7 |

||

|

|

|

«АБО» |

|

|

В8 |

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

Рисунок 3.1 – Структурна схема даної ПЛІС |

|

|||||

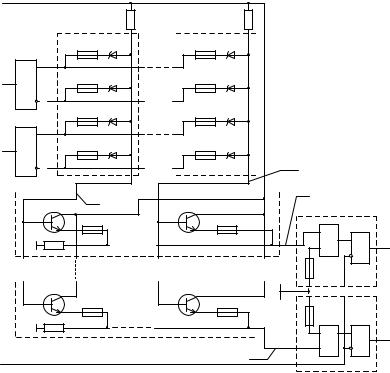

Вхідні підсилювачі (ВП1–ВП16) формують прямі й інверсні значення вхідних змінних, які надходять у матрицю «І». Для керування вхідними підсилювачами є шістнадцять входів (А1–А16). Вхідні підсилювачі побудовані на основі двох послідовно ввімкненних буферних логічних схем

I НЕ.

Основними вузлами мікросхеми К556РТ1 є матриці «І» і «АБО», які реалізують дворівневі логічні функції. Перший рівень ПЛМ складається із 48 кон’юнкторів (матриця «І»), які з’єднані за допомогою плавких ніхромових перемичок з будь-яким із шістнадцяти спільних входів через буферні схеми. У матриці «І» реалізують кон’юнкції вхідних змінних, причому кожна вхідна змінна може входити в кон’юнкцію прямим або інверсним значенням, або не входити зовсім. Вхідні сигнали, які з’являються на вхідних шинах матриці «І», вводяться в

матрицю «АБО», яка утворює другий логічний рівень і реалізує диз’юнкції заданих кон’юнкцій.

104

UK |

|

|

|

|

|

|

|

|

K1 |

R9 |

|

R56 |

|

|

|

|

|

|

K48 |

|

|

|

|

ВП1 |

F1 |

VD1 |

|

F1881 VD1505 |

|

|

|

A1 |

|

48 |

|

|

|

|

|

F |

|

|

|

|

|

||

|

|

|

F1882 VD1506 |

|

|

|

|

A1 |

F2 |

VD2 |

|

|

|

|

|

|

A1 |

|

48 |

|

|

|

|

ВП16 |

F31 |

VD31 |

|

F1911 VD1535 |

|

|

|

A16 |

|

48 |

|

|

|

|

|

F |

|

|

|

|

|

||

F32 |

VD32 |

|

F1912 VD1536 |

|

|

|

|

A16 |

|

|

|

|

|||

|

A16 |

|

48 |

|

P48 |

|

|

|

P1 |

|

|

|

S1 |

|

|

|

|

|

VT377 |

|

|

|

|

|

VT1 |

|

|

BK1 |

|

|

|

Д1 |

F33 |

|

|

F1913 |

|

|

|

|

|

|

|

|

|||

|

R1 |

48 |

|

|

=1 |

& |

B1 |

|

|

|

|

||||

|

|

|

|

|

F1921 |

|

|

Д8 |

VT8 |

|

|

VT384 |

|

|

|

F40 |

|

|

F1920 |

|

|

|

|

|

|

|

|

|

|

||

|

R8 |

48 |

|

|

F1928 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

=1 |

& |

B8 |

CS(ДВ) |

|

|

|

|

S8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BK8 |

|

|

Рисунок 3.2 – Базова функціональна схема ПЛІС К556РТ1, ВП1–ВП16 – вхідні підсилювачі; К1–К48 – кон’юнктори матриці «І»; Д1–Д8 – диз’юнктори матриці «АБО» ВК1–ВК8 – вихідні каскади; Р1–Р48 – шини кон’юнкцій;

S1–S8 – шини диз’юнкцій;

F1–F1928 – плавкі ніхромові перемикачі; VD1–VD1536 – діоди Шотткі; VT1–VT384 – транзистори;

R1–R56 – резистори.

105