Материал: mikroshemotehnika

x1 |

|

x2 |

|

|

|

|

|

|

b |

+E |

Uвх , В |

|

|

|

|

|

V4 |

U1 |

||

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

b |

V3 |

0 U0 |

|

|

|

|

|

t |

|||

|

|

|

y=x1+x2 |

x1 |

1 |

|

c |

|

c |

|

y |

||

|

|

x2 |

|

|||

|

|

|

|

|||

|

V1 |

V2 |

|

|

|

|

|

|

|

|

|

||

VD1 |

|

VD2 |

Cвих |

|

|

|

|

|

|

|

|

||

|

|

а) |

|

|

б) |

|

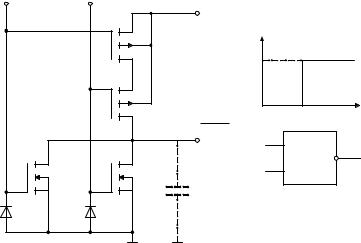

Рисунок 2.27 – Логічний елемент АБО НЕ на |

|

|||||

|

|

КМОН-структурах |

|

|

|

|

Якщо |

хоча б на один із входів |

подається |

логічна |

|||

«одиниця», |

наприклад, |

x U1 9B, |

то |

транзистор V |

||

|

|

а V4 – |

1 |

|

|

1 |

відкривається, |

закривається. |

На |

виході |

схеми |

||

Uвих 0B U0 .

Ємність Cвих швидко розряджається через відкритий транзистор V1. Швидкий перезаряд Cвих в обох стаціо-

нарних станах ЛЕ сприяє підвищенню його швидкодії.

91

|

+E |

|

V3 |

V4 |

|

|

x1 |

& |

|

y=x1x2 |

y |

|

x2 |

|

x2 |

V2 |

|

|

|

|

x1 |

Cвих |

|

V1 |

|

|

|

|

|

VD1 |

VD2 |

|

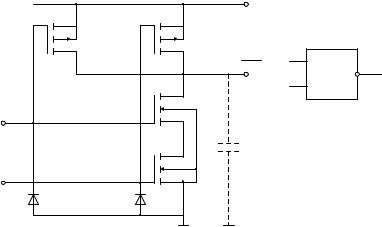

Рисунок 2.28 – Логічний елемент I НЕ на КМОН-структурах

Схема I НЕ

Схема показана на рисунку 2.28 а. Вона працює в

позитивній логіці (U1 E 9B, |

U0 0B ). Операція |

I НЕ |

|

реалізується так. При x x U1 |

комутувальні транзистори |

||

1 |

2 |

|

|

V1 і V2 відкриваються, |

а навантажувальні (V3 |

і V4 ) |

|

закриваються і Uвих U0 0B.

Коли, наприклад, x1 U0 0B, то транзистор V1 закри-

вається, а доповнюючий його навантажувальний транзистор

V4 відкривається, і напруга на виході схеми Uвих U1 9B.

Розглянуті схеми рисунків 2.27 а і 2.28 а є базовими для побудови ЦІС КМОН-типу серій 176, К561, 564.

Мінімальна напруга живлення цих схем визначається пороговою напругою р-канального транзистора Uпорp

(причому Uпорp Uпорn ).

92

Оскільки напруга живлення E Uпорp , то цим

забезпечується висока завадостійкість даних ЛЕ: діоди VD1

і VD2 у схемах – демпфірувальні: шунтують входи ЛЕ при дії завад негативної полярності.

2.5.3 Основні характеристики і параметри логічних елементів на КМОН-транзисторах

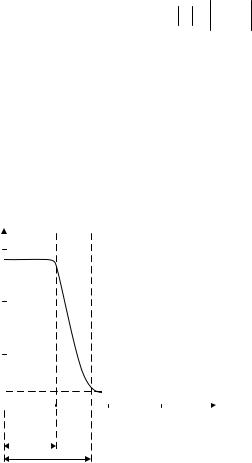

Типова СПХ логічного елемента на КМОН-структурах при E 9B показана на рисунку 2.29.

|

|

|

Uвих,В |

|

|

|

||

|

|

|

|

|

||||

9 |

|

|

I |

|

II |

III |

|

|

U1 |

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

Uвх,В |

|

|

|

|

|

|

|

||

|

|

U0 |

3 |

6 U1 9 |

||||

|

|

Uвх відкр |

|

|

|

|||

|

|

|

|

|

|

|

|

|

Uвх закр

Рисунок 2.29 – СПХ логічного елемента на

КМОН-структурах

На характеристиці можна вирізнити три ділянки.

І – перший стаціонарний режим Uвх U0 0,8B.

Комутувальні транзистори закриті, навантажувальні – відкриті: Uвих U1 8,2B.

93

ІІ – режим перемикання. При напрузі Uвх.відкр

комутувальні транзистори відкриваються. При Uвх.закр

схема остаточно переходить в інший стаціонарний режим.

ІІІ – другий стаціонарний режим Uвх U1 8,2B.

Комутувальні транзистори відкриті, навантажувальні –

закриті: Uвих U0 |

0,8B. |

|

|

|

|

||

Параметри ЛЕ на КМОН |

|

|

|

||||

1 |

Логічні рівні: U0 0,8B , U1 |

8,2B. |

|||||

2 |

Логічний перепад Um |

U1 |

U0 |

7,4B . |

|||

|

|

|

вх |

|

|

|

|

3 |

Ширина зони неозначеності UH 0,1B. |

||||||

4 |

Статична завадостійкість: |

|

|

|

|||

|

Um |

Uвх.відкр Uвх0 Uпор |

n |

2 3B , |

|||

|

зав |

|

|

|

|

|

|

|

Um |

|

Uвх1 Uвх.закр Uпор |

3B. |

|||

|

зав |

|

|

|

|

p |

|

Із причин великого розкиду порогових напруг у практичних схемах завадостійкість логічних елементів на КМОН-структурах становить 30 – 40 % від Е і значно перевищує завадостійкість інших типів логіки – ТТЛ, ЕЗЛ і МОН.

5 Kоб 4. При збільшенні числа входів (числа

навантажувальних транзисторів) вихідна напруга спадає і може бути недостатньою для надійного закривання навантажувальних транзисторів наступного логічного елемента.

6 Kроз 100. Це пояснюється практичною відсутні-

стю вхідних струмів у ЛЕ КМОН. На практиці збільшення Kроз обмежується лише зниженням швидкодії з причини

зростання паразитної ємності Cвих.

94

7Швидкодія – середня (як у ТТЛ-елементів): tзадсер 20 50нс.

8Середня споживана потужність Pсер.спож становить

десятки мікроват. Дуже мала споживана потужність – це основна перевага логічних елементів на КМОН.

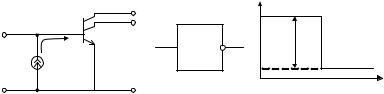

2.6 Логічні елементи з інжекційним живленням

Логічні елементи з інжекційним живленням побудовані з ключів-інверторів як складових частин. Ці складові частини є елементами інтегральної інжекційної логіки

(I2 -елементами), їх напівпровідникова структура описана у посібнику [1]. На рисунку 2.30 а показана еквівалентна

схема I2 -елемента.

|

|

K1 |

|

|

Uвх |

U1 = 0,75 В |

Б |

V |

K2 |

|

1 |

|

|

|

|

|

|

|||

|

Iг |

|

x |

y |

Umвх |

|

|

|

|

U0= 0,05 В |

|||

|

Iг |

|

|

|

|

|

Е |

|

|

|

0 |

|

t |

|

|

|

|

|

|

а) |

б) |

в) |

Рисунок 2.30 – Елементарний вентиль (ключ-інвертор) з інжекційним живленням

На схемі генератор струму – це інжектор, транзистор

V – багатоколекторний транзистор. I2 -елемент функціонує у позитивній логіці. Заміна резистора генератором струму дозволяє забезпечувати роботу елемента малою напругою живлення (E 1,0 1,5B). Відтак логічні рівні

малі і становлять U1 0,75B , U0 0,05B (рис. 2.30 в).

95