Материал: mikroshemotehnika

Інші електричні параметри ЕЗЛ-елемента.

1 Kоб 5. Коефіцієнт об’єднання обмежений числом

вхідних транзисторів, збільшення їх числа призводить до зменшення швидкодії.

2 Kроз 10 – коефіцієнт розгалуження. Це зумовлене

тим, що на виходах ЛЕ є емітерні повторювачі. Крім того, вхідні транзистори ЛЕ мають малу величину вхідного струму Iвх 260мкА.

3 Рівень допустимих завад Umзав 0,15... 0,2B.

Низька завадостійкість є основним недоліком таких елементів. Але сам елемент має малий рівень власних генерованих завад.

4 Швидкодія ЕЗЛ-елементів – найвища серед існуючих ЛЕ. При RH 51Ом tзадсер 1,5 2,0нс.

5 Споживана потужність досить висока

Pсерспож 25 35мВт,

і це істотний недолік ЕЗЛ-елементів, які потребують внаслідок цього потужних джерел живлення.

2.5 Логічні елементи на МОН- і КМОН-транзисторних структурах

Значного поширення в електронній техніці набули цифрові ІС, побудовані на ЛЕ, які містять у своєму складі інтегральні МОН-транзистори з індукованим каналом. Такі ІС мають високий ступінь інтеграції і високу швидкодію. Особливо це стосується ЦІС на комплементарних доповнюючих МОН-структурах (КМОН). Вони дуже компактні (до 100000 елементів на кристалі) і відрізняються надзвичайно низьким енергоспоживанням.

Серії ЦІС на МОН К172, 178, 186 – історично перші, їм була притаманна мала швидкодія і велика споживана потужність.

86

Ці недоліки були усунені в ЦІС на КМОН-структурах серій 176, К561, 564 і т. д.

Схемотехнічна основа ЛЕ на МОН-структурах – це схеми потенціальних інверторів на однотипних і комплементарних МОН-структурах з індукованими каналами, розглянуті у 2.2.3.

2.5.1 Логічні елементи на р- канальних МОНтранзисторних структурах

Базовими логічними елементами для побудови серій ЦІС на МОН-структурах є елементи АБО НЕ, I НЕ.

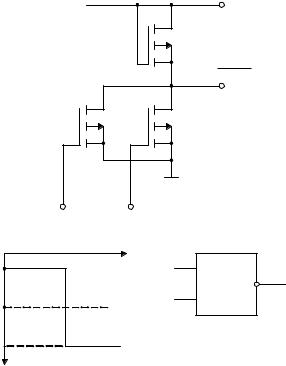

Схема АБО НЕ

Схема АБО НЕ подана на рисунку 2.25 а. Вона працює у негативній логіці при напрузі джерела живлення E 27B 10% і таких значеннях логічних рівнів:

U1 20B, U0 2,0B.

Нехай на всі входи ЛЕ надходять логічні «нулі»:

x x U0 |

2B |

( |

U0 |

|

U |

пор |

), |

1 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

де Uпор – порогова напруга МОН-транзистора.

Тоді всі активні (комутувальні) транзистори Va1 , Va2

будуть закриті, у той час як навантажувальний транзистор

VH відкритий постійно ( E Uпор ).

Напруга на виході ЛЕ Uвих U1 20B .

При надходженні хоча б на один із входів ЛЕ логічної

«одиниці», наприклад, x U1 |

20B |

( |

U1 |

|

U |

пор |

), |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

відповідний комутувальний транзистор Va1 відкриється,

створюючи шлях для протікання струму. Напруга на виході ЛЕ Uвих U0 2,0B .

87

|

|

|

|

—E |

|

|

|

|

Vн |

|

|

|

|

y= x1+ x2 |

|

|

|

Va1 |

Va2 |

|

|

x1 |

|

x2 |

|

|

|

|

а) |

— |

2,0 |

U0 |

t |

x1 1 |

|

|

|

y |

|

|

|

|

|

|

Uпор |

|

|

x2 |

|

|

|

|

||

— 20 |

|

U1 |

|

|

|

Uвх,В |

|

|

|

|

|

б) |

|

в) |

|

Рисунок 2.25 – Логічний елемент АБО НЕ |

|||

|

|

на МОН-транзисторах |

||

Недолік схеми рисунка 2.25 а: зі збільшенням числа входів ЛЕ (числа комутувальних транзисторів) знижується рівень логічної «одиниці» за рахунок спаду напруги на навантаженні від сумарного наскрізного струму у колах «стік – витік» транзисторів Va. Але оскільки він дуже

малий, то значення Kоб цієї схеми досягає величини 10.

88

Схема I НЕ

Ця схема (рис. 2.26 а) використовує не паралельне, а послідовне ввімкнення комутувальних транзисторів.

— E

Vн

Vн

y = x1 x2

x2

x1 &

y

x2

x1 |

Va1 |

x2 |

Va2 |

а) б)

Рисунок 2.26 – Логічний елемент I НЕ на МОН-транзисторах

Схема |

працює |

в |

негативній |

|

|

логіці |

U1 20B; |

||||||||||||||

U0 2,0B. |

При x x |

U1 ( |

|

U1 |

|

|

|

|

U |

пор |

|

) через |

всі |

||||||||

|

|

|

|

|

|||||||||||||||||

|

1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

послідовно ввімкненні транзистори Va , |

Va , |

VH |

|

протікає |

|||||||||||||||||

|

|

|

|

|

|

1 |

|

|

|

|

2 |

|

|

|

|

|

|

||||

струм, і на виході ЛЕ Uвих U0 2,0B. |

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Якщо |

ж, наприклад, |

x U0 ( |

|

U0 |

|

|

|

U |

пор |

|

), |

то |

V |

||||||||

|

|

|

|

||||||||||||||||||

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

закривається, коло протікання струму розривається, і напруга на виході ЛЕ Uвих U1 20B .

Для елементів I НЕ (рис. 2.26 а) Kроз 10 20,

Kоб 4 (достатньо висока навантажувальна здатність).

89

Схеми більш складних ЛЕ (схеми із двоступінчастою логікою) одержують комбінуванням послідовного і паралельного ввімкнення комутувальних (активних) транзисторів.

ЛЕ на однотипних МОН-структурах мають невисоку швидкодію (tзадсер сотні нс), велике енергоспоживання

(Pзадсер 40 мВт на один ЛЕ) і великі рівні вихідної напруги, несумісні з рівнями ЦІС ТТЛ-типу.

2.5.2 Логічні елементи на КМОН-транзисторних структурах

Логічні елементи на КМОН-структурах одержують з’єднанням:

– групи послідовно ввімкнених транзисторів одного

типу;

– групи паралельно ввімкнених транзисторів іншого

типу.

Число транзисторів у кожній групі дорівнює числу входів ЛЕ.

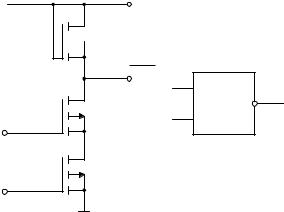

Схема АБО НЕ

Схема наведена на рисунку 2.27 а. ЛЕ працює в позитивній логіці при напрузі джерела живлення E 9B 5% з такими логічними рівнями:

|

|

U1 E 9B; |

U0 0B. |

|

|

|

При x x |

2 |

U0 0B комутувальні транзистори V |

|

і |

||

1 |

|

|

1 |

|

||

V2 закриваються, а навантажувальні транзистори V3 і V4 |

|

– |

||||

відкриваються |

(оскільки Uвх0 |

Uзв 9В ). |

Напруга |

на |

||

виході ЛЕ Uвих E U1. |

|

Cвих швидко |

||||

При цьому вихідна паразитна ємність |

||||||

заряджається через відкриті транзистори V3 , V4 .

90