Материал: mikroshemotehnika

|

|

|

|

|

|

+Ec |

Ic |

|

|

Uзв2 |

|

b |

V2 (p) |

|

|

||

|

|

|

|

|

|

U1 |

|

|

|

|

|

|

|

|

Uзв |

|

|

|

Uвх |

|

|

|

c |

U0 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Uвих |

|

|

|

|

|

|

|

c |

Ic |

|

|

|

U1 |

|

|

|

|

|

||

|

|

|

|

|

|

Uзв |

|

|

|

U0 |

|

|

|

|

V1 (n) |

|

|

|

Uзв2 |

|

|

|

|

|||

|

|

|

|

|

|

b |

а) |

|

|

|

|

|

|

|

а) |

|

|

|

|

|

|

|

|

|

|

|

|

+Ec |

|

|

|

+Ec |

|

||

|

V |

2 |

(R |

= ) |

|

V2 (Ri= 0) |

||

|

|

|

ii |

|

|

|

|

|

Uвх=U1 |

Uвих = U0 |

Uвх=U0 |

Uвих = U1 |

|||||

|

V |

(R = 0) |

|

V1 |

(Ri= ) |

|||

|

|

|

i |

|||||

|

1 |

|

|

i |

|

|

|

|

|

|

|

|

|

б) |

|

|

в) |

|

б) |

|

|

|

|

|

в) |

|

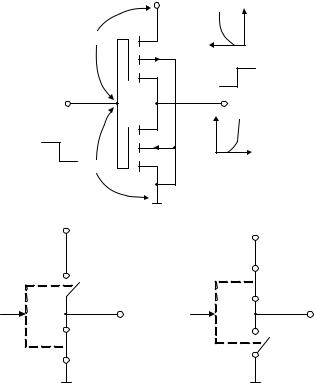

Рисунок 2.11 – Потенціальний інвертор на КМОН-транзисторах

Склад схеми. V1 – комутувальний транзистор із каналом n-типу. V2 – навантажувальний транзистор із каналом p-типу. Вхідний сигнал подається на об’єднані затвори V1 і V2 , вихідний сигнал знімається з об’єднаних стоків транзисторів:

U1 Uпор (U1 Ec); U0 0 Uпор .

66

|

|

Принцип дії. Нехай на вхід подається U |

вх |

U1 E . |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

c |

|

При цьому Uзв Ec , Uзв |

2 |

0, |

і транзистор V1 відкритий |

||||||||||||||

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

(ключ замкнений), а |

транзистор |

V2 |

закритий (ключ |

||||||||||||||

розімкнений). Вихідний потенціал |

Uвих U0 0. |

Якщо |

ж |

||||||||||||||

U |

вх |

U0 0, |

то U |

зв |

0, |

U |

зв |

E |

(| E | U |

пор |

), |

і |

|||||

|

|

|

|

|

|

|

2 |

c |

c |

|

|

|

|

||||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

транзистор |

V1 |

закривається (ключ розімкнений), а |

|||||||||||||||

транзистор V2 |

відкривається (ключ замкнений). |

Вихідний |

|||||||||||||||

потенціал Uвих U1 Ec .

Перевага ПІ на КМОН-транзисторах: в обох стаціонарних станах загальний опір ПІ дуже великий (Ri ) ,

що відповідає практичній відсутності споживання струму від джерела живлення.

2.3 Транзисторно-транзисторні логічні елементи

Близько 60 % усіх ЦІС побудовані на основі транзис- торно-транзисторних елементів (ТЛЛ-елементів). Основний схемотехнічний їх елемент – схема потенціального інвертора з перемиканням базового струму. Роль БЛЕ при побудові серій ЦІС можуть виконувати логічні елементи І НЕ, АБО НЕ , І АБО НЕ. Операцію «І» в цих ПІ реалізує багатоемітерний транзистор у вхідному каскаді.

Традиційні серії ТТЛ 130, 131, 133, 134, 136 155, 530, 555 тощо; вони відрізняються одна від одної швидкодією, споживаною потужністю, навантажувальною здатністю, логічними можливостями і т. п.

ЛЕ функціонує в системі собі подібних ЛЕ. Тому вхідними сигналами для цього ЛЕ є вихідні потенціали попереднього ЛЕ. ТТЛ-елемент працює у позитивній логіці з такими логічними рівнями:

U1 E 5B , U0 UКНE 0,2B .

67

2.3.1 ТТЛ-елемент І-НЕ з простим інвертором

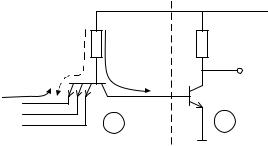

Розглянемо роботу ТТЛ-елемента І НЕ з простим інвертором (рис. 2.12).

Iвх

x1 x2

x2

x3

+E

+E

R1 |

R2 |

IБ1 |

y |

|

IБ1 |

V1 |

V2 |

I |

НЕ |

Рисунок 2.12 – ТТЛ-елемент І НЕ з простим інвертором

Нехай на всі входи подані сигнали логічних «одиниць»:

x1 x2 x3 U1 5B.

При цьому всі незалежні транзисторні структури багатоемітерного транзистора V1 працюють в інверсному режимі, внаслідок чого базовий струм V1 разом із вхідним струмом Iвх перемикається у базу транзистора V2 .

Останній переходить до режиму насичення, і його вихідна

напруга |

Uвих UКНE |

0,2B. |

Відтак |

вихідний сигнал |

ЛЕ |

|

y U0 . |

Якщо ж на один із |

входів |

ЛЕ подати логічний |

|||

«нуль» |

(наприклад, |

x U0 U |

0,2B, у той час |

на |

||

|

|

1 |

|

КНE |

|

|

інших входах діють логічні «одиниці», то відповідна транзисторна структура (наприклад, перша) перейде до режиму насичення (перший емітерний перехід зміститься у прямому напрямі при зворотному зміщенні решти емітерних переходів V1), і базовий струм IБ1 перемикається у

68

вхідне коло (пунктир IБ1 на схемі рисунка 2.12). Транзис-

тор V2 перейде до режиму відсічки, і вихідна напруга

Uвих E 5B , тобто y U1.

Така схема має невисоку навантажувальну здатність, низьку швидкодію і малу завадостійкість. Тому вона не є базовим ЛЕ, а застосовується у складі серій ЦІС як різновид логічного елемента для реалізації схеми з відкритим колектором.

2.3.2 ТТЛ-елемент І–НЕ із складним інвертором

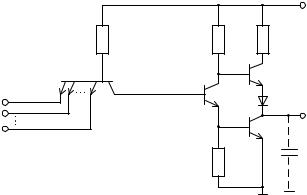

Ці недоліки «знімаються» у схемі рисунка 2.13. Ця схема є базовою для мікропотужної серії 134.

Склад схеми. V1 – багатоемітерний транзистор, який реалізує операцію «І» на вході ЛЕ; V2 , R2 , R3 – фазо-

інверсний каскад; V3 , V4 , R4 , Vg – двотактний вихідний

каскад. Саме фазоінверсний і вихідний каскади утворюють разом схему складного інвертора.

Джерело живлення E 5B.

|

|

+E |

R1 |

R2 |

R4 |

V1 |

|

V3 |

x1 |

V2 |

VD |

x2 |

|

y |

x8 |

|

V4 |

|

R3 |

Cвих |

Рисунок 2.13 – ТТЛ-елемент І НЕ із складним інвертором

69

Принцип дії. Логічний елемент функціонує у пози-

тивній логіці з такими логічними рівнями: U0 0,2B;

U1 3,6B. Нехай на всі ходи подаються логічні «одиниці»:

x1 x2 ... x8 U1 3,6B.

При цьому струм IБ1 перемикається у базу транзис-

тора V2 , який відкривається і переходить до режиму насичення. Зростання струму через V2 приводить до збіль-

шення спадів напруги на опорах R2 і R3. Напруга на колекторі транзистора V2 зменшується, а напруга на емітері

V2 (базі транзистора V4 ) збільшується. Транзистор V4

відкривається, шунтуючи опір R3 і викликаючи подальше зменшення потенціалу колектора транзистора V2 .

Внаслідок цього транзистори V2 і V4 переходять до режиму насичення, тобто

Uвих U UКEH 0,2B, y U0 .

Транзистор V3 закривається, оскільки напруга між колекторами V2 і V4 стає меншою, ніж сумарний поріг відкривання транзистора V3 і зміщувального діода Vg .

Таким чином, основне призначення діода Vg полягає в забезпеченні надійного закривання V3 при насиченні транзисторів V2 і V4 . У цьому стані ЛЕ вихідна паразитна ємність Cвих швидко розряджається через відкритий і насичений транзистор V4 .

При |

надходженні хоча |

б на |

один із |

входів |

ЛЕ |

|

логічного |

«нуля» (x U0 0,2B) |

базовий |

струм |

I |

Б1 |

|

|

1 |

|

|

|

|

|

перемикається у вхідне коло, |

транзистор V2 |

закривається |

||||

|

70 |

|

|

|

|

|