Материал: mikroshemotehnika

Стандартний ряд напруг живлення для ЦІС:

1,2; 1,6; 2,0; 2,4; 3,0; 4,0; 5,0; 6,0; 9,0; 12,6; 27 В.

Для ЦІС на біполярних транзисторах E 4 5B. Для ЦІС на МОН-транзисторах E 5 9B.

7 Допустимий діапазон температур для сучасних напівпровідникових ЦІС 60 125oC (як для кремнієвих напівпровідникових приладів).

2.2 Принципи схемотехніки базових логічних елементів

Унаслідок дворівневого кодування цифрових сигналів найважливішим схемотехнічним елементом в БЛЕ є т. зв.

потенціальні інвертори (ПІ). Основне завдання ПІ є інвертування вхідного потенціалу. Крім того, він є підсилювачем – нормувачем сигналів, що пройшли обробку в логічних схемах.

Схеми ПІ будуються на основі підсилювального каскаду і розрізняються одна від одної схемами керування струмами транзисторів, типом транзисторів, а також навантаженням у колі колектора (стоку). Схеми ПІ на біполярних транзисторах побудовані за принципом перемикання струму з однієї гілки кола на іншу (без зміни величини струму) під дією вхідного сигналу. Залежно від того, в якій гілці кола здійснюється перемикання, розрізняють: перемикачі базового струму, перемикачі емітерного струму.

Крім ПІ на біполярних транзисторах, широко застосовується в ЦІС ПІ на МОН-транзисторах.

Розглянемо принципи будови та функціонування кожного з видів цих потенціальних інверторів окремо.

56

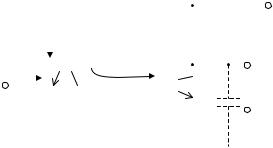

2.2.1 Потенціальні інвертори з перемикання базового струму

Схема (рис. 2.5) розроблена спеціально для інтегральних ТТЛ-елементів, на дискретних елементах вона не застосовується.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IБ1 |

|

|

|

|

|

|

|

R1 |

|

|

|

Rк |

|

|

+E |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Uвх |

Iвх |

|

|

|

|

|

|

|

Iк1 |

|

|

|

|

|

|

|

|

Uвих |

1 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V2 |

|

|

0 |

||||||||

1 |

|

|

|

|

|

|

|

V1 |

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

Cвих |

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 2.5 – Потенціальний інвертор із перемикання базового струму

Склад схеми. V1 – вхідний (керувальний) транзистор

n p n-типу; R1 – |

|

базовий |

опір транзистора |

V1; RK – |

|

колекторний опір транзистора V2 ; V2 – вихідний транзистор |

|||||

n p n-типу. У схемі співвідношення опорів |

RK R1. |

||||

Вхідні і вихідні сигнали набувають таких значень: U1 E , |

|||||

U0 0. |

|

|

|

|

|

Принцип дії |

|

|

|

|

|

1 Нехай на вхід ПІ надходить |

|

||||

|

|

Uвх U1 E. |

|

||

Тоді потенціал емітера транзистора V1 стає вищим від |

|||||

потенціалу бази E |

|

Б |

|

(за рахунок спаду напруги на |

|

V |

V |

|

|

||

|

1 |

|

1 |

|

|

R1), а потенціал колектора V1 (бази V2 ) ще нижче (частки вольтів).

57

Отже, у транзисторі V1 напруга UБЕ 0, UБK 0,

тобто емітерний перехід зміщений зворотно, а колекторний перехід – прямо. Транзистор V1 перебуває в інверсному режимі: колекторний перехід інжектує, емітерний –

екстрагує носії, утворюючи |

IE1 Iвх. |

Джерело |

живлення |

|||||

« E» створює базовий струм IБ1, який протікає по колу |

||||||||

« E»→ R1→ відкритий колекторний перехід V1 → база |

||||||||

V2 → емітер V2 → корпус. Транзистор V2 переходить до |

||||||||

режиму |

|

насичення, |

і |

вихідна |

напруга |

схеми |

||

Uвих UКЕН |

|

0, тобто відповідає логічному «нулю». |

||||||

|

|

V |

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

2 Нехай на вхід ПІ надходить |

|

|

||||||

|

|

|

|

|

Uвх U0 0. |

|

|

|

Тоді потенціал емітера V1 буде нижчим від потенціалу |

||||||||

бази E |

|

Б |

. Емітерний перехід V1 |

зміщується прямо. |

||||

V |

|

V |

|

|

|

|

||

|

1 |

|

|

1 |

|

|

|

|

Обидва переходи транзистора V1 відкриті, і V1 переходить |

||||||||

до режиму насичення. Базовий струм |

IБ1 відгалужується |

|||||||

від колекторного переходу |

V1 до емітерного |

переходу |

||||||

(перемикається до емітерного кола). Внаслідок цього базовий струм IБ2 транзистора V2 різко зменшується, і цей

прилад переходить до режиму відсічки. Вихідна напруга схеми

Uвих U1 E .

Таким чином, інвертування вхідного сигналу в цій схемі здійснюється внаслідок перемикання базового струму IБ1 або до вхідного (емітерного) кола транзистора V1 (при

Uвх U0 ), або до бази транзистора V2 (при Uвх U1). Це, в свою чергу, приводить до вимикання або вмикання транзистора V2 .

58

Недоліки схеми: наявність вхідного струму Iвх при

Uвх U1, що приводить до зменшення рівня високого

потенціалу на вході і відтак обмежує навантажувальну здатність попередньої схеми; порівняно невисока швидкодія (істотний вплив паразитної ємності Cвих ).

Схема рисунка 2.5 – ПІ з перемикання базового струму – застосовується в інтегральних ТТЛ-елементах.

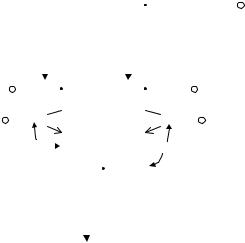

2.2.2 Потенціальні інвертори з перемикання емітерного струму

Схема потенціального інвертора з перемикання емітерного струму є, по суті, диференціальний каскад, що працює у ключовому режимі (рис. 2.6).

|

|

|

|

U1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

U0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U1 |

|

+E |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

Iк1 |

|

|

|

RК |

Iк2 |

|

|

|

RК |

U0 |

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

Uк1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uк2 |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V1 |

|

|

V2 |

|

|

|

|

|

|

|

|

|

|

|||||

U1 |

Uвх |

|

|

|

|

|

+U0n |

|

|

||||||||||||||||||||

UБЕ1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

U0 |

|

|

|

|

|

|

|

|

|

|

|

|

UБЕ2 |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

IE |

|

|

|

RE |

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 2.6 – Потенціальний інвертор із перемикання емітерного струму

59

Склад схеми V1, V2 – пара ідентичних за параметрами транзисторів (V1 – вхідний, V2 – опірний); Uоп – джерело

опірної напруги; RK1 RK2 RK ; RE – спільне для V1 і V2 емітерне навантаження, що забезпечує емітерний зв'язок між V1 і V2 ; Е – джерело живлення.

Принцип дії

1 Нехай до баз V1 і V2 прикладені однакові напруги

Uвх Uоп . Обидва транзистори працюють в активному

режимі, і внаслідок ідентичності плечей диференціального каскаду через них протікають однакові струми:

|

|

IE |

IE |

|

IE |

. |

|

|

||

|

|

2 |

|

|

||||||

|

|

1 |

|

2 |

|

|

|

|

||

В активному режимі |

IK IE |

(IБ 0), |

і вихідні |

|||||||

напруги будуть однакові: |

|

|

|

IE |

|

|

|

|||

U |

K1 |

U |

E |

|

R . |

|

||||

|

|

|||||||||

|

|

K2 |

|

2 |

|

K |

|

|||

Статичні передавальні характеристики UK |

f (Uвх) і |

|||||||||

|

|

|

|

|

|

|

|

|

1 |

|

UK2 f (Uвх) подані |

на |

рисунку 2.7. Описаному стану |

||||||||

схеми відповідає т. А (початковий стан робочої точки). 2 Нехай на вхід поданий сигнал Uвх U1 Uоп .

Процеси в схемі рисунка 2.6 проходитимуть так:

Uвх UБЕ1 IЕ1 IK1 UK1

URE UБЕ2 IЕ2 IK2 UK2 .

Відбувається перерозподіл емітерного струму IE на користь IE1 , внаслідок чого транзистор V1 ще більше

відкривається (залишаючись в активному режимі), а транзистор V2 закривається і переходить до режиму відсічки (точка В на СПХ рисунка 2.7).

60