Материал: mikroshemotehnika

|

|

Uвих |

|

Uзм |

|

Uвих+ |

|

Uс |

VD1 |

0 |

t |

R |

Uвих |

||

U0n |

|

|

—

VD2 Uвих

U1 |

+3…+5 В |

|

|

0 |

t |

||

U0 |

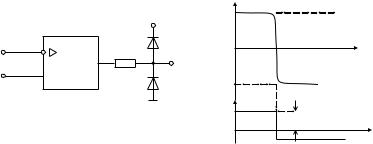

Рисунок 1.33 – Компаратор із цифровим виходом

Фактично, такі інтегральні компаратори – це спеціалізовані ОП із двома входами і поодиноким або парафазним цифровим виходом, який видає сигнал логічного «нуля» або логічної «одиниці» залежно від знака різниці U Uоп Uc.

Як правило, такі компаратори складаються з одного або двох диференціальних підсилювачів, емітерного повторювача, стабілізованого каскаду зсуву рівня і кола обмеження вихідного сигналу. Найпоширеніші інтегральні компаратори – це АІС 521СА1, 521СА2.

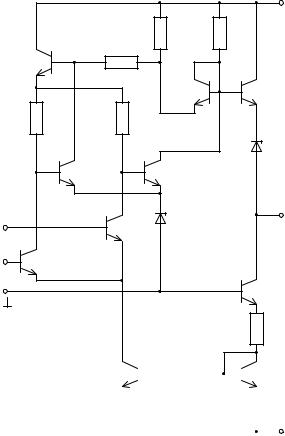

Принципова схема компаратора 521СА2 наведена на рисунку 1.34. Перший диференціальний каскад зібраний на транзисторах V1 і V4 і живиться від ГСС на транзисторі V5 .

R1, R4 – резистори навантаження першого диференціаль-

ного каскаду; R7 , V10 , R8 – коло зміщення ГСС на транзисторі V5 . Транзистор V9 виключає вплив вихідного кола на зміщення ГСС (базу V9 під’єднують безпосередньо до корпусу). Другий диференціальний каскад зібраний на транзисторах V3 , V6 з резисторами навантаження R2 , R3 і

R6. Стабілітрон Vст1 має опірну напругу +6,2 В і фіксує потенціал баз V3 і V6 на рівні приблизно +6,9 В.

46

|

|

+E |

V2 |

R3 |

R6 |

R2 |

|

|

|

V7 |

V8 |

R1 |

R4 |

|

|

|

Vст2 |

V3 |

V6 |

|

Вх1 |

Vст1 |

Вих |

|

||

|

V4 |

|

Вх2 |

|

|

V1 |

|

|

|

|

V9 |

|

|

R7 |

|

V5 |

|

|

|

|

|

|

|

V10 |

||

|

|

|

|

|

|

|||

|

|

R5 |

|

|

|

R8 |

||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

—E

Рисунок 1.34 – Спеціалізований інтегральний компаратор

Тому допустимий сигнал на входах компаратора може наближатися до 7 В. Напруга з виходу другого диференціального каскаду надходить на емітерний повторювач на транзисторі V8 , який забезпечує необхідну

навантажувальну здатність. Стабілітрон Vст2 в емітерному колі V8 зсуває рівень вихідного сигналу «вниз» на 6,2 В,

щоб узгодити його з входами цифрових ТТЛ-схем.

47

Транзистор у діодному режимі V7 обмежує розмах вихідного сигналу в позитивній області (при Uвих 4B

транзистор V7 відкривається і замикає накоротко

диференціальний вихід другого каскаду). Таким чином, вихідна напруга не може зменшитися нижче рівня0,7... 0,8B (напруги на прямозміщеному колекторному

переході транзистора V9 у режимі насичення) і перевищити

+4 В (за рахунок дії транзистора V7 ). Тому вихідні рівні

напруг компаратора (U0 1...0B, |

U1 2,4... |

4B) |

цілком сумісні з ТТЛ-схемами. |

|

|

48

2 Схемотехніка цифрових інтегральних мікросхем

2.1 Загальна характеристика інтегральних логічних елементів

Цифрові інтегральні схеми (ЦІС) – це такі інтегральні схеми, за допомогою яких перетворюються і обробляються дискретні сигнали, виражені у двійковому або іншому цифровому коді, і які призначені для роботи в різноманітних електронних вузлах і системах.

До ЦІС належать логічні елементи, тригери, регістри, суматори, лічильники, шифратори, дешифратори, арифме- тико-логічні пристрої, АЦП, ЦАП, різні схеми пам`яті тощо.

Логічні елементи, як відомо, реалізують такі логічні операції:

–логічне заперечення (інверсія, операція НЕ);

–логічне множення (кон’юнкція, операція І);

–логічне додавання (диз’юнкція, операція АБО);

– операція І НЕ y x1 x2 ... xn ;

– операція АБО НЕ y x1 x2 ... xn .

Із цих елементів саме елементи І НЕ та АБО НЕ є базовим: в алгебрі логіки доведено, що для побудови цифрових систем будь-якої складності достатньо мати в наборі лише однотипні елементи І НЕ або АБО НЕ. А тому для цифрової мікросхемотехніки найбільш важливим і першочерговим є знання принципів побудови і функціонування саме базових логічних елементів (БЛЕ). Це знання дозволяє потім засвоїти й більш функціонально складні ЦІС. Електричні параметри БЛЕ визначають характеристики практично всіх ЦІС, що входять до складу спільної з цим базовим елементом серії.

49

Класифікація інтегральних логічних елементів

За видом логічної операції, що реалізується в них,

розрізняють:

– ІЛЕ одноступеневої логіки (НЕ, І, АБО, І НЕ,

АБО НЕ );

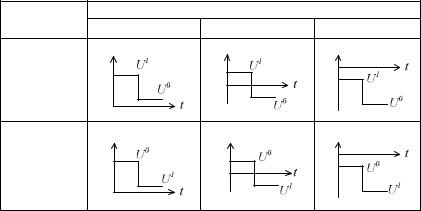

– ІЛЕ двоступеневої логіки (І АБО,І АБО НЕ). За способом подання цифрових сигналів ІЛЕ

поділяються на:

–потенціальні, в яких значення логічних 0 і 1 подані двома рівнями електричного потенціалу – низьким і високим;

–імпульсні, в яких значення 0 і 1 свідчать про відсутність і наявність імпульсів певної тривалості і амплітуди.

За типом елементів, з яких побудовані ІЛЕ, розрізняють: логічні елементи транзисторно-транзисторної логіки (ТТЛ), логічні елементи емітерно-зв’язаної логіки (ЕЗЛ), логічні елементи на МОН (КМОН)-структурах, логічні

елементи інтегральної інжекційної логіки (I2 ). |

|

|||

Потенціальні логічні елементи функціонують за |

||||

позитивною і негативною логікою (табл. 2.1). |

|

|||

Таблиця 2.1 |

Полярність напруги джерела живлення |

|||

Вид логіки |

||||

+ |

два джерела |

– |

||

|

||||

Позитивна |

|

|

|

|

Негативна |

|

|

|

|

|

|

50 |

|

|