Материал: m013800e

Peak Time Counter 750-404/000-002

Technical data

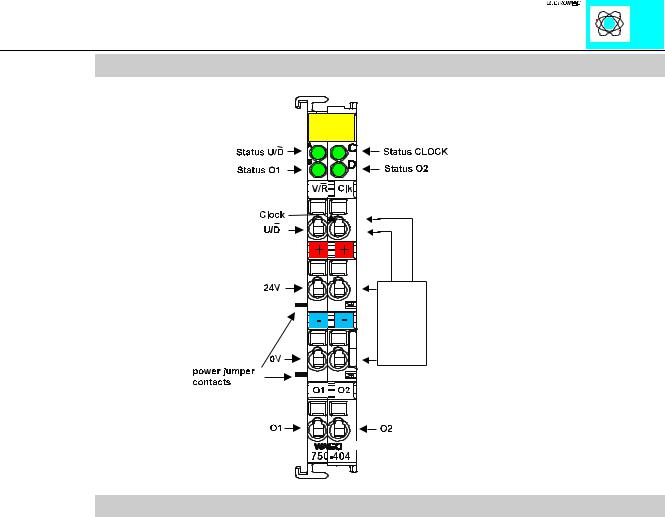

The counter module also can be ordered as peak time counter with 750-404/000-002.

This description is only intended for hardware version X X X X 0 0 0 1- - - -. The serial number can be found on the right side of the module.

The counter begins processing with pulses at the CLOCK input. The changes from 0 V to 24 V are counted.

The counter counts up if the input U/D is set at 24 V. With an open circuit input or 0 V the counter counts backwards.

The two bottom contacts each include another output. These outputs are activated through bits in the control byte.

The counter module is able to run with all WAGOÇI/OÇSYSTEM bus-couplers (except for the economy type).

Counter Module 750-404 |

6 |

|

:$*2 , 2 6<67(0 |

Organization of the inand output data:

The counter begins processing with pulses at the CLOCK input for a special time span. The time span is predefined as 10 s. The state of the counter is stored in the processs image until the next period. After the recording the counting starts again at 0.

The activation of the counting and the synchronisation with the SPS is made by a handshake in the control and status byte.

The end of thre counting period and thus the new process data is signaled by a toggel bit in the status byte.

The control byte has the following bits:

Control Byte

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

|

|

|

|

|

|

|

|

0 |

0 |

start of the |

0 |

Output value at |

Output value at |

0 |

0 |

|

|

periodic |

|

output O2 |

output O1 |

|

|

|

|

counting |

|

|

|

|

|

|

|

|

|

|

|

|

|

The status byte has the following bits:

Status Byte

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

|

|

|

|

|

|

|

|

0 |

0 |

counting |

0 |

actual signal at |

actual signal |

actual signal at |

Toggelbit for |

|

|

started |

|

O2 |

at O1 |

input U/D |

end of the |

|

|

|

|

|

|

|

record |

|

|

|

|

|

|

|

|

Counter Module 750-404 |

7 |

|

:$*2 , 2 6<67(0 |

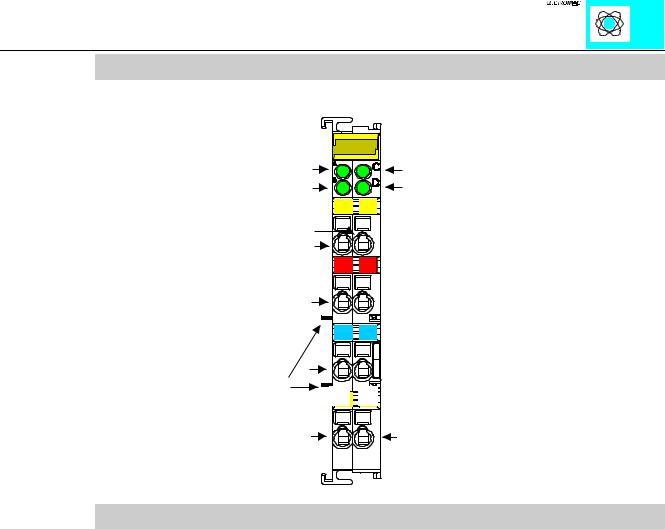

Frequency Counter Module, 750-404/000-003

Status Gate |

|

Status CLOCK |

Q1 |

|

Q2 |

O1 |

|

O2 |

|

G |

+E2Clk |

Clock |

|

|

Gate |

+ |

+ |

|

||

|

24V |

24V |

24V |

|

|

|

- |

- |

|

0V |

0V |

0V |

|

|

power jumper |

O1 |

O2 |

|

Q1 |

Q2 |

contacts |

S |

S |

|

|

|

O1 |

|

O2 |

Q1 |

|

Q2 |

750-404

000-003

Technical Description

The counter module 750-404/000-003 measures the period of the 24 V DC input signal at the CLOCK terminal and converts it into a corresponding frequency value. The measurement is enabled if the GATE terminal is an open circuit input or 0V. To disable processing, the GATE input is to be set to 24 V DC.

The terminals O1 and O2 work as binary outputs. Each output can be activated via specific bits in the CONTROL byte.

The high states of the input and output channels are each indicated by a LED.

To recognize low frequency or near zero frequency signals, the maximum time between two data updates is parameterizable.

Counter Module 750-404 |

8 |

|

:$*2 , 2 6<67(0 |

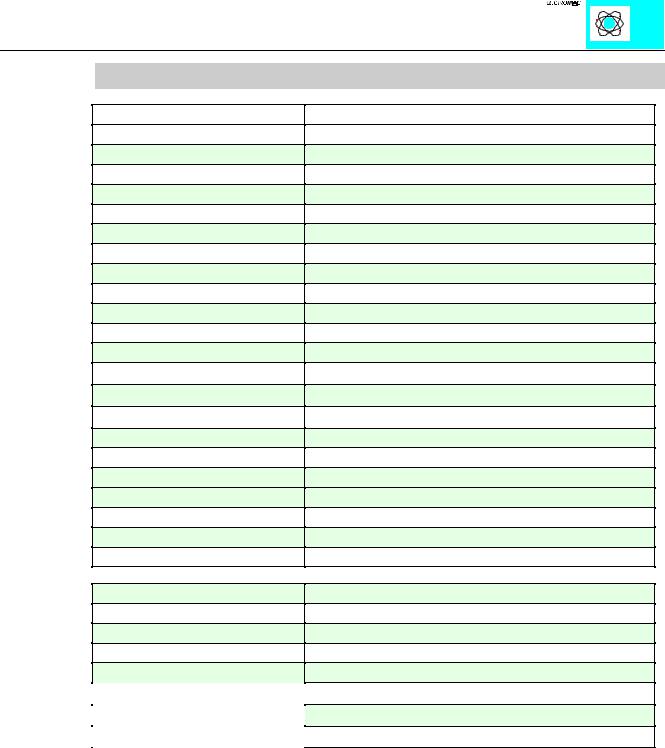

Technical Data:

Item-No.: 750-

Supply Voltage

Input Voltage (low)

Input Voltage (high)

Input Current

Min. Pulse Width

Output Current

Voltage Drop

Frequency Range:

Integration time = 1 period

Integration time = 4 periods

Integration time = 16 periods

Measuring Error:

Range 0.1 - 100 Hz

Range 1 - 1000Hz

Range 10 - 10000Hz

Data Format:

Process Image

Internal Bit Width

Input Current (internal)

Operating Temperature

Wire Connection

Size (mm) WxHxD

Frequency Range:

Integration time = 1 period

Integration time = 4 periods

Integration time = 16 periods

Measuring Error:

Range |

0.1 |

- |

8000Hz |

Range |

0.25 - |

32000Hz |

|

Range |

1 |

- |

100000Hz |

404/000-003

24V DC (-15%/+20%)

-3V - 5V DC

15V - 30V DC

5mA typ. at 24V DC

10µs

0.5A (short circuit protection)

0.6V DC max. at 0.5A

0.1 - 100Hz, Resolution 0.001Hz

1 - 1,000Hz, Resolution 0.01Hz

10 - 10,000Hz, Resolution 0.1Hz (1Hz)

<± 0.05%

<± 0.05 %

<± 0.2 %

5 Byte Inand Output

8 Bit CONTROL/STATUS + 32 Bit DATA

80mA max. at 5V DC

0°C....+55°C

CAGE CLAMP; 0.08 to 2.5mm2

12 x 64* x 100 (*from upper edge of carrier rail)

0.1 - 8,000Hz, Resolution 0.001Hz

0.25 - 32,000Hz, Resolution 0.01Hz

1- 100,000Hz, Resolution 0.1Hz (1Hz)

<± 1%

<± 1.5 %

<± 1.5 %

Counter Module 750-404 |

9 |

|

:$*2 , 2 6<67(0 |

Functional description

The counter module acquires the time between one or more rising edges of the CLOCK input signal and calculates the frequency of the applied signal.

The calculation and process image update are initiated every 1st, every 4th or every 16th rising edge depending on the integration time selected via the CONTROL byte. The first detection of a rising edge starts the cyclic period measurement and cannot provide a valid frequency value. In this case the module will send 0xFFFFFFFFH for input information. The same input value is returned when a static high or static low signal is applied to the CLOCK input.

If there are no signal changes seen at the CLOCK input, the module can be forced to update the process image after defined parameterizable time spans. In this state the module will send the non valid value 0xFFFFFFFFH too.

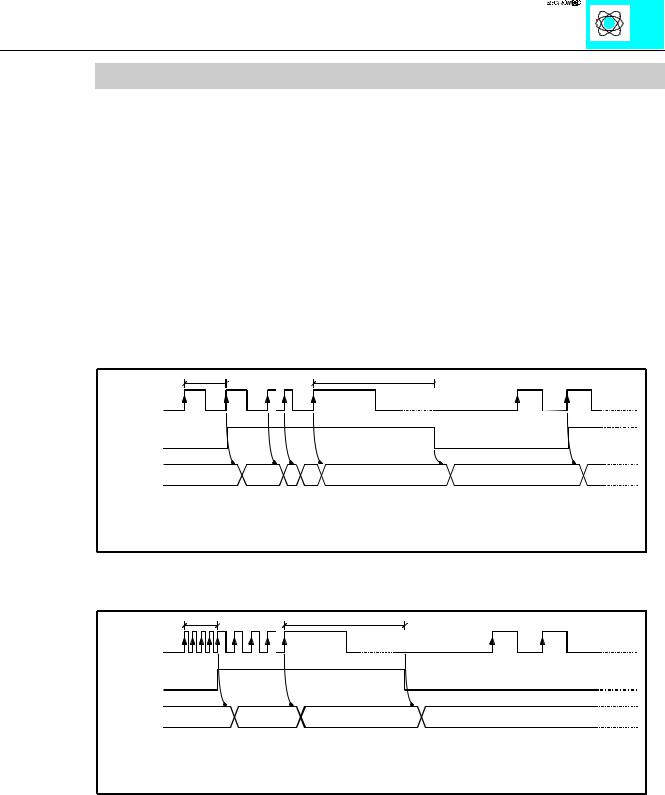

The following figures illustrate a process data cycle.

|

|

73 |

|

7 |

|

|

,1387 )5(4 |

|

|

|

|

|

|

'$7$ 9$/,' |

|

|

|

|

|

|

352&(66 '$7$ |

[)))))))) |

' ' |

' ' |

[)))))))) |

' ' |

|

|

|

|

|

|

|

|

|

|

|

' ' ' ' |

|

|

|

' ' |

,QSXW 'DWD |

|

|

|

|

|

73 |

I |

FXUUHQW SHULRG |

|

|

|

|

7 |

|

0D[LPXP GDWD KROG WLPH SDUDPHWHUL]DEOH |

|

|

||

Figure 2: Timing diagram for process data update sequence |

|

|||||

(integration time = 1 period) |

|

|

|

|||

|

|

7 |

|

|

|

|

,1387 )5(4 |

|

|

|

|

|

|

'$7$ 9$/,' |

|

|

|

|

|

|

352&(66 '$7$ |

[)))))))) |

' ' |

' ' |

[)))))))) |

|

|

' ' |

,QSXW 'DWD |

|

|

|

|

|

73 |

I |

FXUUHQW SHULRG |

|

|

|

|

7 |

|

0D[LPXP GDWD KROG WLPH SDUDPHWHUL]DEOH |

|

|

||

Figure 3: Timing diagram for process data update sequence (integration time = 4 periods)

Counter Module 750-404 |

10 |

|

:$*2 , 2 6<67(0 |