Материал: Tverdotila_elektronika

2 За функціональними призначеннями:

-

аналогові (АІС);

-

цифрові (ЦІС).

3

За ступенем інтеграції, який оцінюється

показником

![]() ,

де

,

де

![]() –

число елементів і компонентів у складі

ІС:

–

число елементів і компонентів у складі

ІС:

-

малої інтеграції:

Ne

≤ 10,

![]() ,

,

10<Ne≤100,

![]() ;

;

-

середньої інтеграції:

100<Ne≤1000,

![]() ;

;

-

великі інтегральні схеми (ВІС):

1000<Ne≤10000,

![]() ;

;

-

надвеликі інтегральні схеми (НВІС): 10000<Ne≤100000,

.

.

4 За функціональними можливостями:

-

універсальні;

-

спеціалізовані.

5 За типом основного активного елемента:

-

ІС на біполярних транзисторах;

-

ІС на уніполярних транзисторах (МДН, КМДН).

6 За конструктивним виконанням:

-

корпусні;

-

без корпусні.

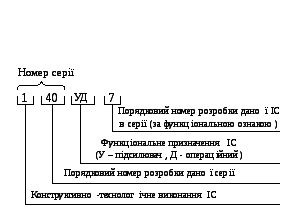

Система умовних позначень інтегральних схем

Упроваджена на підставі ГОСТ 17021-75.

1-й елемент: 1, 5, 6, 7 – напівпровідникові ІС;

2, 4, 8 - гібридні ІС;

3 - інші (плівкові, вакуумні).

3-й елемент: ЛА – логічний елемент І – НЕ; ЕН – стабілізатор напруги; ТВ – JК тригер; ТМ – D-тригер; ТМ D-тригер; ТР – RS-тригер; ІP – регістр; ІE – лічильник; СА – компаратор; ПВ – АЦП; ПА – ЦАП; УВ – підсилювач ВЧ; УР – підсилювач проміжної частоти; УН – підсилювач НЧ; УВ – відеопідсилювач; УЕ – емітерний повторювач; ФВ – фільтр ВЧ; ФН – фільтр НЧ; ГС – генератор синусоїдних сигналів.

7.2 Гібридні інтегральні схеми

Основою мікроелектроніки є метод інтеграції (об'єднання) елементів. При цьому сукупність елементів ІС і міжз'єднань виготовляється в єдиному технологічному процесі – одержують закінчений функціональний вузол. Автономно або разом із додатковими елементами цей вузол власне утворює інтегральну схему.

Застосовуються дві основні технології виготовлення ІС – гібридна і напівпровідникова.

До технології виготовлення ІС ставлять 2 суперечливі вимоги:

1 Підвищений ступінь інтеграції (щільності упакування).

2 Необхідно мати універсальні ІС.

Втім, збільшення ступеня інтеграції ІС обмежує сферу її застосування, тобто призводить до зниження універсальності схеми.

Наявність двох технологій – гібридної і напівпровідникової – дещо розв'язує цю суперечність. Максимальну цільність упакування дає напівпровідникова технологія, проте вона є складною, і властивості елементів, виготовлених за нею, не завжди задовольняють вимоги ТУ (наприклад, розкид параметрів і т.п.) Гібридна технологія є більш економною і пристосованою до спеціальних прецизійних пристроїв, дозволяє одержати ІС із кращими властивостями, хоча при цьому з низьким ступенем інтеграції.

Варто пам'ятати, що, крім напівпровідникових і гібридних ІС, існують ще й плівкові ІС. Плівкова ІС – це така, у якої елементи і міжз'єднання виготовляються з плівок необхідної форми з різними електрофізичними властивостями і розміщуються на поверхні діелектричної підкладки або діелектричної плівки. Однак плівкова технологія не дозволяє виготовляти активні елементи із задовільними параметрами. Відтак чисто плівкові ІС – це пасивні схеми (переважно резистивні розподільники напруги, набір резисторів і конденсаторів, резистивно-ємнісні схеми). Тому всі переваги плівкової технології застосовуються у високопрецизійних гібридних ІС.

Гібридна технологія полягає у наступному (рис. 7.2). На відшліфовану діелектричну підкладку (скло, кераміка) за допомогою масок наносяться плівки резистивних і провідникових матеріалів, а також контактні площадки. Активні елементи за плівковою технологією, як уже зазначалося, не виготовляються, а виробляються окремо, у безкорпусному виконанні, а потім підпаюються. Підкладка розрізається на окремі ІС, які вкладаються до корпусів і приєднуються до контактних площадок виводів. Корпуси герметизуються і маркуються.

Розрізняють два різновиди гібридних ІС:

-

товстоплівкові, у яких товщина нанесених плівок ∆>10 мкм;

-

тонкоплівкові, у яких ∆≤1-2 мкм.

Нанесення резистивних і провідникових плівок здійснюється через випарювання у вакуумі різноманітних матеріалів за допомогою трафаретів: ніхрому, двоокису олова і т.д. Плівкові резистори мають значно більший діапазон номінальних значень і менший розкид параметрів порівняно з дифузійними резисторами (виготовленими за напівпровідниковою технологією).

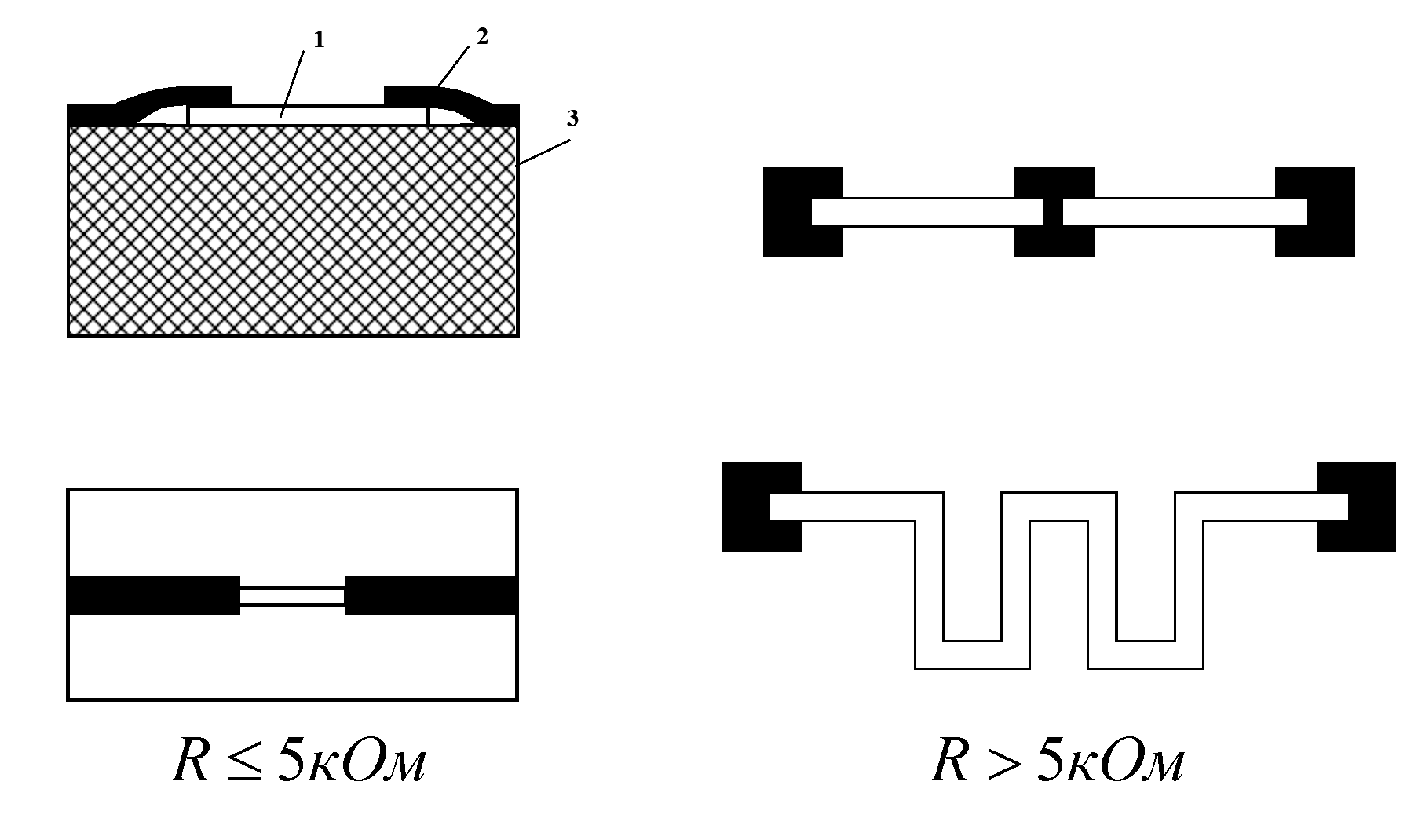

Рисунок 7.5 – Плівкові резистори:

1 – резистивна плівка (ніхром);

2 – провідникова плівка (алюміній);

3 – діелектрична підкладка

Опір плівкового резистора залежить від товщини і ширини плівки, її довжини і матеріалу. Для створення більших опорів застосовуються з'єднання кількох плівок, резистори зигзагоподібної форми тощо.

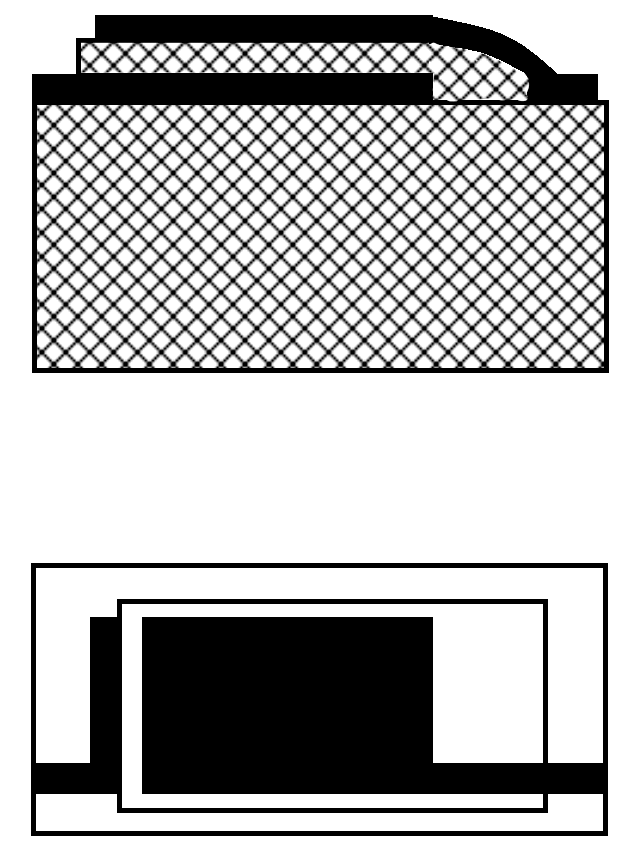

Плівкові конденсатори створюються шляхом почергового нанесення на діелектричну підкладку провідникових і діелектричних плівок (рис. 7.6).

С

≤104

пФ 5%

С

≤104

пФ 5%

Рисунок 7.6 – Плівковий конденсатор

Плівкова технологія дозволяє виконувати також індуктивності (у тому числі й трансформатори) у вигляді плоских спіралей прямокутної форми (рис. 7.7). На площі, яка не перевищує 25 мм², можна одержати індуктивність L ≤ 0,5 мкГн. Наноситься також феромагнітна плівка для формування осердя.

Рисунок 7.7 – Плівкова котушка індуктивності

7.3 Напівпровідникові інтегральні схеми

7.3.1 Технологія

Напівпровідникова (монолітна, твердотіла) технологія більш придатна для масового виробництва ІС з високим ступенем інтеграції, характеристики яких не критичні щодо розкиду параметрів пасивних елементів, їх температурної нестабільності і впливу паразитних зв'язків. За напівпровідниковою технологією виготовляється більшість цифрових інтегральних схем і багатофункціональних аналогових ІС. Надійність напівпровідникових мікросхем значно вища, ніж у гібридних ІС, внаслідок невеликої кількості припаювань.

Усі елементи напівпровідникових ІС виконані всередині напівпровідникового кристала – чіпа. Товщина чіпа – 200-300 мкм, горизонтальні розміри – від 1,5 х 1,5 мм до 6,0 х 6,0 мм.

Планарно-дифузійна технологія виготовлення біполярних напівпровідникових інтегральних схем

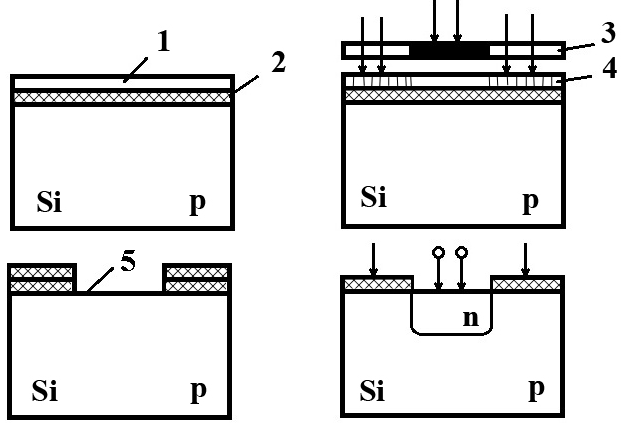

На кремнієвому кристалі (рис. 7.8) створюється тонкий шар двоокису SiO2. На нього наноситься шар 1 фоторезиста. Це речовина, яка під дією опромінення стає кислотостійкою. Фоторезист опромінюється ультрафіолетовими променями через фотошаблон 3 (фотопластинка з відповідним рисунком із прозорих і непрозорих ділянок). Опромінені ділянки 5 витравлюються кислотою. Цей процес називається фотолітографією. На ділянках 5 утворюються вікна, через які здійснюється процес дифузії донорних атомів із нагрітого газу 6.

Рисунок 7.8 – Технологія виготовлення біполярних структур ІС

Таким чином, у кремнієвому кристалі формуються n – області (так звані «кишені»), які відповідають емітерам усієї сукупності біполярних транзисторів цієї ІС. При повторенні операцій послідовно формуються області бази, потім колектора. Паралельно формуються пасивні елементи, а на поверхні кристала – міжз'єднання і контактні площадки.

Ця планарно-дифузійна технологія має такі недоліки:

-

нерівномірний розподіл домішок у областях;

-

нерівномірний опір колектора і збільшення його значення;

-

відсутні чіткі межі переходів, що призводить до зменшення напруги пробою між колектором і підкладкою;

-

підкладка дуже впливає на електричні параметри транзистора ІС.

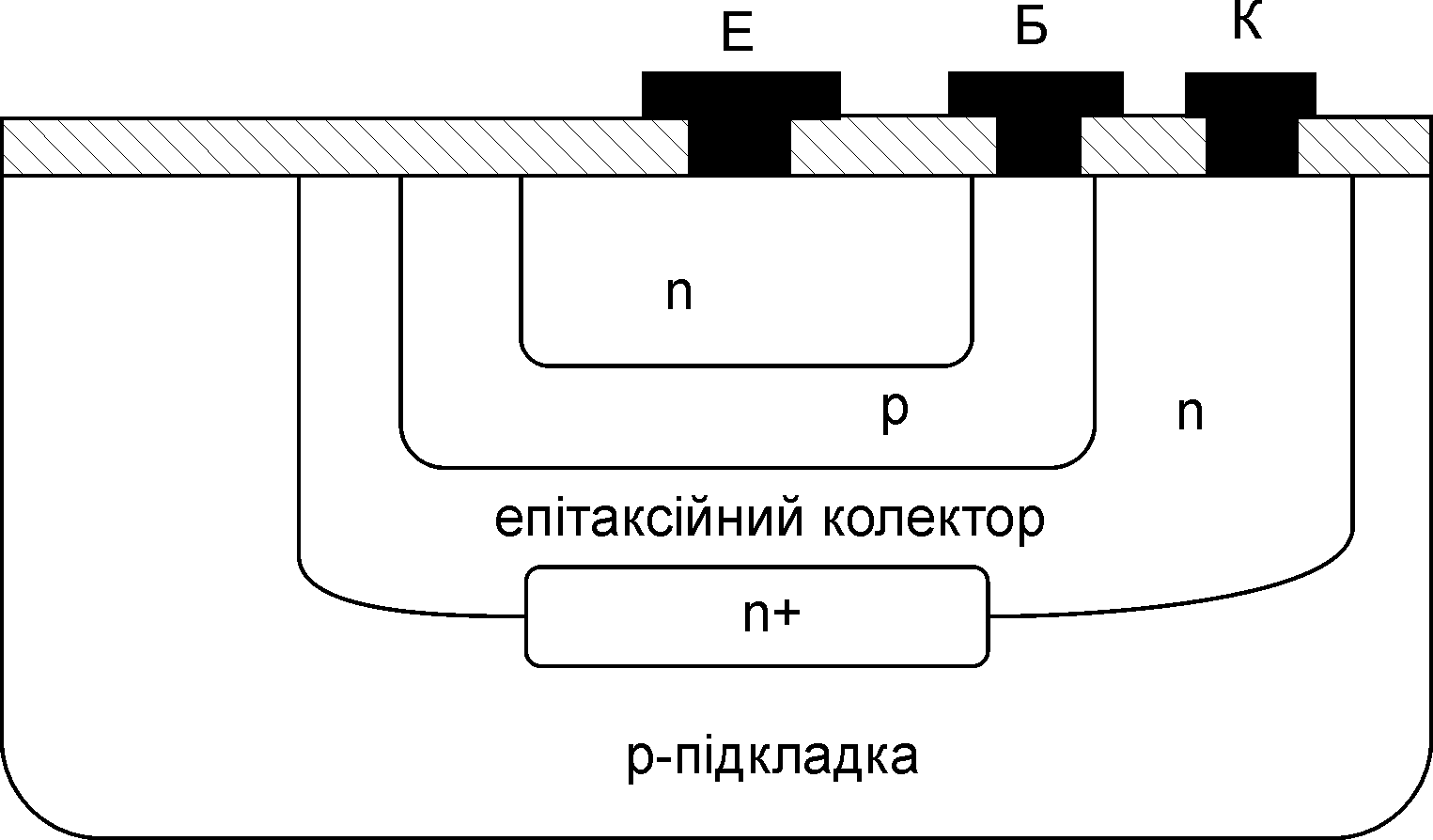

Натомість біполярні інтегральні транзистори, виготовлені за планарно-епітаксійною технологією, відзначаються рівномірним розподілом домішок (рис. 7.9).

Рисунок 7.9 – Планарно-епітаксійна біполярна структура

У них на p-підкладці вирощується колектор n - типу. Для зменшення опору колектора, а отже, зниження втрат потужності і ступеня впливу підкладки створюють прихований n+- шар, який має менший порівняно з епітаксійним n - шаром опір. Цей прихований шар створюється за допомогою додаткової дифузії донорних домішок у відповідні ділянки підкладки.

7.3.2 Технологія виготовлення інтегральних

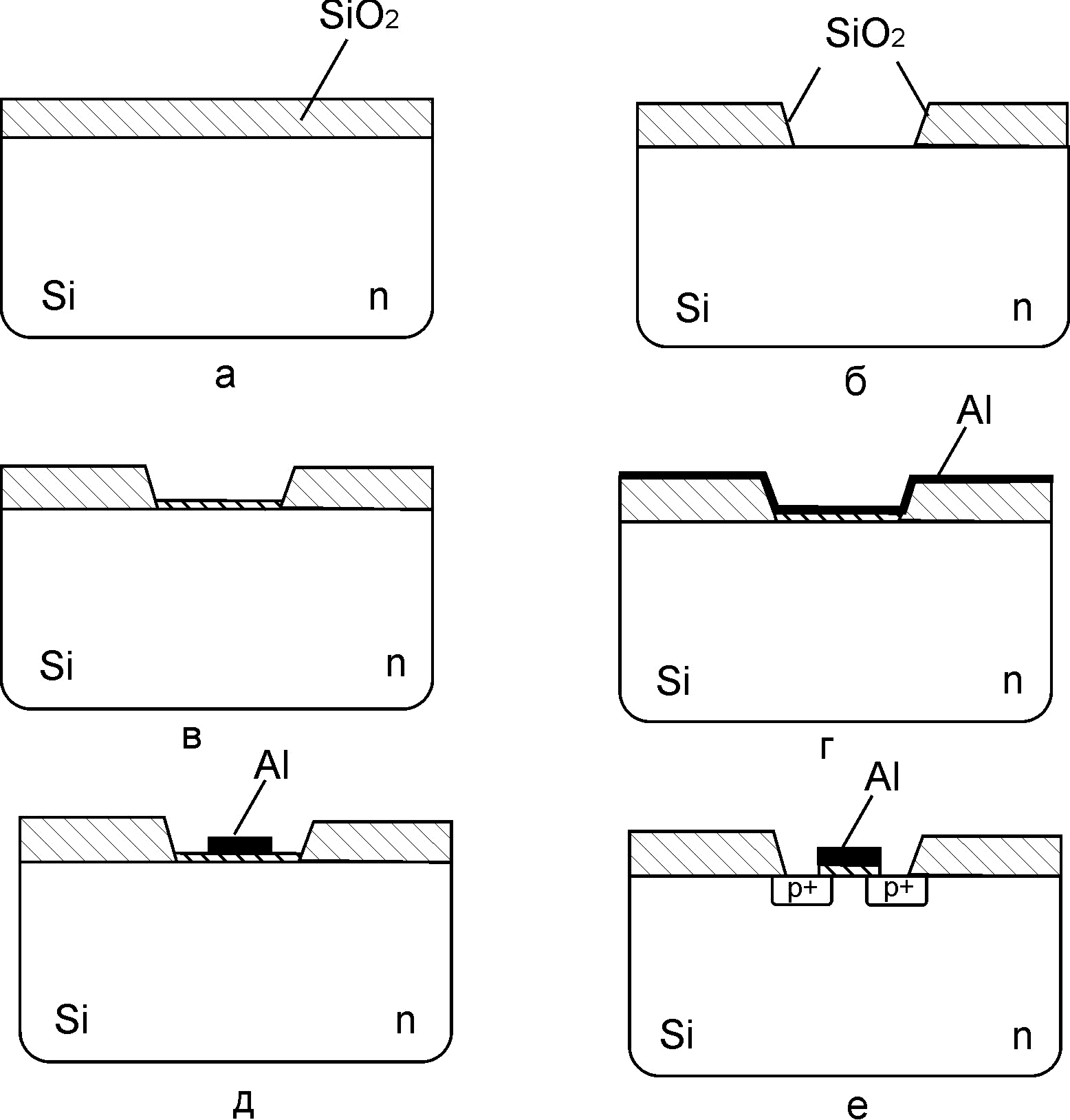

МДН- структур

Послідовність операцій цієї технології показана на рис. 7.10. Виконується товстий (до 1,5 мкм) шар окису кремнію SiO2 (а); за допомогою фотолітографії витравляється «вікно» (б); це вікно покривається тонким шаром SiO2 (0,2 мкм) (в); потім уся пластина покривається шаром матеріалу затвора (алюміній, хром, молібден) (г); за допомогою фотолітографії залишається шар металу тільки над тією областю, де буде затвор (д); шляхом дифузії та іонного легування створюються p+- області витоку і стоку (причому електрод затвора служить маскою) (е).

Рисунок 7.10 – Технологія виготовлення МОН (МДН) - структур