Материал: Analochifr_i_chifroanalog_preobrazovat

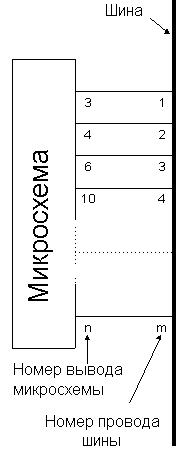

(ША) и шину управления (ШУ). Шины на схеме показываются жирной линией, подключение микросхем и блоков к шинам – по аналогии с рисунком 4.3.

К шине данных подключаются выходы данных АПВ, входы данных ЦАП, информационные выходы ОЗУ и ПЗУ, информационные выводы микросхемы микропроцессора. К шине адреса подключаются адресные выводы микросхемы микропроцессора, адресные выходы ОЗУ и ПЗУ, входы перевода выходов микросхем буферного регистра БМП, ОЗУ и ПЗУ в третье состояние. К шине управления подключаются выходы устройства управления, а также управляющие входы микросхем БМП.

АЦП подключается к шине данных через буферный регистр, имеющий третье состояние выходов. Микросхему (или несколько микросхем, что зависит от рассчитанной разрядности устройства) буферного регистра необходимо выбрать по справочной литературе (например [3, 4]) и выходы схемы АЦП подключить к ее входам. Тактовый вход буферного регистра подключается к соответствующему выходу БУ, а вход, переводящий выходы буферного регистра в третье состояние, – через шину адреса к одному из незадействованных адресных выходов микропроцессора.

Рисунок 4.3 – Подключение микросхем к шинам

Информационные входы входного регистра ЦАП подключаются к шине данных непосредственно. Тактовый вход регистра подключается через шину адреса к одному из незадействованных адресных выходов микропроцессора (можно к тому же, к которому подключен буферный регистр АЦП, но так, чтобы в один и тот же момент времени на подключенные к нему входы регистров АЦП и ЦАП, если они не являются инверсными по отношению друг к другу, подавались инверсные сигналы).

ПРИЛОЖЕНИЕ (справочное)

МИКРОСХЕМЫ АЦП И ЦАП

Микросхема К572ПА1 Микросхемы К572ПА2 и КР572ПА2

Микросхема К594ПА1

Микросхема К1108ПА1 Микросхема К1118ПА1 Микросхема К1118ПА3

Микросхема К1118ПА2 Микросхемы АЦП К572ПВ1 и КР572ПВ1 Микросхема К1107ПВ1 Микросхема К1107ПВ2 Микросхема К1107ПВЗ Микросхема К1107ПВ4 Микросхема КР1107ПВ5 Микросхема К1108ПВ1 Микросхема К1108ПВ2 Микросхема АЦП К1113ПВ1 Микросхемы К572ПВ2 и КР572ПВ2 Микросхема КР572ПВ5

Микросхема К572ПА1

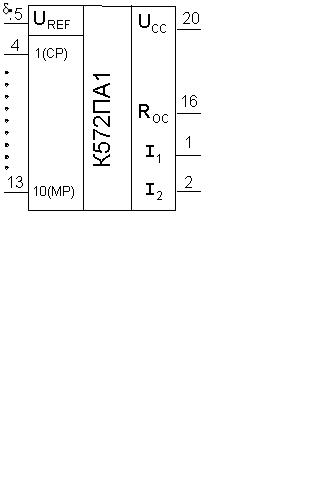

Микросхема умножающего ЦАП типа К572ПА1 (А, Б, В, Г) (рисунок 1) является универсальным структурным звеном для построения микроэлектронных ЦАП, АЦП и управляемых кодом делителей тока.

Благодаря малой потребляемой мощности, достаточно высокому быстродействию, возможности реализации полного двух- и четырехквадратного умножения, небольшим габаритам ЦАП К572ПА1 находит широкое применение в различной аппаратуре.

|

Микросхема ЦАП К572ПА1 предназначена для преобразования 10- |

|

разрядного прямого параллельного двоичного кода на цифровых |

|

входах в ток на аналоговом выходе, который пропорционален |

|

значениям кода и опорного напряжения. Для работы в режиме с |

|

выходом по напряжению к ИС ЦАП К572ПА1 подключатся внешний |

|

ИОН и операционный усилитель (ОУ) с целью создания |

Рисунок 1 – Микросхема |

отрицательной обратной связи (ЦОС), работающей в режиме |

К572ПА1 |

суммирования токов. |

|

Нумерация и назначение выводов микросхемы: 1 – аналоговый выход 1; 2

– аналоговый выход 2; 3 – общий вывод; 4 – цифровой вход 1 (СР); 5 – 12 – цифровые входы 2 – 9; 13 – цифровой вход 10 (МР); 14 – напряжение

источника питания; 15 – опорное напряжение; 16 – вывод резистора обратной связи.

Основные электрические параметры:

|

|

Не менее |

Не более |

– число разрядов b |

10 |

– |

|

– дифференциальная нелинейность |

|

LD, %: |

|

|

|

||

К572ПА1А |

-0,1 |

0,1 |

|

К572ПА1Б |

-0,2 |

0,2 |

|

К572ПА1В |

-0,4 |

0,4 |

|

К572ПА1Г |

-0,8 |

0,8 |

||

– время установления выходного тока tsI, мкс |

– |

5 |

||

– выходной ток смещения нуля I00, нА |

– |

100 |

||

– абсолютная погрешность преобразования в |

-30 |

30 |

||

конечной точке шкалы |

|

Fa, МР |

||

|

||||

– ток потребления ICC, мА |

– |

2 |

||

Точность ЦАП определяется значением абсолютной погрешности прибора, нелинейностью и дифференциальной нелинейностью. Абсолютная погрешность представляет отклонение значения выходного напряжения (тока) от номинального расчетного, соответствующего конечной точке характеристики преобразования. Абсолютная погрешность обычно измеряется в единицах младшего значащего разряда (МР). Нелинейность прибора δ L характеризуется идентичность минимальных приращений выходного сигнала во всем диапазоне преобразования и определяется как наибольшее отклонение выходного сигнала от прямой линии абсолютной точности, проведенной через ноль и точку максимального значения выходного сигнала.

Дифференциальная нелинейность δ LD характеризует идентичность соседних приращений сигнала. Ее определяют как минимальную разность погрешности нелинейности двух соседних квантов в выходном сигнале.

Время установления – это интервал времени от подачи входного кода до вхождения выходного сигнала в заданные пределы. Максимальная частота преобразования – это наибольшая частота дискретизации, при которой параметр ЦАП соответствует заданному значению.

Нормы на электрические параметры данной интегральной схемы (ИС) и возможность ее согласования с КМОП цифровой ИС обеспечиваются при напряжении источника питания 15 В ± 10 % и опорном напряжении 10,24 В. Для работы ЦАП с ТТЛ схемами требуются дополнительные резисторы согласования уровней. Непосредственное согласование ЦАП с ТТЛ цифровыми ИС возможно при питании от источника 5 В ± 10%. Однако электрические параметры в этом случае ухудшаются. Преобразователь К572ПА1 допускает работу при напряжении питания в диапазоне от 5 до 7 В и изменении опорного напряжения в пределах

± 17 В без гарантии норм на параметры.

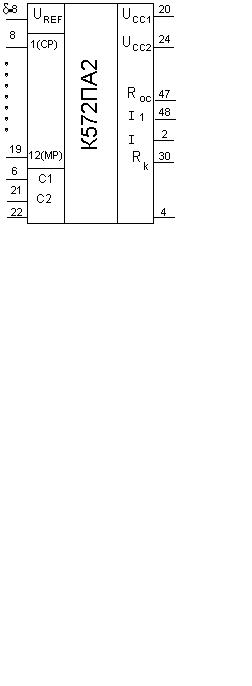

Микросхемы К572ПА2 и КР572ПА2

Микросхемы умножающего ЦАП К572ПА2 (А, Б, В) (рисунок 2) или КР572ПА2 (А, Б, В), как и ИС К572ПА1, являются универсальными структурными звеньями для построения микроэлектронных ЦАП, АЦП и управляемых цифровым кодом делителей тока. Они предназначены для преобразования 12-разрядного прямого двоичного кода на цифровых входах в ток на аналоговом выходе, который пропорционален значениям кода и (или) опорного напряжения.

Рисунок 2 – Микросхема К572ПА2

Нумерация и назначение выводов (для ИС КР572ПА2 в скобках): 2(32) – аналоговый выход 2; 4(33) – аналоговая земля; 6(34) – вход регистра 1; 8(35)

– 19(6) – цифровые входы 1 – 12; 21(8) – вход регистра 2; 22(9) – цифровая земля; 24(10) – напряжение источника питания U СС2; 30(13) – вывод конечного резистора матрицы; 38(27) – опорное напряжение U REF; 47(28) – вывод резистора обратной связи; 48(31) – аналоговый выход 1; 1, 3, 5, 7, 23, 25 – 29, 31 – 37, 39 – 46 – незадействованные выводы.

Основные электрические параметры: |

|

|

||||

|

|

|

|

|

Не менее |

Не более |

– число разрядов b |

12 |

– |

||||

– дифференциальная нелинейность |

|

LD, %: |

-0,025 |

0,025 |

||

|

||||||

К572ПА2А (КР572ПА2А) |

||||||

К572ПА2Б (КР572ПА2Б) |

-0,05 |

0,05 |

||||

К572ПА2В (КР572ПА2В) |

-0,1 |

0,1 |

||||

– время установления выходного тока tsI, мкс |

– |

15 |

||||

– выходной ток смещения нуля I00, нА |

– |

30 |

||||

– абсолютная погрешность преобразования в |

-20 |

20 |

||||

конечной точке шкалы |

|

Fa, МР |

||||

|

||||||

– ток потребления ICC1, ICC2, мА |

– |

2 |

||||

Метод преобразования в ИС К572ПА2 и КР572ПА2 предполагает суммирование всех разрядных токов, взвешенных по двоичному закону и пропорциональных значению опорного напряжения на входе 38(27) в соответствии с заданным значением двоичного кода на цифровых входах ЦАП.

Преобразователь рассчитан на работу от двух источников питания U СС1 =

5 В ± 5 % и U СС2 = 15 В ± 5 % при опорном напряжении U REF = 10,24 В ± 20 мВ. Наличие отдельного вывода для питания входных усилителей-

инверторов от источника +5 В ± 5 % позволяет подключить его к ТТЛ схемам

без дополнительных резисторов. Точность преобразования при этом не ухудшается.

Микросхемы К572ПА2 и КР572ПА2 допускают эксплуатацию при изменении напряжений источников питания U СС1 от 4,7 до 17 В, U СС2 от 12 до 17 В, опорного напряжения U REF в диапазоне ± 22,5 В. Но при этом не гарантируются нормы на электрические параметры, и необходимо выполнение условия U СС1 U СС2, а U Н1

U СС2, а U Н1 U СС1.

U СС1.

Облегченный режим эксплуатации ИС К572ПА2 (КР572ПА2)

обеспечивается при U СС1 = 5 В ± 5 %, U СС2 = 15 В + 5 %, U REF = 10 В +1 %.

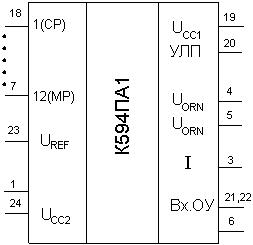

Микросхема К594ПА1

Микросхема типа К594ПА1 (рисунок 3) представляет собой параллельный ЦАП с суммированием токов, комбинированной матрицей (взвешенных R и 2R резисторов), предназначена для преобразования 12разрядного двоичного кода в ток и работает со стандартными уровнями сигналов от ТТЛ и КМОП ЦИС.

Рисунок 3 – Микросхема К594ПА1

Нумерация и назначение выводов микросхемы: 1 – вход сдвига выходного уровня; 2 – выход-вход сдвига выходного уровня; 3 – выход; 4 – обратная

связь UORN=10 В; 5 – обратная связь UORN=20 В; 6 – общий; 7 – цифровой вход 12 (МР); 8– 17 – цифровые входы 11 – 2; 18 – цифровой вход 1 (СР); 19

– напряжение источника питания U CC1; 20 – управление логическим порогом; 21 – инвертирующий вход ОУ; 22 – инвертирующий вход ОУ; 23 – вход источника опорного напряжения U REF; 24 – напряжение источника питания

U CC2.

Основные электрические параметры: |

|

|

|

Не менее |

Не более |

– число разрядов b |

12 |

– |

– дифференциальная нелинейность δLD, % |

-0,012 |

0,012 |

– время установления выходного тока tsI, мкс |

– |

3,5 |

– выходной ток I0, мА |

– |

2,2 |

– ток потребления ICC1, мА |

– |

25 |

– ток потребления ICC2, мА |

– |

35 |