Материал: 832

115

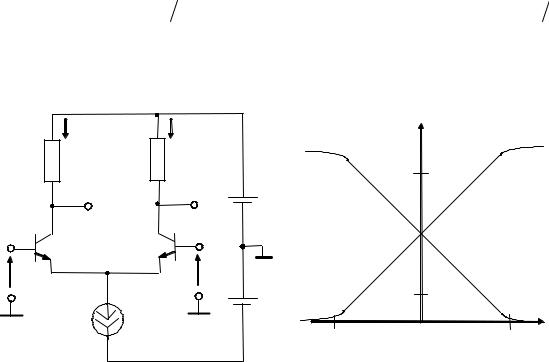

кады (ДУ). Каскад обычно питается от двухполярного источника (с одинаковыми по величине напряжениями +Е и –Е), относи-

тельно общей точки которого ведется отсчет входных (Uвх1 |

и |

Uвх2) и выходных (Uвых1 и Uвых2 ) напряжений (рис. 11.1, а). Сим- |

|

метрия схемы относительно генератора постоянного тока |

Iг |

практически устраняет дрейф нулевого уровня из-за температурного смещения входных и выходных характеристик транзисторов VT1 и VT2 (транзисторы идентичны).

Если входные напряжения Uвх1 и Uвх2 совпадают по фазе и одинаковы по амплитуде (такие сигналы называют синфазными)

Uвх1 Uвх2 Uсф ,

то токи в плечах ДУ остаются постоянными (в силу симметрии

схемы они равны Iг |

2). При этом Uвых1 Uвых2 |

Е IгRК 2, а |

|||

между коллекторами транзисторов VT1 и VT2 отсутствует раз- |

|||||

ность потенциалов |

Uвых Uвых1 Uвых2 |

0. |

|

|

|

|

|

|

|

||

I |

|

I2 |

I / Iг |

|

|

1 |

|

|

|

|

|

RК |

|

RК |

|

08, |

I1 / Iг |

Uвых1 |

Uвых2 Е |

|

|||

|

|

|

|||

|

|

|

|

||

VT1 |

VT2 |

|

|

|

|

Uвх |

|

Uвх2 |

|

02, |

I2 / Iг |

|

Iг |

|

|

||

|

Е |

|

|

4 Uвх /φТ |

|

|

|

4 |

|

|

|

|

а |

|

б |

|

|

Рис. 11.1 – Дифференциальный усилитель (а) |

|||||

|

и его вольтамперная характеристика (б) |

|

|||

Если на вход ДУ подается дифференциальный входной сиг- |

|||||

нал Uвх Uвх1 |

Uвх2 |

0, то происходит перераспределение токов |

|||

между плечами каскада, но сумма токов I1 I2 Iг |

остается по- |

||||

стоянной. На рис. 11.1, б показаны зависимости I1 |

и I2 от Uвх , |

||||

определяемые соотношениями |

|

|

|

||

116

I1 Iг  1 e Uвх

1 e Uвх Т и I2 Iг

Т и I2 Iг  1 eUвх

1 eUвх Т ,

Т ,

где Т kT – температурный потенциал; e

k – постоянная Больцмана;

Т – температура перехода по абсолютной шкале; е – заряд электрона.

При комнатной температуре Т 26 мВ. Линейный диапазон изменения входного дифференциального напряжения составляет примерно 2 Т , а полный – 4 Т . Если нагрузка включается между коллекторами транзисторов VT1 и VT2 (например, стрелочный милливольтметр), реализуются усилительные свойства обеих половин ДУ. Но часто используется и несимметричный выход, когда в качестве выходного сигнала используется изменение Uвых1 или Uвых2 ( Uвых1 и Uвых2 равны по величине, но противоположны по фазе).

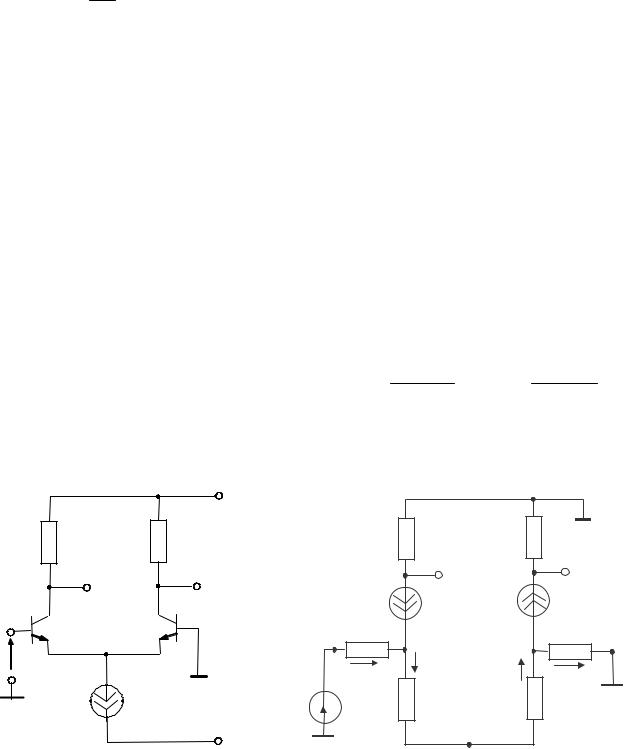

Для оценки коэффициентов передачи по напряжению для

входного дифференциального сигнала K1 Uвых1 и K2 Uвых2

Uвх Uвх

(рис. 11.2, а) воспользуемся эквивалентной схемой для приращений напряжений и токов (рис. 11.2, б).

|

|

Е |

|

|

|

|

RК |

RК |

|

RК |

|

RК |

|

|

|

|

U |

|

Uвых2 |

|

|

Uвых1 |

Uвых2 |

вых1 |

|

|

|

|

Яiб |

|

Яi |

|

||

|

|

|

|

б |

||

|

|

|

|

iб |

||

VT1 |

VT2 |

|

iб |

|

|

|

|

A rб |

|

rб |

C |

||

Uвх |

B |

|

iэ |

iэ |

|

|

|

|

iб |

|

|||

|

|

|

iб |

|

|

|

|

Iг |

|

rэ |

rэ |

|

|

|

|

|

Uвх |

|

|

|

|

|

Е |

B |

|

|

|

|

|

|

|

|

|

|

|

а) |

|

б) |

|

|

|

Рис. 11.2 – Вариант схемы дифференциального усилителя (а) и эквивалентная схема для определения входного сопротивления и коэффициента усиления по напряжению для дифференциального сигнала (б)

117

Входное сопротивление для дифференциального сигнала (обходим контур ABC)

r |

|

Uвх |

|

rбiб rэiэ rэiэ rбiб |

2 r |

r 1 β 2h |

11Э |

, (11.2) |

|

i |

i |

||||||||

вх |

|

|

б |

э |

|

||||

|

|

б |

|

б |

|

|

|

|

т.е. в два раза больше,чем для каскада посхемес общимэмиттером. Приращения выходных напряжений можно оценить как

Uвых2 Uвых1 iбRК.

Коэффициенты усиления входного дифференциального напряжения

K K |

|

K |

|

U |

вых2 |

|

iбRК |

|

RК |

. (11.3) |

|

Uвх |

|

|

|||||||

|

2 |

1 |

|

|

rвхiб |

2h11Э |

||||

Переменная составляющая напряжения в точке В (общая точка эмиттеров транзисторов VT1 и VT2) равна половине Uвх . Она является входным сигналом для транзистора VT2, включенного по схеме с общей базой. Его входное сопротивление является элементом последовательной обратной связи по току для транзистора VT1, увеличивающим входное сопротивление со стороны базы этого транзистора.

Сопротивление эмиттерного перехода связано с током эмит-

тера транзистора соотношением r |

Т . |

|

(11.4) |

|

|

|

э |

Iэ |

|

|

|

|

+E |

|

RК |

|

|

RК |

RК |

|

Uвых1 |

||

|

|

||||

Uвых1 |

Uвых2 |

rб |

|

iб |

|

Uсф |

|

|

|

|

|

|

|

|

|

|

|

VT1 0 VT2 |

|

iб |

iэ |

rэ |

iэ |

|

|

||||

|

|

Uсф |

|

|

|

Iг |

|

|

2iэ |

Rг |

|

|

-E |

|

|

||

|

|

|

|

|

|

а |

|

|

б |

|

|

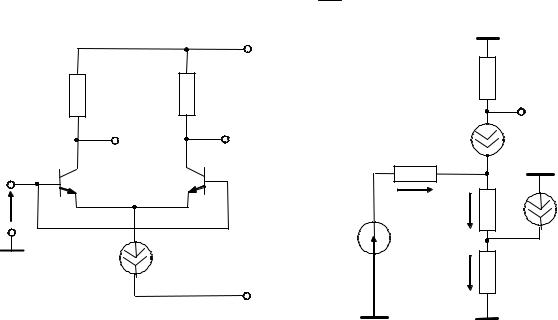

Рис. 11.3 – Схема для оценки коэффициента передачи синфазного сигнала в дифференциальном усилителе

118

Для уменьшения входных токов и повышения входного сопротивления входной дифференциальный каскад переводят в режим микротоков. При этом rэ 1 rб и справедливы соотношения

r |

2r 1 и K |

RK |

|

|

RK |

. |

(11.5) |

2rэ 1 |

|

||||||

вх |

э |

|

2rэ |

|

|

||

|

|

|

|

|

|||

Выходное сопротивление реального генератора постоянного |

|||||||

тока Rг не равно бесконечности. Вследствие этого даже при пол- |

|||||||

ной симметрии плеч наблюдаются определенные |

изменения |

||||||

Uвых1 или Uвых2 при изменении входного синфазного напряжения (рис. 11.3, а). Для оценки коэффициента передачи синфазного напряжения воспользуемся эквивалентной схемой, приведенной к одному плечу дифференциального усилителя (рис. 11.3, б).

Входное сопротивление синфазному сигналу

|

Uсф |

|

r i r i 2R i |

э |

r r 2R 1 2R 1 .(11.6) |

|||||||||||||

r |

|

|

|

б б |

э э |

г |

||||||||||||

i |

|

i |

|

|

|

|||||||||||||

сф |

|

|

|

|

|

|

|

б |

э |

г |

|

|

г |

|

||||

|

|

б |

|

|

б |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Коэффициент передачи синфазного напряжения |

|

||||||||||||||||

|

|

|

|

Kсф |

|

Uвых1 |

|

|

iбRK |

|

RK |

|

|

RK |

. |

(11.7) |

||

|

|

|

|

|

rсф iб |

2Rг 1 |

|

|||||||||||

|

|

|

|

|

|

|

Uсф |

|

|

|

|

2Rг |

|

|||||

Важной характеристикой дифференциального усилителя является коэффициент ослабления синфазного сигнала Мсф, опре-

деляемый отношением коэффициентов усиления K и Kсф:

RK

М |

сф |

|

K |

|

|

2rэ |

|

|

Rг |

. |

(11.8) |

|

|

|

RK |

|

|

||||||||

|

|

K |

|

|

|

|

|

r |

|

|||

|

|

|

|

сф |

|

|

|

|

|

э |

|

|

|

|

|

|

|

|

|

|

|||||

2Rг

Его часто оценивают в децибелах

Мсф,дБ 20lgМсф .

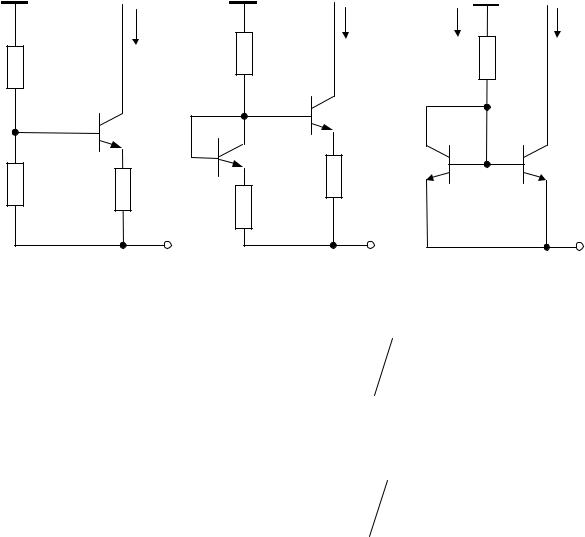

11.2Стабилизаторы тока

Варианты построения схем генераторов постоянного тока (стабилизаторов тока) для дифференциального усилительного

119

каскада приведены на рис. 11.4 (в простейшей схеме каскада вместо генератора тока включается резистор R г).

В схеме рис. 11.4, а эмиттерный ток транзистора VT1 задается с помощью базового делителя и резистора R0:

|

Iг |

Iг |

I |

Iг |

|

|

|||

R1 |

|

R1 |

|

R1 |

|

|

|

||

|

|

|

|

|

|

VT1 |

VT1 |

|

|

|

VT2 |

|

|

|

|

|

|

VT1 |

|

R2 |

|

R0 |

|

|

R0 |

|

VT2 |

||

R2 |

|

|||

|

-E |

|

-E |

|

|

-E |

|

||

|

а) |

б)б |

|

вв) |

Рис. 11.4 – Варианты построения схем стабилизаторов тока

I |

|

|

E R2 |

U |

|

R , |

|

|

|

|

(11.9) |

||||

|

|

||||||

|

Э |

R R |

|

ЭБ |

0 |

|

|

|

|

|

1 2 |

|

|

|

|

где UЭБ 0,7 В для кремниевого транзистора. Коллекторный ток практически повторяет ток эмиттера и почти не зависит от потенциала коллектора VT1. Поэтому

I |

|

|

E R2 |

|

|

|

|

|

R . |

|

||||

|

|

|

|

0,7 |

|

(11.10) |

||||||||

|

|

|

|

|||||||||||

|

г |

R R |

2 |

|

|

|

|

0 |

|

|||||

|

|

|

1 |

|

|

|

|

|

|

|

||||

Для повышения температурной стабильности генератора |

||||||||||||||

тока в схеме рис. 11.4, б последовательно с R2 включен транзи- |

||||||||||||||

стор VT2 в диодном включении. Для этой схемы |

|

|||||||||||||

|

|

I |

|

|

|

E 0,7 R2 |

. |

|

(11.11) |

|||||

|

|

|

|

|

|

|||||||||

|

|

|

г |

|

R R |

2 |

R |

|

|

|||||

|

|

|

|

|

|

1 |

|

|

|

0 |

|

|

|

|

Интересно, что схема сохраняет свои функции и при выполнении условия R2 R0 0 (см. рис. 11.4, в).