Материал: 1740

41

ляет выдавать в любой момент времени записанный в нем параллельный код.

Генератор эталонных напряжений состоит из кодирующей матрицы сопротивлений, управляемой напряжением с триггеров памяти через ключи КЛ1-КЛ7.

В исходном состоянии все триггеры памяти находятся в положении «0», в которое они установлены коммутирующим импульсом, снимаемым с восьмого выхода распределителя и определяющим начало цикла кодирования. При этом все ключи закрыты, и с их выхода снимается напряжение, близкое к нулю.

Каждый из ключей КЛ1-КЛ7 открывается при подаче на него положительного импульса с триггера памяти соответствующего разряда и создает на входе сравнивающего устройства (компаратора) опорное напряжение, которое равно взвешенной сумме эталонных напряжений

n |

|

E |

|

|

|

Uоп |

ak |

, |

(2.9) |

||

k |

|||||

k 1 |

|

2 |

|

|

где Е=10 В,

ak |

1 |

при подключении источника (КЛk открыт); , |

|

0 |

при подключении "земли" (КЛk закрыт). |

Первый коммутирующий импульс распределителя управляет триггером памяти старшего разряда – перебрасывает его в состояние «1»; импульс триггера открывает ключ КЛ1, на матрицу поступает напряжение Е, на выходе ГЭН формируется

Uэт 6 E 2 5 В и поступает на один вход компаратора. На другой вход компаратора подается кодируемое напряжение Х. Если Uэт 6 X , то на выходе компаратора формируется поло-

2 5 В и поступает на один вход компаратора. На другой вход компаратора подается кодируемое напряжение Х. Если Uэт 6 X , то на выходе компаратора формируется поло-

жительный импульс. Этот импульс подается на вход как импульс старшего разряда обратного кода и одновременно возвращает триггер старшего разряда Т7 в состояние «0». В «нулевом» состоянии Т7 находится до конца цикла кодирования (т.е. триггер помнит, что входное напряжение не превышает 5 В).

При этом Uэт 6 E 2 5 В убирается с выхода кодирующей

2 5 В убирается с выхода кодирующей

матрицы.

42

U(t) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Б1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Б2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Б4 А1 А2

А3 А4 А5 А6 А7

А8

Б6

Б7

t

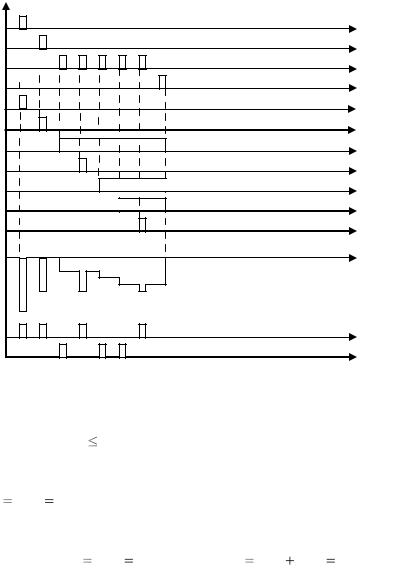

Рис. 2.7 – Временные диаграммы работы преобразователя с обратной связью

Если Uэт 6 X , импульс старшего разряда на выходе

обратного кода отсутствует и триггер памяти Т7 остается в состоянии «1» до конца цикла кодирования. Напряжение

Uэт 6 E 2 5 В остается на выходе кодирующей матрицы до

2 5 В остается на выходе кодирующей матрицы до

конца цикла кодирования.

Следующий импульс распределителя устанавливает на выходе ГЭН Uоп E 4 2,5 В либо Uоп E

4 2,5 В либо Uоп E 2 E

2 E 4 7,5 В (в зависимости от результата сравнения в первом такте). Теперь Х сравнивается с Uоп .

4 7,5 В (в зависимости от результата сравнения в первом такте). Теперь Х сравнивается с Uоп .

43

Значения остальных разрядов формируются в следующих тактах аналогично. Процесс продолжается до тех пор, пока не произойдет сравнение во всех разрядах.

Таким образом, после семи тактов преобразования в регистре памяти будет записан семиразрядный двоичный код, соответствующий величине входного напряжения. Полученный код может быть выдан потребителю или в параллельном виде при считывании из регистра памяти или в последовательном виде при использовании сигналов схемы сравнения. Как следует из алгоритма преобразования по методу поразрядного кодирования, на выходе схемы сравнения формируется последовательный обратный код. Для получения прямого последовательного кода применена схема запрета. Таким образом, в последовательности импульсов обратного кода присутствуют импульсы тех разрядов, которые отсутствовали в последовательности прямого кода, и наоборот.

В конце каждого цикла кодирования триггеры ставятся в положение «0» восьмым импульсом распределителя: регистр подготовлен к следующему циклу кодирования.

4. Основные характеристики преобразователя

Очевидно, разрешающая способность равна приращению входной величины, соответствующему изменению входного кода на единицу младшего разряда, т.е. шагу квантования по уровню

X |

E |

. |

(2.10) |

n |

|||

|

2 |

|

|

Быстродействие преобразователя определяется числом преобразований в единицу времени. Быстродействие преобразователя определяет полосу частот сигнала, пропускаемых преобразователем без существенных искажений.

Точность преобразования складывается из ошибок квантования по уровню и инструментальной ошибки.

Инструментальная ошибка зависит от характеристик резисторного делителя на матрице R-2R, ключей, схемы сравнения и источника напряжения питания Е. Для резисторного делителя

44

важно постоянство заданного отношения сопротивлений резисторов, которое обеспечивается проще, если все резисторы изготавливаются одновременно по единой технологии. Поэтому резистивные делители для преобразователей выпускаются в виде отдельных функционально и конструктивно законченных узлов.

Параметрами ключа, влияющими на точность и скорость преобразования, являются остаточное (ненулевое) напряжение на замкнутом ключе, остаточный ток и время переключения. При увеличении сопротивлений матрицы R-2R влияние остаточного напряжения уменьшается, но увеличиваются переходные процессы и сильнее оказывается остаточный ток разомкнутого ключа.

Схемы сравнения в интегральном исполнении строятся обычно на основе усилителей постоянного тока. Влияние схемы сравнения на инструментальную погрешность зависит от еѐ чувствительности, которая определяется ошибками за счет дрейфа и шумов усилителей.

Ошибка квантования по уровню при Хэф |

X равномер- |

но распределена в интервале X , где Х эф – эффективное зна-

чение кодируемого сигнала. Тогда среднеквадратическая ошибка квантования равна

|

|

|

X |

|

, |

|

||

кв |

|

|

|

|

|

|

(2.11) |

|

2 |

3 |

|

|

|||||

|

|

|

|

|||||

а максимальная ошибка |

X / 2 . Эффективная относитель- |

|||||||

ная ошибка преобразования |

|

|

|

|

|

|

|

|

|

|

|

|

кв |

. |

(2.12) |

||

эф |

|

|

Х |

|

||||

|

|

|

|

|

|

|||

|

|

|

эф |

|

||||

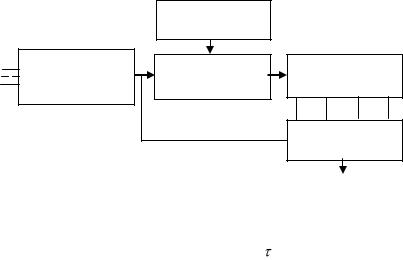

5. Преобразователь временного интервала в двоичный код (кодирующее устройство последовательного счета)

5.1. Принцип действия преобразователя

Исследуемый преобразователь представляет собой устройство счетно-импульсного типа, осуществляющее циклическое

45

преобразование напряжения в код с промежуточным преобразованием напряжения во временной интервал.

Действие кодирующего устройства основано на преобразовании мгновенных значений функции X(t) в число импульсов. Преобразование осуществляется в течение фиксированного цикла путем последовательного выполнения следующих операций:

1)дискретизации сигнала во времени и формирования отсчетов АИМ-2;

2)преобразования отсчетов в импульсы с ОШИМ;

3)квантования во времени путем наложения последовательности квантующих импульсов на ОШИМ сигнал;

4)кодового представления сигнала путем двоичного счета числа квантующих импульсов;

5)считывания состояний ячеек двоичного счетчика по окончании счета;

6)возвращения (сброса) счетчика в исходное состояние. Структурная схема кодирующего устройства приведена на

рис. 2.8.

|

Генератор |

|

|

|

квантования |

|

|

Коммутатор и |

Схема |

Двоичный |

|

преобразователь |

|||

совпадения |

счетчик |

||

АИМ-ОШИМ |

|||

|

|

||

|

|

Считывающее |

|

|

|

устройство |

Рис 2.8 – Структурная схема кодирующего устройства последовательного счета

Отсчет передаваемого аналогового сигнала X(t) преобразуется в импульс с ОШИМ длительностью X . Импульсы с генератора квантования поступают с периодом следования