Материал: 1740

36

Следовательно, передача непрерывных сообщений заменяется передачей последовательности чисел. Эти числа можно выразить в удобной системе счисления и передать по линии связи в виде последовательности кодовых комбинаций. В технических приложениях наибольшее применение находит двоичная система счисления. Реализация двух цифр такой системы (0 и 1) наиболее проста.

Каждому целому числу (уровню квантования) можно поставить в соответствие двоичное n-разрядное число. Обычно используется натуральный двоичный код, в котором кодовые группы соответствуют номеру передаваемого уровня квантования в двоичной системе счисления, т.е. структура кодовой группы определяется выражением

|

n 1 |

|

N an 1 2n 1 an 2 2n 2 ... a0 |

20 |

ai 2i , (2.6) |

|

i |

0 |

где ai – кодовый символ i-го разряда ( ai |

0; 1 ). |

|

Множители 2n 1 ,2n 2 ,...,20 называют весовыми коэффици-

ентами соответствующего разряда или просто весами разрядов. Количество уровней амплитуды, которые можно представить в виде n-разрядного двоичного числа, равно

|

|

|

|

|

|

|

|

M |

X max |

|

|

Xmin |

2n . |

|

(2.7) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

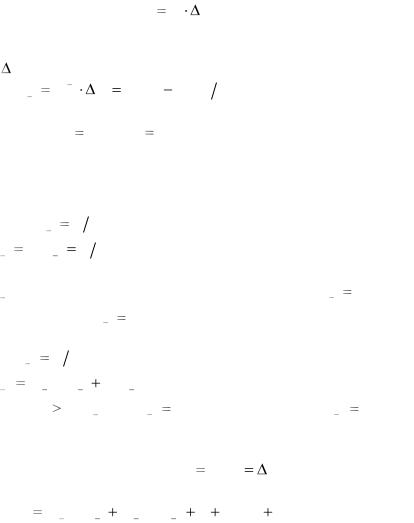

Двоичные символы числа N можно представить условно в |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

виде наличия или от- |

||

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

|

сутствия импульса на |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

соответствующих |

по- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

зициях. На рис. 2.4 по- |

||

64 |

32 |

16 |

8 |

4 |

2 |

|

1 t |

казана двоичная |

им- |

||||||||

Рис. 2.4 – Последовательность |

пульсно-кодовая груп- |

||||||||||||||||

импульсов, отображающая число |

па, соответствующая |

||||||||||||||||

N=107 в двоичной системе счисления |

десятичному |

числу |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N=107 при числе |

раз- |

|

рядов n=7.

3. Преобразователь напряжения в цифровой двоичный код (АЦП) взвешивающего типа

37

3.1. Принцип действия преобразователя

Работа преобразователя основана на сравнении кодируемого напряжения x(t) с взвешенной суммой n эталонных напряжений, величины которых равны

Uэт i 2 |

i |

U , |

(2.8) |

|

|||

|

|

где i=n–1, n–2, … ,1, 0 |

– номер разряда; |

|

|||||||

n – число разрядов; |

|

|

|

|

|

|

|||

U – шаг равномерного квантования; |

|||||||||

U |

эт n 1 |

2n 1 |

U |

( X |

max |

X |

min |

) 2 |

– эталон наибольшего |

|

|

|

|

|

|

|

|||

веса (старшего разряда). |

|

|

|

|

|

||||

Пусть X min |

0 , X max |

E . |

|

|

|

|

|||

Преобразование напряжения Х в n-разрядное число осуществляется здесь за n тактов; на каждом такте вырабатывается очередной двоичный символ.

Первый такт. Вырабатывается первое эталонное напряже-

ние |

Uэт n 1 |

E 2 |

и |

первое |

опорное |

напряжение |

Uоп n 1 |

Uэт n 1 |

E 2 . |

|

|

|

|

Если кодируемое |

напряжение |

Х оказалось |

больше, чем |

|||

Uоп n 1 , то первый символ (символ старшего разряда) Sn 1 1 ; в

противном случае Sn 1 0.

Второй такт. Вырабатывается второе эталонное напряже-

ние Uэт n |

2 |

E 4 и формируется второе опорное напряжение |

|

Uоп n 2 |

Sn 1Uэт n 1 |

Uэт n 2 . |

|

Если X |

Uоп n |

2 , то Sn 2 1 ; в противном случае Sn 2 0. |

|

Такие операции повторяются до последнего, n-го такта.

n-й такт. Последнее эталонное напряжение равно шагу квантования по амплитуде E 2n U , а последнее опорное напряжение уже незначительно отличается от Х

2n U , а последнее опорное напряжение уже незначительно отличается от Х

.

38

Если X Uоп 0 , то S0 1 ; в противном случае S0 0. На этом цикл преобразования заканчивается.

В табл. 2.1 в качестве примера указаны значения перечисленных величин для пятиразрядного (n=5) преобразователя, рассчитанного на преобразование напряжений Х, которые могут

принимать любое значение |

в интервале |

от X min |

0 до |

||||||

X max |

E 8 . Пусть величина входного напряжения равна 3,31. |

||||||||

|

Таблица 2.1 – Пример преобразования методом взвешивания |

||||||||

|

Х |

Номер такта |

|

Uэт i |

|

Uоп i |

|

Si |

|

|

|

1 |

|

4,00 |

|

4,00 |

|

0 |

|

|

|

2 |

|

2,00 |

|

2,00 |

|

1 |

|

|

3,31 |

|

|

|

|

|

|

|

|

|

3 |

|

1,00 |

|

3,00 |

|

1 |

|

|

|

|

4 |

|

0,50 |

|

3,50 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

0,25 |

|

3,25 |

|

1 |

|

3.2. Описание лабораторной установки

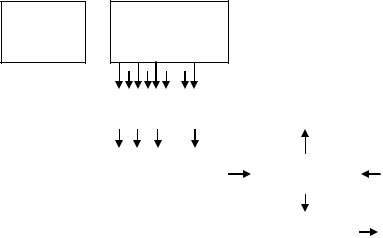

Исследуемый преобразователь построен по типу прямого преобразования с цепью обратной связи. Структурная схема преобразователя приведена на рис. 2.5.

Основные узлы преобразователя выполняют следующие функции:

1)генератор тактовых импульсов (ГТИ) вырабатывает периодическую последовательность прямоугольных импульсов, которые управляют работой всего преобразователя. Период по-

вторения импульсов ТГТИ определяет время, необходимое для образования одного разряда двоичного числа;

2)распределитель импульсов определяет частоту циклов кодирования, управляя распределением импульсов кодовой группы по соответствующим разрядам;

3)входное кодируемое напряжение x(t) подается в сравнивающее устройство, где производится его последовательное сравнение с эталонным напряжением, формируемым в генераторе эталонного напряжения (ГЭН);

39

Генератор Распределитель тактовых  импульсов импульсов

импульсов импульсов

|

|

|

|

|

|

Управляющее |

|

Цепь обратной |

|

||

|

устройство |

|

связи |

|

|

|

|

Uоп |

|

|

|

|

|

|

|

|

|

|

Генератор |

|

|

x(t) |

|

|

Сравнивающее |

||||

|

эталонного |

|

|

||

|

|

устройство |

|

||

|

напряжения |

|

|

||

|

|

|

|

Вых. |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Формирующее |

||

|

|

|

|

||

|

|

|

устройство |

|

|

|

|

|

|

|

|

Рис. 2.5 – Структурная схема преобразователя

собратной связью

4)вырабатываемое в результате сравнения напряжение ошибки через цепь обратной связи воздействует на управляющее устройство и таким образом управляет выдачей эталонного напряжения соответствующего разряда;

5)результат сравнения с формирующего устройства поступает на выход преобразователя в виде импульсов кода.

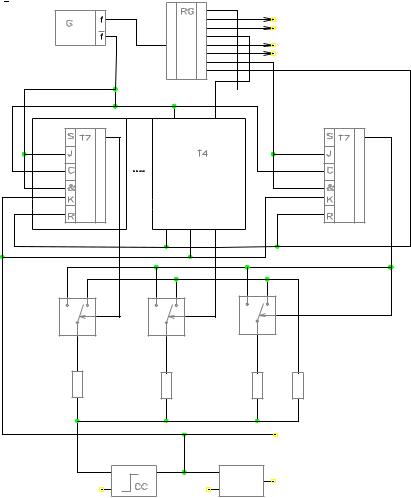

Функциональная схема преобразователя приведена на рис.

2.6.

Работа преобразователя иллюстрируется временными диаграммами на рис. 2.7.

Импульсы ГТИ служат импульсами запуска для циклического распределителя на триггерах.

В преобразователе использован семиразрядный код (n=7), поэтому на восьми выходах распределителя появляется серия коммутирующих импульсов, равномерно сдвинутых во времени друг относительно друга. Цикл кодирования повторяется с пе-

риодом Т=8ТГТИ – это время, необходимое для образования одной кодовой комбинации.

|

|

|

|

|

|

|

|

|

|

40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

Б1 |

|

Б2 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

1 |

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

Б3 |

|

|

|

|

|

2 |

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Б4 |

|

|

|

|

|

|

|

|

5 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

1 |

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

2 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

2 |

|

|

1 |

|

2 |

|

|

1 |

|

2 |

|

|

|

|

|

|

|

|

||

|

1 |

0 |

|

|

|

|

1 |

0 |

|

|

|

1 |

1 |

0 |

2 |

|

|

1 |

2 |

|

|

1 |

2 |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

КЛ7 |

|

|

КЛ4 |

|

|

|

|

|

|

КЛ1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

4 |

4 |

|

|

|

|

4 |

4 |

|

|

|

|

|

4 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

A1 |

|

|

|

|

A4 |

|

|

|

|

|

|

A7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

3 |

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

3 |

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2n-1*R |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Б7 |

|

|

|

|

|

2 |

3 |

3 |

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

2 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Б5 |

|

|

|

3 |

|

3 |

Б6 |

|

|

|

|

|

1 |

1 |

|

|

|

|

_ |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fT |

|

|

|

|

|

|

|

Рис. 2.6 – Функциональная схема преобразователя |

|||||||||||||||||

собратной связью

Вкачестве управляющего устройства используется статический триггерный регистр (регистр памяти) – Т1-Т7. Запись чисел в регистр производится в параллельном коде. В каждом

триггере хранится один разряд двоичного числа. Регистр позво-