Материал: Электроника

ТТЛ с открытым коллектором применяется для подключения элементов индикации (миниатюрные лампы накаливания, светодиоды, семисегментные индикаторы [один сегмент]).

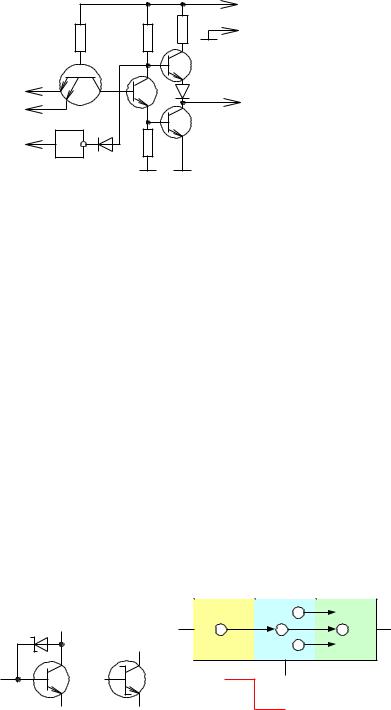

2) ТТЛ с Z-состоянием. Третьим, или Z-состоянием называется запрет приёма информации, при котором выходное сопротивление логического элемента стремится к бесконечности, а выходной ток – к нулю.

|

|

|

|

|

+ |

|

|

R1 |

R2 |

R4 |

Uип |

|

|

|

- |

||

|

|

|

|

|

|

|

|

VT1 |

A |

VT3 |

|

X1 |

|

|

VT2 |

VD2 |

Y |

|

|

|

|||

X2 |

|

|

|

VT4 |

|

|

DD1 |

VD1 |

|

|

|

Eo |

|

|

|

||

1 |

|

R3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

|

X2 |

|

Y |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

|

1 |

||

0 |

|

0 |

|

1 |

|

1 |

||

0 |

|

1 |

|

0 |

|

1 |

||

0 |

|

1 |

|

1 |

|

0 |

||

1 |

|

0 |

|

0 |

|

Z |

||

1 |

|

0 |

|

1 |

|

Z |

||

1 |

|

1 |

|

0 |

|

Z |

||

1 |

|

1 |

|

1 |

|

Z |

||

|

|

|

|

|

|

|

|

|

Рис. 189 |

Рис. 190 |

Если на запрещающий вход с инверсией подать логический ноль, то на выходе инвертора DD1 установится высокий уровень логической единицы, диод VD1 закроется, что равносильно разрыву цепи, и схема будет работать как базовый элемент ТТЛ, выполняющий функцию И- НЕ. При подаче на запрещающий вход логической единицы на выходе инвертора DD1 будет логический ноль, и диод VD1 откроется. Точка «А» схемы окажется под напряжением близким к нулю, т. е. под напряжением логического нуля выходного сигнала инвертора DD1. Это приведёт к тому, что транзистор VT3 закроется. Ток через транзистор VT2, а следовательно, в базе VT4, будет близок к нулю, и транзистор VT4 тоже закроется. Таким образом, оба транзистора – и VT3 и VT4 - будут одновременно закрыты при любых состояниях на информационных входах X1 и X2. Это и является Z-состоянием схемы.

3)ТТЛШ.

Кодному из недостатков ТТЛ можно отнести сравнительно невысокое быстродействие. Это объясняется тем, что при переключении транзистора из режима насыщения в режим отсечки база транзистора оказывается насыщенной неосновными носителями заряда. И коллекторный ток транзистора будет продолжать течь до тех пор, пока неосновные носители заряда не перейдут из базы в коллектор. Для повышения быстродействия в ТТЛШ между базой и коллектором транзистора включают быстродействующий переход Шоттки. В этом случае неосновные носители будут переходить из базы в коллектор не через коллекторный p-n переход, а через переход Шоттки (смотрите Рис. 192).

На принципиальных схемах транзистор с переходом Шоттки обозначается следующим образом:

Э |

|

- |

|

К |

|

- |

- |

- |

|||

|

|

||||

|

|

p - |

n |

|

= |

Б |

|

|

Рис. 191 |

Рис. 192 |

|

4) Оптоэлектронные ИМС.

Оптроном, или оптоэлектронной парой называется устройство, состоящее из светоизлучателя, фотоприёмника и оптически прозрачной среды между ними.

Светоизлучателем служит излучающий диод, фотоприёмником может служить фоторезистор, фотодиод, фототранзистор, поэтому оптроны называют резисторными, транзисторными, диод-

Е. А. Москатов. Стр. 76

ными, симисторными, динисторными. Основная задача оптрона – обеспечить передачу информации без электрической связи между входом и выходом.

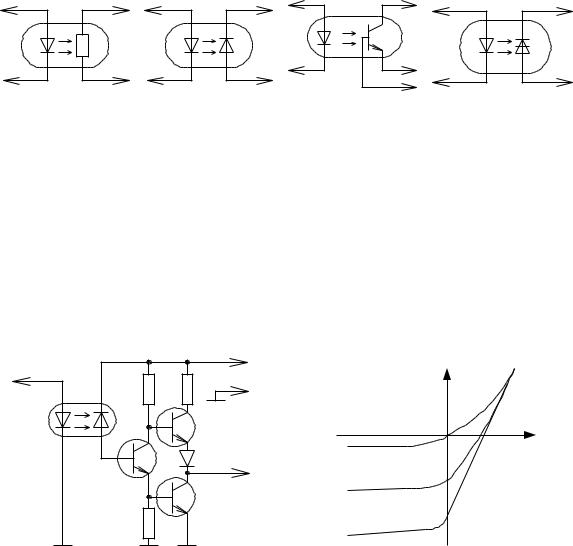

УГО оптронов изображено на рисунках 193 – 196.

Рис. 193 |

Рис. 194 |

Рис. 195 |

Рис. 196 |

На рисунке 193 изображён резисторный оптрон, на 194 – диодный, на 195 – транзисторный и на рисунке 196, соответственно, динисторный.

Маркировка оптронов.

|

А |

О |

Д |

103 |

А |

|

1 |

2 |

3 |

4 |

5 |

Расшифровывается маркировка так: |

|||||

1 |

группа – материал полупроводника. Буква «А» означает арсенид галлия. |

||||

2 |

группа. Буква «О» означает, что мы имеем дело с оптроном. |

||||

3 |

группа. Тип оптрона по виду фотоприёмника. «Д» – диодный оптрон, «У» – тиристорный. |

||||

4 |

группа – группа по электрическим параметрам. |

||||

5 |

группа – модификация прибора в четвёртой группе. |

||||

В цифровых ИМС применяют диодные оптроны (смотрите рисунок 197).

X1 |

|

+ |

|

I |

R3 |

Uип |

|

||

R1 |

|

|||

VD1 |

|

- |

|

|

|

|

|

|

|

VT1 |

VT2 |

|

|

|

|

|

|

|

|

|

VD2 |

Y |

Ф=0 |

U |

|

VT3 |

|

Ф1>0 |

|

R2 |

|

|

Ф2>Ф1 |

|

|

|

|

|

|

Рис. 197 |

|

|

|

Рис. 198 |

Принцип действия.

При подаче на вход логического нуля ток через светодиод не протекает, светодиод не светится, и через фотодиод будет протекать очень маленький темновой ток, которого не достаточно для отпирания транзистора VT1 (смотрите рисунок 198).

При подаче на вход логической единицы светодиод зажигается, и через фотодиод будет протекать достаточно большой световой обратный ток, который открывает транзистор VT1. Оставшаяся часть схемы работает как базовый элемент ТТЛ.

Логические элементы на полевых транзисторах МОП-структуры

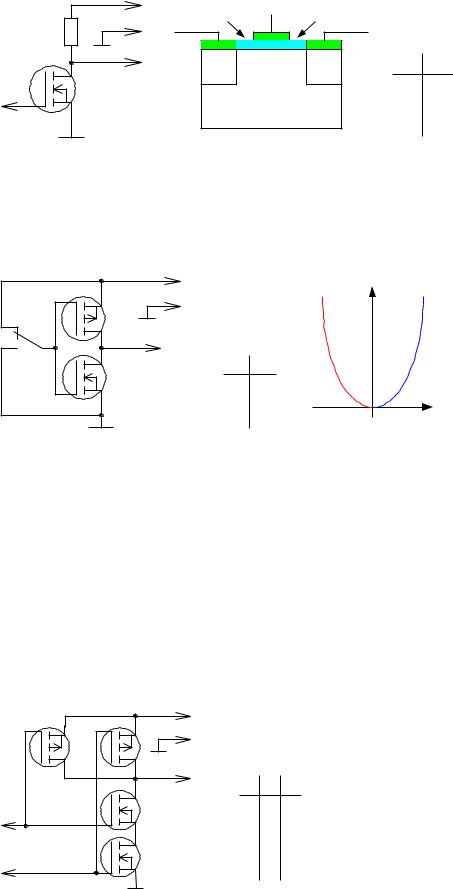

1)Ключи на МОП–транзисторах.

2)Комплементарная МОП – пара (КМОП).

3)Реализация функции И-НЕ в КМОП – логике.

4)Реализация функции ИЛИ-НЕ в КМОП – логике.

Е. А. Москатов. Стр. 77

1) Ключи на МОП–транзисторах.

|

|

+ |

И Канал |

З SiO2 |

С |

|

|

|

R |

Uип |

|

||||

|

|

- |

|

|

|

|

|

|

|

Y |

|

n |

|

x |

y |

|

С |

VT1 |

n+ |

n+ |

|||

|

|

||||||

X |

|

|

|

|

|

0 |

1 |

З |

И |

|

|

Подложка p- |

|

1 |

0 |

|

|

|

|

||||

|

Рис. 199 |

|

Рис. 200 |

|

Рис. 201 |

||

Недостатком данных ключей является наличие резисторов, которые занимают в подложке значительно больше места, чем транзистор. Поэтому наиболее широко применяются ИМС, у которых вместо резистора также применяется МОП - транзистор, но с каналом другого типа проводимости. Такие взаимодополняющие структуры получили название МОП - пар.

2) Комплементарная МОП – пара (КМОП).

|

|

+ |

|

|

|

|

VT1 |

Uип |

|

|

Ic |

"1" |

- |

|

|

||

|

|

|

|

|

|

|

X |

Y |

|

|

|

"0" |

VT2 |

x |

y |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

"p" |

"n" |

|

|

1 |

0 |

|

Uзи |

|

Рис. 202 |

Рис. 203 |

|

Рис. 204 |

|

Если на затвор подать сигнал логического нуля, то в транзисторе VT2 (c каналом «n»типа проводимости) канал будет отсутствовать, а в транзисторе VT1 с каналом «p» типа канал будет индуцирован, т. к. на затворе относительно истока будет действовать отрицательное напряжение. Через этот канал выход Y соединяется с плюсом ИП, и на выходе будет высокий уровень логической единицы.

При подаче на вход логической единицы канал в транзисторе VT1 исчезает, а в VT2 канал индуцируется и через этот канал соединяется с нулевым потенциалом общего провода, следовательно, на выходе будет логический ноль.

Достоинства комплементарной МОП – пары – отсутствие резисторов, что позволяет повысить степень интеграции; очень малое потребление тока от ИП, т. к. между плюсом и минусом ИП всегда оказывается транзистор, у которого нет канала.

Недостаток комплементарной МОП – пары: низкое быстродействие.

3) Реализация функции И-НЕ в КМОП – логике.

|

|

+ |

|

|

VT1 |

VT2 |

Uип |

|

|

|

|

- |

|

|

|

|

Y |

|

|

|

VT3 |

X1 X2 |

Y |

|

|

0 |

0 |

1 |

|

X1 |

|

|||

|

|

0 |

1 |

0 |

X2 |

VT4 |

1 |

0 |

0 |

|

1 |

1 |

0 |

|

Рис. 205 |

|

Рис. 206 |

||

Е. А. Москатов. Стр. 78

Если хотя бы на одном из входов имеется сигнал логического нуля, в соответствующем транзисторе с каналом p-типа – VT1 или VT2 – будет индуцирован канал, через который выход Y соединяется с плюсом ИП, и на выходе будет логическая единица. При подаче на оба входа логических единиц в VT1 и в VT2 каналы исчезают, а в транзисторах VT3 и VT4 каналы индуцируются, и через эти каналы выход Y соединяется с общим проводом, следовательно, на выходе будет логический ноль.

4) Реализация функции ИЛИ-НЕ в КМОП – логике.

|

+ |

"p" |

VT2 Uип |

|

- |

|

|

VT3 |

|

|

|

|

|

|

"p" |

Y |

X1 X2 |

Y |

|

"n" |

|

|

|

0 |

0 |

1 |

VT1 |

X2 |

VT4 |

|

1 |

0 |

0 |

X1 |

|

|

0 |

1 |

0 |

|

|

|

"n" |

|

|||

|

|

|

|

1 |

1 |

0 |

Рис. 207 |

|

Рис. 208 |

Если на оба входа поданы нули, то в транзисторах VT1 и VT4 с каналами n-типа каналы отсутствуют, а в VT2 и VT3 каналы индуцируются, и через них выход Y связан с плюсом ИП, следовательно, на выходе логическая единица.

Если хотя бы на один из входов подать логическую единицу, то в соответствующем транзисторе p-типа канал исчезает, и выход Y отключается от плюса ИП, а в соответствующем транзисторе с каналом n-типа канал индуцируется, и через него выход Y соединяется с общим проводом, следовательно, на выходе будет логический ноль.

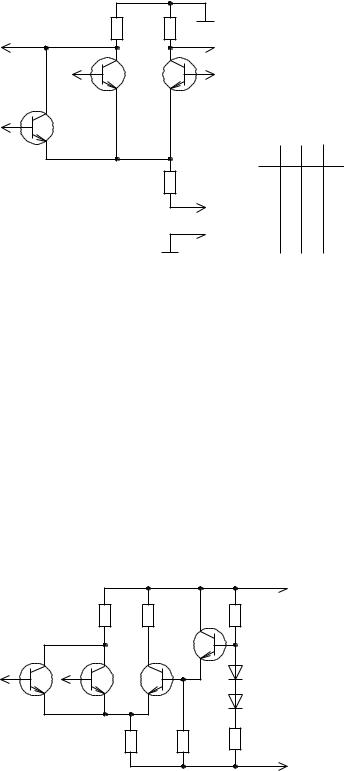

Эмиттерно-связная логика

1)Реализация функций ИЛИ и ИЛИ-НЕ в эмиттерно-связной логике (ЭСЛ).

2)Источник опорного напряжения.

3)Базовый элемент ЭСЛ серии К500.

1) Реализация функций ИЛИ и ИЛИ-НЕ в эмиттерно-связной логике (ЭСЛ).

ЭСЛ является самой быстродействующей из всех типов логики. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения или отсечки. Основой ЭСЛ является дифференциальный эмиттерный каскад, изображённый на рисунке 209.

|

+ |

|

R1 |

R2 Uип |

|

Uвых |

- |

|

VT2 |

||

Uвх1 |

||

Uвх2 |

||

VT1 |

||

|

Ia Генератор стабильного

тока

Рис. 209

Е. А. Москатов. Стр. 79

Uвх1 = Uвх2; I1 I2 Io2 ; Uвх1 > Uвх2; I1 = I0 + ΔI; I2 = I0 – ΔI.

Особенность ЭСЛ: разница уровней логической единицы и нуля очень мала, следовательно, помехоустойчивость плохая. Чтобы повысить помехоустойчивость, в ЭСЛ используется схема, при которой в цепи коллектора – соединение с общим проводом, а в цепь эмиттера подаётся минус напряжения ИП. Это приводит к тому, что все уровни напряжения отрицательны и ЭСЛ плохо согласуются с другими типами логики.

Рассмотрим следующую схему (смотрите рисунок 210), в которой U0 ≈ -1,6 В; U1 ≈ -0,8 В; Uоп ≈ -1,2 В.

Y1 |

|

R1 |

R2 |

|

|

|

|

|

|

|

Y2 |

|

|

|

|

|

|

|

X2 |

VT2 |

VT3 |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

VT1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 X2 Y1 Y2 |

|||

|

|

|

R3 |

|

0 |

0 |

1 |

0 |

|

|

|

|

|

||||

|

|

|

- |

|

0 |

1 |

0 |

1 |

|

|

|

Uип |

1 |

0 |

0 |

1 |

|

|

|

|

+ |

|

1 |

1 |

0 |

1 |

|

|

Рис. 210 |

|

|

|

Рис. 211 |

||

В данной схеме роль генератора стабильного тока (ГСТ) выполняет источник стабилизированного напряжения U = -5,2 В вместе с последовательно включённым резистором R3 достаточно большого номинала.

При подаче на оба входа логического нуля опорное напряжение оказывается более положительным, чем на базах транзисторов VT1 и VT2, следовательно, транзистор VT3 открыт в большей степени, чем VT1 и VT2. Значит, ток через R2 будет больше, чем через R1, и напряжение на Y2 (логический ноль) будет более отрицательным, чем на выходе Y (логическая единица).

Если хоть на один из входов подать логическую единицу, то напряжение на базе соответствующего транзистора становится более положительным, чем опорное. Этот транзистор (VT1 или VT2) открывается в большей степени, чем VT3. Ток через R1 будет больше, чем через R2. Напряжение на выходе Y будет более отрицательным, т. е. логическим нулём, а напряжение на выходе Y2, более положительным, т. е. логической единицей.

Вывод: ЭСЛ реализует функцию ИЛИ-НЕ по выходу Y и функцию ИЛИ по выходу Y2.

2) Источник опорного напряжения. |

||||

|

|

|

|

+Uип |

|

|

R1 |

R3 |

R5 |

|

VT1 |

|

VT4 |

|

|

|

|

|

|

X1 |

X2 |

VT2 |

VT3 |

VD1 |

|

||||

|

|

|

|

VD2 |

|

|

R2 |

R4 |

R6 |

|

|

|

|

-Uип |

|

|

Рис. 212 |

|

|

Е. А. Москатов. Стр. 80