Материал: Электроника

2)Схемотехника простейших логических элементов.

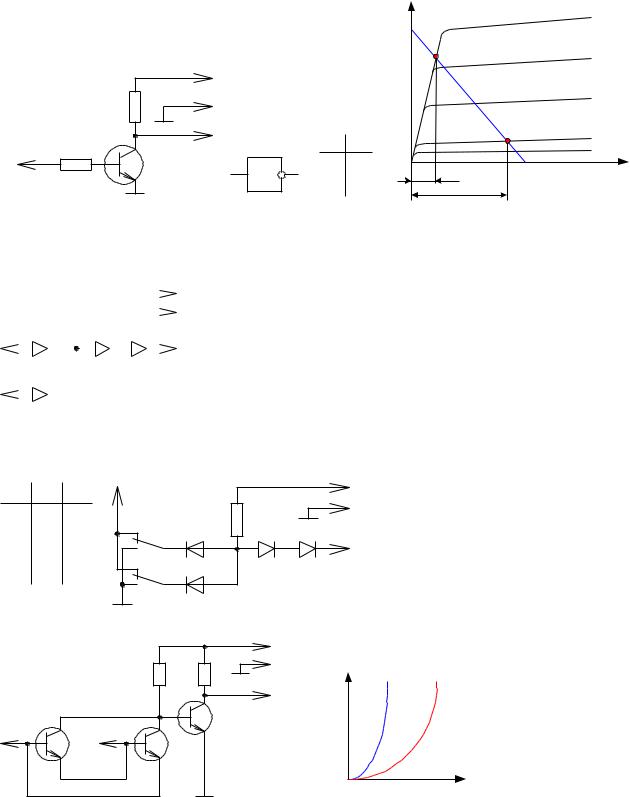

1.Элемент НЕ (смотрите рисунки 166 - 168). В общем случае представляет транзисторный ключ на полевом или биполярном транзисторе.

|

|

|

|

|

Iк |

|

Iб4=max |

|

|

|

|

|

|

Р.Т.нас |

Iб3 |

|

|

|

+ |

|

|

|

|

|

Rк |

|

Uип |

|

|

|

Iб2 |

|

|

y |

- |

|

|

Р.Т.отс |

Iб1 |

|

|

|

|

|

|||

|

|

|

|

x |

y |

||

x |

Rб |

|

|

|

Iб=0 |

||

|

VT1 |

|

1 |

0 |

1 |

Uнас |

E к |

|

|

|

1 |

0 |

|||

|

|

|

|

Uотс |

|

||

|

Рис. 165 |

|

Рис. 166 |

Рис. 167 |

Рис. 168 |

|

|

2.Элемент ИЛИ. В простейшем случае реализуется на полупроводниковых диодах (смотрите рисунок 169). Необходимым условием для работы является: 1) Uвх1 > Uип; 2) R >>

Ri.пр.

|

|

|

|

|

|

|

|

|

|

|

+ |

ИП |

X1 |

|

X2 |

|

Y |

|

|

|

|

|

R |

|

|

|

|

|

|

|

|||||||

X1 VD1 |

|

|

|

|

|

|

- |

|

|

|||||||||

|

|

|

|

|

|

|

||||||||||||

|

|

VD3 VD4 |

Y |

|

0 |

|

|

0 |

|

0 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

X2 VD2 |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

|

1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

Рис. 169 |

|

|

|

|

Рис. 170 |

|||||||||

3.Схема И. Элементы И-НЕ и ИЛИ-НЕ реализуются подключением на выход диодной матрицы транзисторного инвертора. R >> Rпр.

X1 |

X2 |

Y |

"1" |

|

R |

+ |

0 |

0 |

0 |

SA1 X1 |

|

- ИП |

|

VD1 |

VD3 |

VD4 Y |

||||

0 |

1 |

0 |

|

|

|

|

1 |

0 |

0 |

X2 |

VD2 |

|

|

1 |

1 |

1 |

|

|

||

|

|

|

|

|

|

Рис. 171 |

|

|

|

|

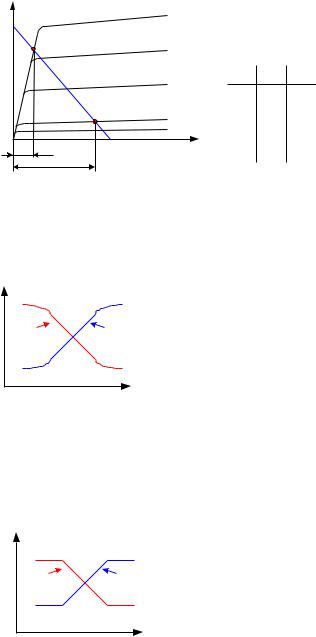

4. |

Исключающее ИЛИ. |

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

R1 |

R2 |

-Uип |

|

|

|

|

|

Y |

Iб |

Iкэ=0 |

Iкэ>0 |

|

|

|

VT3 |

|

|

|

X1 |

VT1 |

X2 |

|

|

|

|

|

|

VT2 |

|

|

|

|

|

|

|

|

|

Рис. 173 |

Uбэ |

|

|

Рис. 172 |

|

|

|

|

|

|

|

|

|

|

|

База каждого из входных транзисторов VT1, VT2 соединена с эмиттером другого транзистора. На транзисторе VT3 собран инвертор, или транзисторный ключ.

Е. А. Москатов. Стр. 71

Iк |

|

Iб4=max |

|

|

|

|

Iк.нас |

|

|

|

|

|

|

Р.Т.нас |

|

Iб3 |

|

|

|

|

|

|

Iб2 |

X1 |

X2 |

Y |

|

|

|

|

|

|

||

|

Р.Т.отс |

Iб1 |

0 |

0 |

0 |

|

|

1 |

0 |

1 |

|||

|

|

Iб=0 |

||||

|

|

0 |

1 |

1 |

||

Uкэ.нас |

Uип |

E к |

||||

1 |

1 |

0 |

||||

Uкэ.отс |

||||||

|

|

|||||

|

Рис. 174 |

|

Рис. 175 |

|||

3) Характеристики и параметры цифровых ИМС.

Кхарактеристикам цифровых ИМС относятся:

Входные характеристики (смотрите рисунок 176) – это зависимость входного тока Iвх ИМС от величины входного напряжения. Iвх = f (Uвх).

Iвх |

|

1 |

2 |

|

Uвх |

|

Рис. 176 |

Кривая 1 – для ИМС, у которых входной ток максимален при логическом нуле на входе. Кривая 2 – это характеристика ИМС, у которых входной ток максимален при логической единице на входе.

Передаточные характеристики. Это зависимость выходного напряжения ИМС от входного (смотрите рисунок 177).

Uвых |

|

1 |

2 |

|

Uвх |

|

Рис. 177 |

Кривая 1 – для ИМС с инверсией. Кривая 2 – для ИМС без инверсии.

Параметры ИМС.

Параметры ИМС подразделяются на две группы – статические и динамические.

1] Статические параметры характеризуют работу ИМС при статических 0 или 1 на входе и выходе.

Кстатическим параметрам относятся:

1.Напряжение источника питания Uип.

2.Входные и выходные напряжения логического нуля и логической единицы: Uвх0, Uвх1, Uвых0, Uвых1.

3.Входные и выходные токи логического нуля и логической единицы: Iвх0, Iвх1, Iвых0, Iвых1.

4.Коэффициент разветвления показывает количество входов микросхем нагрузок, которые можно подключить к данной микросхеме без потери её работоспособности (характеризует нагрузочную способность ИМС): Кр.

Е.А. Москатов. Стр. 72

5.Коэффициент объединения по входу Коб показывает, количество входов микросхемы, по которым реализуется выполняемая ею функция.

6.Напряжение статической помехи – это максимально допустимое статическое напряжение на входе, при котором микросхема не теряет свой работоспособности. Характеризует помехоустойчивость ИМС. Обозначение: Uст.п.

7.Средняя потребляемая мощность от источника питания Pпот.ср.

Pпот.ср |

P0пот. P1пот. |

|

2 |

||

|

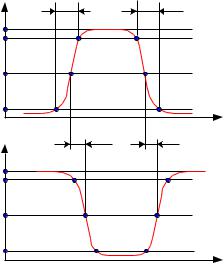

2] Динамические характеристики. Они характеризуют работу ИМС в момент переключения из нуля в единицу или из единицы в ноль.

Uвх |

t01 |

t10 |

|

|

|

|

|

Uвх |

|

|

|

0,9 Uвх |

|

|

|

0,5 Uвх |

|

|

|

0,1 Uвх |

|

|

|

|

t01зад. |

t10зад. |

t |

Uвы х |

|

|

|

Uвы х |

|

|

|

0,9 Uвых |

|

|

|

0,5 Uвых |

|

|

|

0,1 Uвых |

|

|

|

|

Рис. 178 |

|

t |

|

|

|

1.Время переключения из логического нуля в логическую единицу t01 – это время, за которое напряжение на входе или выходе возрастает от 0,1 до 0,9 уровня логической единицы (смотрите рисунок 178).

2.Время переключения из логической единицы в логический ноль t10.

3.Время задержки распространения сигнала при переключении из нуля в единицу. Обозначение: t01зад.

4.Время задержки распространения сигнала при переключении из логической единицы в логический ноль. Обозначение: t10зад.

5.Среднее время задержки распространения сигнала, характеризует быстродействие ИМС. Обозначение: tзад.ср.

tзад.ср |

t01зад t10 |

зад |

2 |

|

|

|

|

Транзисторно-транзисторная логика

1)Основные типы логики и понятие о многоэмиттерном транзисторе.

2)Транзисторно-транзисторная логика (ТТЛ) с простым инвертором.

3)ТТЛ со сложным инвертором.

1) Основные типы логики и понятие о многоэмиттерном транзисторе. Существует много разновидностей логики:

ТЛНС – транзисторная логика с непосредственными связями.

РТЛ – резисторно-транзисторная логика.

Е. А. Москатов. Стр. 73

РЕТЛ – резисторно-ёмкостная транзисторная логика.

ДТЛ – диодно-транзисторная логика.

Косновному типу логики относят ТТЛ. Разновидности:

ТТЛШ – транзисторно-транзисторная логика с переходами Шоттки.

ЭСЛ – эмиттерно-связная логика.

КМОП – логика на полевых МОП - транзисторах, состоящая из комплементарных пар.

|

|

R1 |

+Uип1 |

R2 |

+Uип2 |

"1" |

|

|

- |

|

- |

|

|

|

|

|

|

X1 |

|

|

|

|

Y |

VD1 |

VD3 |

VD4 |

VT1 |

|

|

|

|

||||

|

|

|

|

|

|

X2 |

VD2 |

|

|

|

|

|

|

|

|

|

Рис. 179

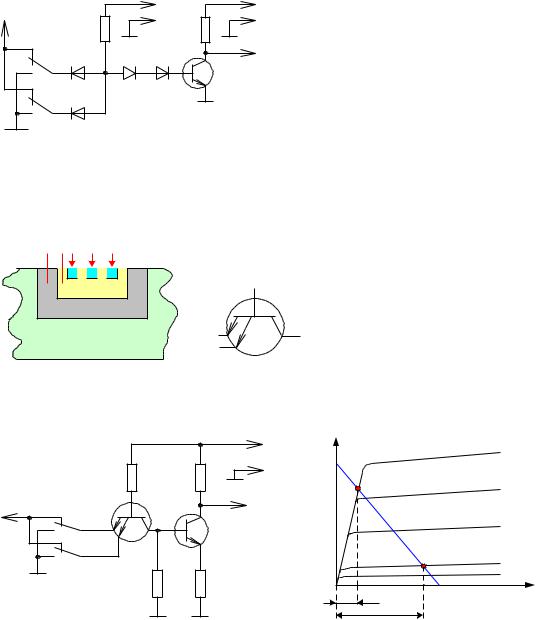

В ТТЛ операцию «И» выполняет многоэмиттерный транзистор, в котором функции диодов VD1 и VD2 выполняют эмиттерные переходы транзистора, а функции диодов VD3, VD4 выполняет коллекторный переход транзистора (смотрите рисунок 179).

Структура многоэмиттерного транзистора показана на рисунке 180, а УГО – на 181.

КБ Э1 Э2 Э3

n

n

n

n

n

p

p

n

Подложка "р"

Рис. 180

|

p |

n |

n |

n |

Рис. 181 |

|

2) Транзисторно-транзисторная логика с простым инвертором.

|

|

|

|

+ |

Iк |

|

Iбmax |

|

|

|

|

Uип |

|

||

|

|

R1 |

R3 |

Iк.нас |

|

|

|

|

|

- |

|

|

|||

|

|

Р.Т.нас |

|

Iб3 |

|||

|

|

|

|

|

|||

|

|

|

|

|

|

||

"1" |

X1 |

VT1 |

|

Y |

|

|

|

|

|

|

|

Iб2 |

|||

|

|

VT2 |

|

|

|

||

|

|

|

|

|

|

||

|

X2 |

|

|

|

|

Р.Т.отс |

Iб1 |

|

|

R2 |

R4 |

|

|

||

|

|

|

|

|

Iб=0 |

||

|

|

|

|

|

U0вых |

Uип |

Uкэ |

|

|

|

|

|

U1вых |

||

|

|

|

|

|

|

|

|

|

|

Рис. 182 |

|

|

|

Рис. 183 |

|

X1 |

|

X2 |

|

Y |

|

|

|||

|

|

|

|

|

0 |

|

0 |

|

1 |

0 |

|

1 |

|

1 |

1 |

|

0 |

|

1 |

1 |

|

1 |

|

0 |

|

|

Рис. 184

Принцип действия.

Если хотя бы на один из входов будет подаваться сигнал логического нуля, соответствующий эмиттерный переход транзистора VT1 будет открыт, и через него будет протекать ток от плюса источника питания (ИП), через резистор R1, база-эмиттер VT1, общий провод, минус источника питания. В цепи коллектора VT1, а следовательно, и в цепи базы VT2, ток будет отсутствовать, транзистор VT2 будет находиться в режиме отсечки, на выходе будет высокий уровень напряжения логической единицы. При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса ИП, через R1, базаколлектор VT1 и на базу VT2. Транзистор VT2 перейдёт в режим насыщения и на выходе установится низкий уровень напряжения логического нуля.

Недостатком ТТЛ с простым инвертором является маленький коэффициент разветвления.

Е. А. Москатов. Стр. 74

3) ТТЛ со сложным инвертором.

+

+

R1 R2 R4 Uип

-

-

"1" |

|

VT1 |

VT3 |

|

X1 |

VT2 |

|

|

|

|

VD1 |

|

||

|

X2 |

|

Y |

|

|

|

|

|

|

|

|

|

VT4 |

|

|

|

|

R3 |

|

|

|

Рис. 185 |

|

|

X1 X2 Y

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

Рис. 186 |

|

Если хотя бы на одном из входов будет действовать логический ноль, соответствующий эмиттерный переход будет открыт, и через него будет протекать ток по цепи от плюса ИП, через R1, база-эмиттер VT1, общий провод, минус ИП. В цепи коллектора VT1, а следовательно, и в цепи базы VT2 ток будет отсутствовать, VT2 будет находиться в режиме отсечки, ток через транзистор VT2, а значит, ток базы VT4 будут близки к нулю. Транзистор VT4 также будет находиться в режиме отсечки, и на выходе будет высокий уровень напряжения логической единицы. При этом напряжение на коллекторе VT2 и на базе VT3, будет максимальным, и VT3 будет находиться в полностью открытом состоянии.

При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса ИП, через R1, переход база-коллектор VT1 на базу VT2. Транзистор VT2 перейдёт в режим насыщения. Ток через него, а следовательно, и ток базы VT4 будет максимальным, и транзистор VT4 перейдёт в режим насыщения. На выходе будет низкий уровень логического нуля. При этом напряжение на коллекторе VT2 и на базе VT3 будет близко к нулю и VT3 перейдёт в полностью закрытое состояние. Диод VD1 применяется для более надёжного запирания транзистора VT3.

Логические элементы ТТЛ со специальными выводами

1)ТТЛ с открытым коллектором.

2)ТТЛ с Z-состоянием.

3)ТТЛШ.

4)Оптоэлектронные ИМС.

1) ТТЛ с открытым коллектором. Следующая схема получила своё название за счёт того, что коллектор выходного транзистора не подключён ни к одной точке схемы. Поэтому для обеспечения работоспособности между выходом и плюсом ИП необходимо подключить внешнее навесное сопротивление (смотрите рисунки 187, 188).

|

|

|

+ |

|

|

+ |

|

|

|

Uип |

|

|

|

|

R1 |

R2 |

- |

|

R1 |

Uип |

|

|

Rвн |

|

|

|

- |

"1" |

VT1 |

Y |

|

|

|

|

X1 |

VT2 |

|

|

DD1 |

VD1 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

X2 |

VT3 |

|

X1 |

& |

|

|

|

|

|

|

||

|

|

R3 |

|

X2 |

|

|

|

|

|

|

|

|

|

|

Рис. 187 |

|

|

|

Рис. 188 |

|

Е. А. Москатов. Стр. 75