Материал: 2416

|

|

|

|

|

|

|

|

|

|

4 |

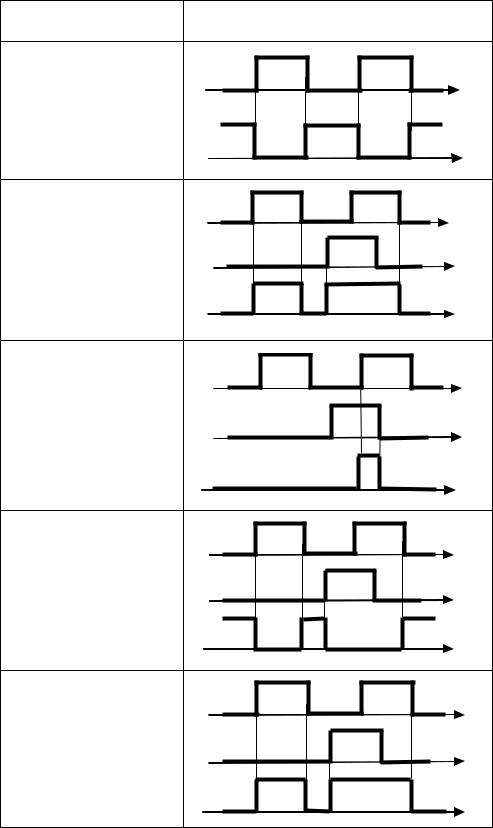

Окончание табл. 10.6 |

|||||||

1 |

2 |

|

|

|

3 |

|

|

|

|

|

5 |

|

||||||

|

Отрицание |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

X1 |

& |

Y |

|

|

|

|

|

|

0 |

0 |

1 |

||||

|

логического |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

И-НЕ |

|

|

X2 |

|

|

|

|

|

|

|

|

0 |

1 |

1 |

||||

умножения, |

|

|

|

|

|

|

|

Y = X1 X 2 |

||||||||||

|

штрих |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Шеффера |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Исклю- |

Сложение по |

|

|

X1 |

|

|

|

|

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

=1 |

Y |

|

|

|

|

|

|

0 |

0 |

0 |

||||||

чающее |

модулю 2, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

X2 |

|

|

Y = X1 |

X 2 |

0 |

1 |

1 |

|||||||||

ИЛИ |

неравнознач- |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

1 |

0 |

1 |

||||||||||

|

|

|

|

|

|

|

|

|||||||||||

|

ность |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Исклю- |

Эквивалент- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

X1 |

|

=1 |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

||

чающее |

ность, |

|

|

|

Y |

Y = X1 |

Х2 |

|||||||||||

|

|

|

|

|

|

|

|

|||||||||||

|

|

X2 |

|

|

0 |

1 |

0 |

|||||||||||

ИЛИ-НЕ |

равнозначность |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

X |

Х |

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

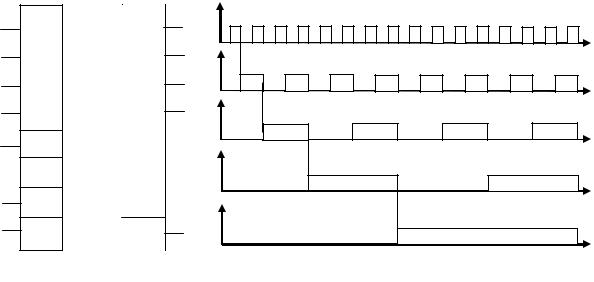

Логические элементы выполняют, как правило, в виде интегральных микросхем, каждый корпус которых может содержать несколько логических элементов. Логические элементы могут работать в режимах положительной и отрицательной логики. В режиме положительной логики логической единице соответствует высокий уровень напряжения, а логическому нулю – низкий уровень напряжения. В режиме отрицательной логики логической единице соответствует низкий уровень напряжения, а логическому нулю – высокий. Временные диаграммы логических элементов приведены в табл. 10.7.

Для контактно-релейных схем в режиме положительной логики логической единице соответствует замкнутый контакт ключа или реле, а логическому нулю – разомкнутый. Светящийся индикатор (лампочка, светодиод) соответствует логической единице, а несветящийся

– логическому нулю.

Как правило, паспортное обозначение логического элемента соответствует функции, реализуемой положительной логикой. Логическая функция может быть задана таблицей, которая называется таблицей истинности. Число строк в таблице – это число возможных наборов значений аргументов. Оно равно 2n, где n – число переменных.

287

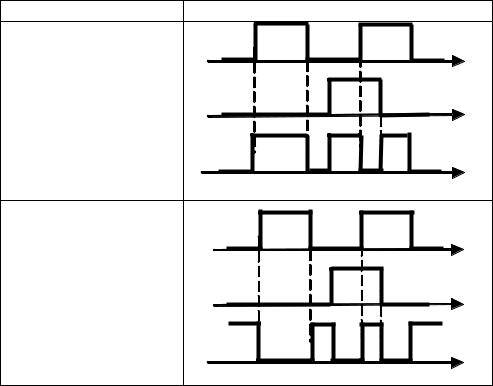

Таблица 10.7

Временные диаграммы логических элементов

Логический элемент |

Временная диаграмма |

1 |

2 |

X |

t |

НЕ |

Y |

t |

|

X1 |

t |

X2 |

t |

ИЛИ |

|

Y |

t |

X1 |

t |

И |

X2 |

t |

|

|

|

|

Y |

t |

X1 |

t |

ИЛИ-НЕ |

X2 |

t |

|

Y |

t |

X1 |

t |

X2 |

t |

И-НЕ |

|

Y |

t |

288

|

|

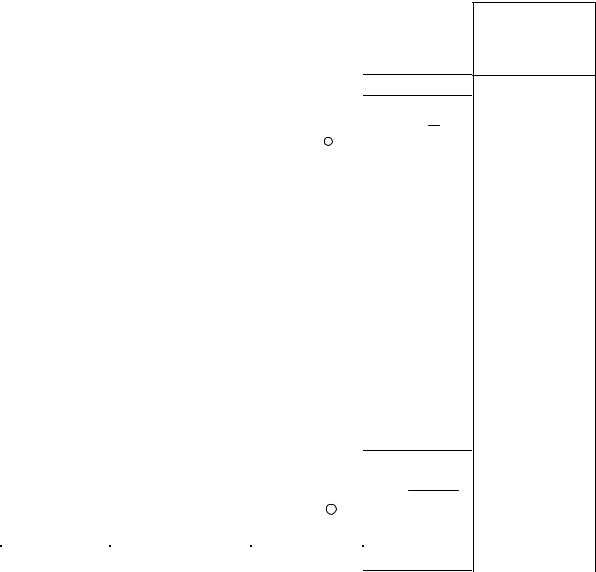

Окончание табл. 10.7 |

1 |

|

2 |

|

X1 |

t |

Исключающее |

X2 |

t |

ИЛИ |

|

|

|

Y |

t |

X1 |

t |

Исключающее |

X2 |

t |

ИЛИ-НЕ |

Y |

t |

Логические элементы представляют собой комбинационные схемы. В комбинационных схемах состояние на выходе в данный момент времени однозначно определяется состояниями на входах в тот же момент времени.

На базе логических элементов построены такие устройства, как шифраторы, дешифраторы, мультиплексоры, демультиплексоры, сумматоры.

Шифратор (кодер) преобразует сигнал на одном из его входов в n-разрядное двоичное число. При появлении сигнала логической единицы на одном из десяти входов на четырех выходах шифратора будет присутствовать соответствующее двоичное число.

Дешифратор (декодер) преобразует код, поступающий на его n- входов, в сигнал логической единицы только на одном из его выходов. Дешифратор n-разрядного двоичного числа имеет 2n выходов.

Различные типы дешифраторов применяются в схемах цифровой индикации информации. Особенно широко применяются дешифраторы, преобразующие информацию в код для семисегментных индикаторов.

Условные обозначения и таблицы истинности шифратора и дешифратора приведены соответственно в табл. 10.8 и 10.9.

289

C

C