Материал: 2416

– запуск импульсами одинаковой полярности одновременно на базы обоих транзисторов (счетный запуск).

Простейшей запускающей цепью является дифференцирующая RC-цепь, формирующая короткий импульс, который через диод поступает на базу транзистора.

На рис. 10.53, а приведена схема с раздельным запуском, которая имеет два входа. При этом положительный запускающий импульс подается раздельно на вход uвх1 через дифференцирующую цепь Rвх1Свх1, диод VD1 на базу транзистора VT1 или на вход uвх2 через дифференцирующую цепь Rвх2Свх2, диод VD2 на базу транзистора VT2 (см. рис. 10.53, а, б).

Как установлено выше, триггер находится в одном из двух устойчивых состояний, при котором транзистор VT1 открыт, а транзистор VT2 закрыт. Чтобы перевести триггер в другое устойчивое состояние, необходимо подать положительный импульс на вход uвх1 через дифференцирующую цепь Rвх1Свх1, диод VD1 на базу открытого транзистора VT1, что приводит к его запиранию. Запирание VT1 вызовет описанный выше лавинообразный процесс, в результате которого VT2 будет открыт, а VT1 закрыт. Новое состояние в отсутствие внешних запускающих импульсов будет также устойчивым.

Если запускающий положительный импульс подать на базу закрытого транзистора, то состояние триггера не изменится. Если диоды включить в противоположном направлении, то на базы транзисторов будут поступать отрицательные импульсы, которые открывают транзисторы. На состояние открытого транзистора эти импульсы влиять не будут, а закрытый транзистор начнет открываться.

В практических схемах диоды включаются таким образом, чтобы запускающий импульс работал на закрывание транзистора, так как в этом случае потребляется меньший ток от источника импульса.

Симметричный триггер с раздельным запуском (рис. 10.50, а), представляет собой RS-триггер.

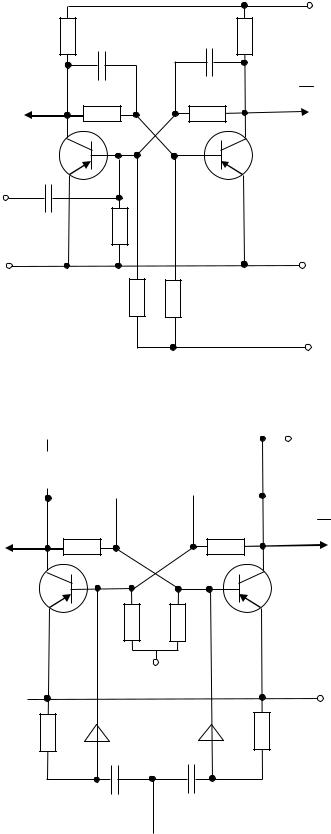

На рис. 10.54 приведена схема триггера с запуском импульсами чередующейся полярности, подаваемыми на базу одного транзистора. Так как импульсы имеют разную полярность, диод в цепи запуска такого триггера отсутствует.

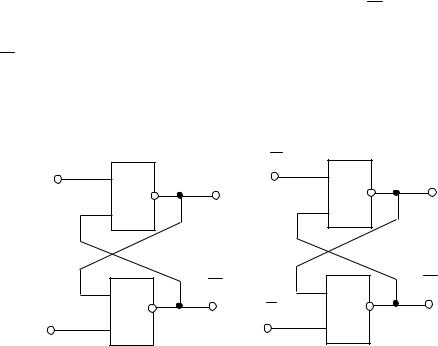

На рис. 10.55 приведена схема триггера со счетным входом. Для получения такого триггера входные цепи триггера с раздельным запуском объединяются. Полученный общий вход называется счетным входом, или Т-входом. Сам триггер называется Т-триггером.

275

Rк1 |

|

|

–Ек |

Скб1 |

Скб2 |

Rк2 |

|

|

|

||

Q |

Rб2 |

Rб1 |

Q |

uвых1 |

|

|

uвых2 |

VT1 |

|

|

VT2 |

Свх |

|

|

|

uвх |

Rвх |

|

|

|

|

|

|

|

RЗ1 |

RЗ2 |

0 |

|

|

+Еб

Рис. 10.54. Триггер с запуском импульсами чередующейся полярности, подаваемыми на базу одного транзистора

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–Ек |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rк1 |

|

|

|

|

|

Скб1 |

Скб2 |

|

|

|

|

Rк2 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

Rб2 |

Rб1 |

Q |

uвых1 |

|

|

uвых2 |

VT1 |

|

|

VT2 |

RЗ1  RЗ2

RЗ2

+Еб

0

Rвх1 |

|

VD1 VD2 |

|

Rвх2 |

|

|

Свх1 Свх2  Т

Т  uвх

uвх

Рис. 10.55. Триггер со счетным входом

276

В этой схеме на катоды диодов через сопротивления Rб1, Rб2 подается высокое отрицательное напряжение, в результате чего один из диодов всегда будет закрыт. Запускающий импульс поступит через диод, подключенный к базе открытого транзистора, который начнет закрываться. Если, например, закрыт транзистор VT1, будет закрыт диод VD1, подключенный к базе VT1, запускающий импульс поступит на базу VT2, в результате чего триггер перейдет в другое устойчивое состояние, когда будет закрыт VT2.

Т-триггер является делителем частоты входных импульсов на 2.

10.19.3. Триггеры на интегральных микросхемах

RS-триггер

Асинхронный RS-триггер имеет два информационных входа R и S. Входы S и R названы по первым буквам английских слов set – установка и reset – сброс. При S=1 и R=0 на выходах триггера появляются сигналы: на прямом выходе Q=1, на инверсном Q =0. При S=0 и R=1

выходные сигналы триггера принимают противоположные состояния (Q=0, Q =1). Этот триггер не имеет тактового входа. Простейший RS-

триггер можно реализовать на логических элементах ИЛИ-НЕ и И-НЕ, как показано на рис. 10.56.

R |

1 |

Q |

R |

Q |

|

& |

1 |

Q |

& |

Q |

S |

|

S |

|

а |

|

б |

|

Рис. 10.56. RS-триггер, реализованный на логических элементах ИЛИ-НЕ (а) и И-НЕ (б)

Схемное обозначение и таблица истинности, поясняющая алгоритм функционирования асинхронного RS-триггера, приведены в табл. 10.3.

277

Таблица 10.3

Схемное обозначение

и таблица истинности асинхронного RS-триггера

|

|

Схемное |

|

|

|

|

Входные |

|

Состояние |

||||||

|

обозначение |

|

|

|

|

сигналы |

|

|

выхода |

||||||

|

|

|

|

|

|

|

|

|

|

R |

|

S |

Q(t) |

|

Q(t+1) |

|

|

|

|

|

|

Q |

0 |

|

0 |

0 |

|

0 |

|||

|

|

|

T |

|

|

|

|||||||||

|

|

R |

|

|

|

|

|

0 |

|

0 |

1 |

|

1 |

||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

1 |

|

1 |

|

|

S |

|

|

|

Q |

|

|

|||||||

|

|

|

|

|

|

|

|

|

1 |

|

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

0 |

|

Не |

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

1 |

|

определено |

RS-триггер не допускает одновременно наличие на входах активных сигналов «S=1, R=1». В этом случае не выполняется условие его функционирования, поскольку на выходах Q и Q логические уровни

перестают быть взаимно инверсными, состояние выхода оказывается неопределенным. Данные комбинации считаются запрещенными.

Режим «S=1, R=0» называют режимом записи «1», так как Q(t+1)=1; режим «S=0 и R=1» – режимом записи «0», так как Q(t+1)=0; режим «S=0, R=0» – режимом хранения информации, так как информация на выходе остается неизменной. Временная диаграмма асинхронного RS-триггера приведена на рис. 10.57.

R

t

t

S

t

t

Q

t

t

Рис. 10.57. Временная диаграмма асинхронного RS-триггера

Синхронный RS-триггер отличается от асинхронного наличием входа С для синхронизирующих тактовых импульсов. Переключение

278