Материал: 2416

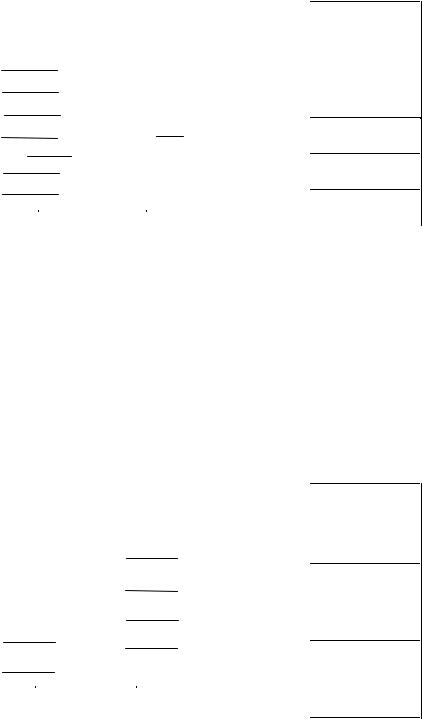

Таблица 10.8

Условное обозначение и таблица истинности шифратора

|

Условное обозначение |

«1» на |

|

Выходы |

|

||||||||||||

|

|

|

|

|

|

|

|

шифратора |

входе |

1 |

2 |

4 |

8 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

0 |

CD |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

1 |

0 |

0 |

0 |

1 |

||||||||||||

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

1 |

|

|

2 |

0 |

0 |

1 |

0 |

||||||

|

|

|

|

|

|

|

|

2 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

3 |

|

2 |

|

|

3 |

0 |

0 |

1 |

1 |

||||

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

|||||

|

|

|

|

4 |

|

|

|||||||||||

|

|

|

5 |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

5 |

0 |

1 |

0 |

1 |

||||||||||

|

|

|

|

|

|

|

|

6 |

|

8 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

6 |

0 |

1 |

1 |

0 |

||||||||||

|

|

|

|

|

|

|

|

7 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

8 |

|

|

|

|

7 |

0 |

1 |

1 |

1 |

||||||

|

|

|

|

|

|||||||||||||

|

|

9 |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

8 |

1 |

0 |

0 |

0 |

|||||||||

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

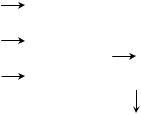

Таблица 10.9

Условное обозначение и таблица истинности дешифратора

Условное обозначение |

|

Входы |

|

«1» на |

|||||||||||

|

|

|

|

дешифратора |

1 |

2 |

4 |

8 |

выходе |

||||||

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

DC |

0 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 |

0 |

1 |

0 |

2 |

|||||||||||

|

|

|

|

|

|

1 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

1 |

|

2 |

|

|

|

|

0 |

|

|

|

|

0 |

1 |

1 |

3 |

||||||||||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

0 |

1 |

0 |

0 |

4 |

|||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

4 |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

0 |

1 |

0 |

1 |

5 |

|||||

|

|

4 |

|

5 |

|

|

|

||||||||

|

|||||||||||||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

8 |

|

6 |

|

|

|

0 |

1 |

1 |

0 |

6 |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|||||||||||

|

|

7 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

7 |

||

|

|

|

|

|

|

8 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

1 |

0 |

0 |

0 |

8 |

|||||

|

|

|

|

|

|

9 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

9 |

||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Мультиплексор – это устройство, обеспечивающее соединение одного из информационных входов с выходом. Номер информационного входа, который соединяется с выходом, задается в двоичном коде на адресных входах. Если мультиплексор имеет n адресных входов, то в нем может быть 2n информационных входов.

290

Мультиплексор позволяет передавать по одной коммуникационной линии или каналу одновременно несколько различных потоков данных.

Таблица 10.10

Условное обозначение и таблица истинности мультиплексора

Условное обозначение |

Адрес |

На выход Q |

||||||||

|

мультиплексора |

|

|

передается |

||||||

|

|

|

|

|

|

|

|

А0 |

А1 |

информация |

|

|

D0 |

MX |

|

|

|

|

|||

|

|

|

|

|

|

|

|

со входа |

||

|

|

D1 |

|

|

|

|

|

0 |

0 |

D0 |

|

|

D2 |

|

Q |

|

|

|

|

|

D1 |

|

|

|

|

0 |

1 |

|||||

|

|

D3 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

D2 |

|

|

A0 |

|

|

|

|

|

1 |

0 |

|

|

|

A1 |

|

|

|

|

|

|

|

D3 |

|

|

|

|

|

1 |

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

Демультиплексор – это устройство, обеспечивающее соединение одного из информационных выходов с одним входом. Номер информационного выхода, который соединяется с входом, задается в двоичном коде на адресных входах. Если демультиплексор имеет n адресных входов, то в нем может быть 2n информационных выходов.

Таблица 10.11

Условное обозначение и таблица истинности демультиплексора

|

Условное обозначение |

Адрес |

Информация |

|||||||

|

демультиплексора |

|

|

со входа D |

||||||

|

|

|

|

|

|

|

|

А0 |

А1 |

передается |

|

|

|

|

DMX |

Q |

0 |

|

|

|

на выход |

|

|

|

D |

|

Q |

1 |

|

0 |

0 |

Q0 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Q |

2 |

|

0 |

1 |

Q1 |

|

|

|

A0 |

|

Q |

|

|

|

|

Q2 |

|

3 |

|

1 |

0 |

||||||

|

|

|

A1 |

|

|

|||||

|

|

|

|

|

|

|

|

|

Q3 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

291

Условные обозначения и таблицы истинности мультиплексора и демультиплексора приведены соответственно в табл. 10.10 и 10.11.

Разновидностью логического элемента «Исключающее ИЛИ» является сумматор. Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение.

При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в ариф- метико-логических устройствах, ядром которых являются сумматоры. Сумматор – логический операционный узел, выполняющий арифметическое сложение двух чисел.

Одноразрядный двоичный сумматор (С) – это устройство с тремя входами и двумя выходами, работа которого может быть описана таблицей истинности. Схемное обозначение сумматора и его таблица истинности приведены в табл. 10.12.

Многоразрядный сумматор для поразрядного сложения обычно состоит из соответствующим образом соединенных одноразрядных сумматоров.

Таблица 10.12

Схемное обозначение сумматора и его таблица истинности

|

Схемное |

|

Входы |

|

Выходы |

||||||

|

Разряд |

Разряд |

Перенос |

|

Перенос в |

||||||

|

обозначение |

из преды- |

|

||||||||

|

первого |

второго |

|

следую- |

|||||||

|

сумматора |

дущего |

Сумма S |

||||||||

|

|

|

|

|

|

|

слагае- |

слагае- |

разряда |

|

щий раз- |

|

|

|

|

|

|

|

мого A |

мого B |

|

ряд ПВЫХ |

|

|

|

|

|

|

|

|

ПВХ |

|

|||

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

|

|

|

ПС |

|

|

|

0 |

1 |

0 |

1 |

0 |

|

А |

|

С |

|

|

|

|||||

|

В |

|

|

|

|

|

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

ПВЫХ |

|

|

1 |

0 |

0 |

1 |

0 |

||||

|

ПВХ |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

|

|

1 |

0 |

1 |

0 |

1 |

|||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

292 |

|

|

|

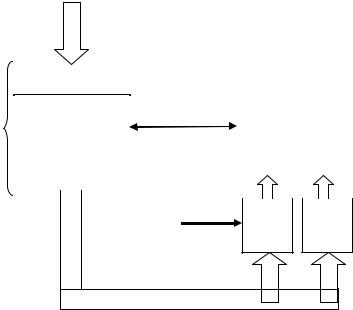

Упрощенная блок-схема МП (рис. 10.67, б) состоит из АЛУ и совокупности n параллельных регистров общего назначения (РОН) по m разрядов каждый для хранения двоичных чисел, используемых в процессе вычислений.

Всостав МП входят также два параллельных буферных регистра (БР), предназначенных для кратковременного хранения чисел А и В во время выполнения операции АЛУ, и устройство управления (УУ), которое задает режим работы всех элементов МП.

При работе МП числа А и В, над которыми выполняются операция, передаются по магистрали последовательно из РОН на буферные регистры БРА и БРВ. Затем АЛУ по команде производит указанную операцию, а результат ее по внутренней магистрали передается в РОН. Обычно для этой цели выделяется специальный регистр РОН, называемый аккумулятором, в котором ранее записанное число стирается. Например, сложение трех чисел выполняется таким образом: сначала складываются два первых числа и результат записывается в РОН. Затем в АЛУ поступают результат этого сложения и третье число, вычисляется окончательный результат и записывается в РОН.

Последовательность выполнения операций практически не ограничивает функциональные возможности МП. Однако эффективность применения МП значительно возрастает, если его снабдить дополнительными устройствами для хранения информации и обмена ею с внешними устройствами.

МикроЭВМ – это устройства на основе МП, а также запоминающих устройств (ЗУ), УУ и средств связи с периферийными устройствами (интерфейс). Управляющая микроЭВМ должна иметь средства сопряжения с объектом управления: датчики, АЦП, ЦАП. Совокупность микроЭВМ и средств сопряжения образует микропроцессорную систему.

Блок-схема микроЭВМ (рис. 10.68) содержит устройства ввода (УВВ) и вывода (УВЫВ), порты ввода и вывода, центральный МП с АЛУ, устройством управления и регистрами общего назначения, а также постоянные запоминающие устройства (ПЗУ) и оперативные запоминающие устройства (ОЗУ).

Вкачестве УВВ служат клавиатура, АЦП, различные носители информации (флэш-карты, диски и т.п.), в качестве УВЫВ – дисплеи, печатающие устройства, ЦАП и т.п. Порты ввода и вывода предназначены для кратковременного хранения информации в процессе ввода, вывода.

294