Материал: TOE-RGR-2014

16

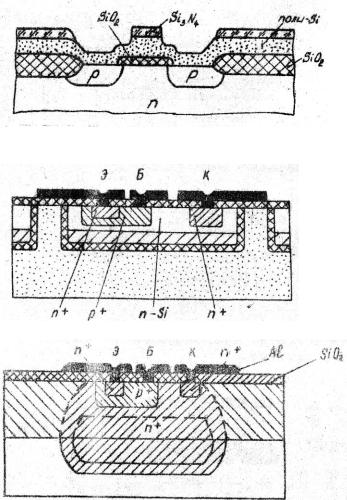

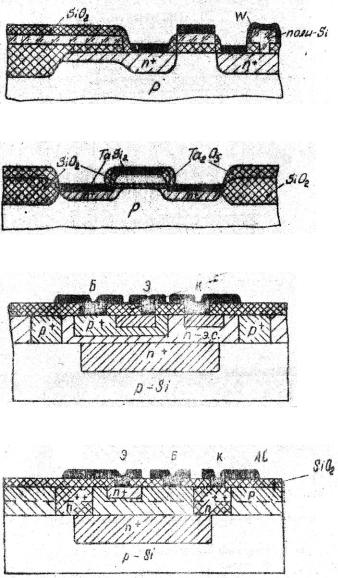

Рис 2.4. Модифікована МДН-технологія зі зменшеним рельєфом поверхні

Рис 2.5. Повна діелектрична ізоляція(EPIK-процес)

Рис 2.6. Самоізоляція за допомогою n-області

17

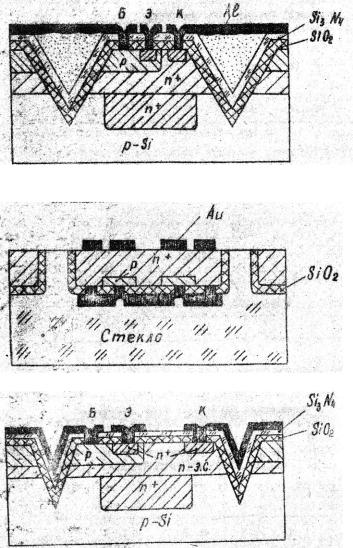

Рис 2.7. Структура n-p-n транзистора, виготовленого за V- технологією

Рис 2.8. Структура p-n-p транзистора

Рис 2.9. Структура n-p-n транзистора, виготовленого за V-АТБ- технологією

18

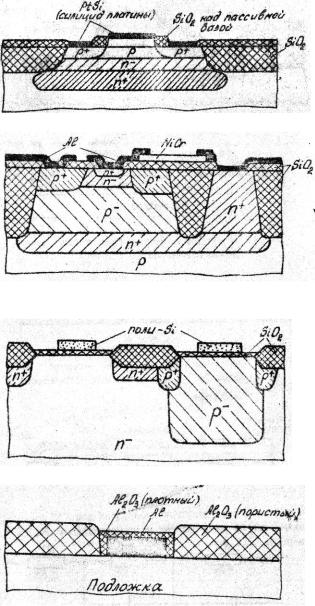

Рис 2.10. Фрагмент структура p-n-p транзистора

Рис 2.11. Cтруктура біполярного n-p-n- транзистора

Рис 2.12. Фрагмент КМДН-структури

Рис 1.13. Структура струмопровідної системи на основі Al , одержана методом електролітичного анодування

19

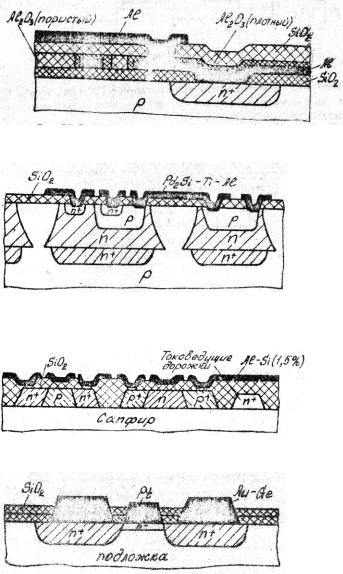

Рис 2.14. Дворівнева струмопровідна система на основі Al та його анодних плівок з додатковим захистом шаром SiO2

Рис 2.15. Cтруктура біполярного транзистора з резистором суміщення

Рис 2.16. Структура КМДН-транзистора на сапфіровій підкладці

Рис 2.17. Польовий транзистор з барєром Шотткі на арсеніді галлію

20

Рис 2.18. Фрагмент МОН-структури

Рис 2.19. Фрагмент МОН-структури

Рис 2.20. Структура з роздільною дифузією в епітаксіальний шар

Рис 2.21. Структура з колекторною ізолюючою дифузією