Материал: TOE-RGR-2014

6

14.Ефимов И.Е. Основы микроэлектроники /. И.Е. Ефимов, И.Я Козырь. - Москва: Высшая школа, 1983. – 384 с.

15.Пасынков В.В. Материалы электронной техники / В.В. Пасынков. - Москва: Высшая школа, 1980. – 406 с.

16.Курносов А.И. Технология производства полупроводниковых приборов и интегральных мікросхем / А.И. Курносов, В.В. Юдин. - Москва: Высшая школа, 1986. – 368 с.

17.Черняев В.Н. Технология производства интегральных микросхем и микропроцессоров /В.Н.Черняев. - Москва: Радио и связь, 1987. - 464 с.

18.Тилл У. Интегральные схемы. Материалы, приборы, изготовление / У. Тилл, Дж. Мансон. - Москва: Мир, 1985.-501 с.

19.Моро У. Микролитография / У. Моро. - Москва: Мир, 1990.-

1240 с.

20.Борисенко А.С. Технология и оборудование для производства микроэлектронных устройств / А.С. Борисенко, Н.Н. Бавыкин. - Москва: Машиностроение, 1983.- 320 с.

21.Молекулярно-лучевая эпитаксия и гетероструктуры / Под.ред. Л. Ченга и К. Плота.- Москва: Мир, 1989.- 584 с.

22.Сугано Т., Введение в микроэлектронику / Т. Сугано, Т. Икома, Е.Такэиси. - Москва: Мир, 1988.- 320 с.

23.Медведев С.А. Введение в технологию полупроводниковых материалов / С.А. Медведев.- Москва: Высшая школа, 1970.-

504 с.

24.Федоров Л.П. Производство полупроводниковых приборов / Л.П Федоров., В.М. Багров, Ю.Н.Тихонов. - Москва: Энергия,

1979.- 432 с.

25.Опанасюк Н.М. Технологічні основи електроніки (практикуми): навчальний посібник / Н.М.Опанасюк, Л.В.Однодворець, А.О.Степаненко. - Суми: Сумський державний університет,

2013.- 102 с.

26.Проценко І.Ю. Методичні вказівки до лабораторних робiт із курсу "Технологiчнi основи електронiки" / І.Ю. Проценко, А.М. Чорноус, Л.В.Однодворець. – Суми: СумДУ, 1998.- 43с.

7

3 КОНТРОЛЬНІ ЗАВДАННЯ

3.1 Перелік контрольних питань та вправ

Завдання 1. Зобразити та описати послідовність формування наступних структур напівпровідникових мікросхем:

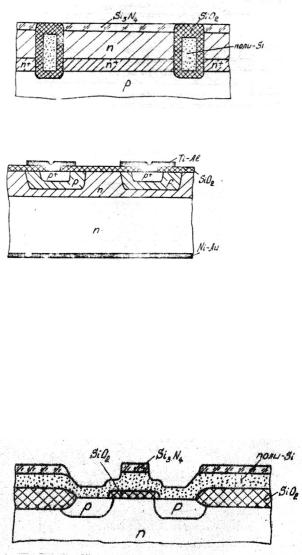

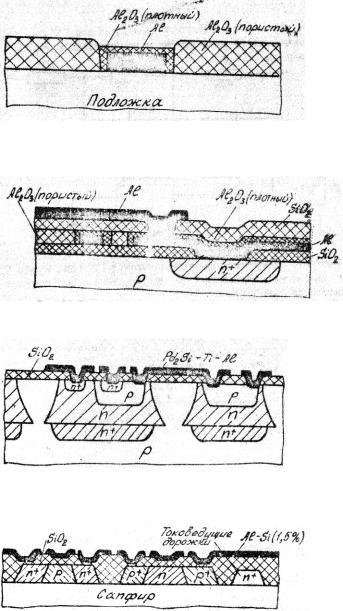

Рис 1.1. Комбінована ізоляція з використанням оксида кремнію та полікремнію

Рис 1.2. Епітаксійно-планарна діодна структура

0

0

Рис 1.3. Біполярний n-p-n-транзистор з діодом Шотткі

Рис 1.4. Модифікована МДН-технологія зі зменшеним рельєфом поверхні

8

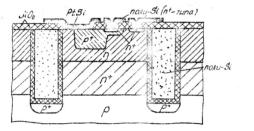

Рис 1.5. Повна діелектрична ізоляція(EPIK-процес)

Рис 1.6. Самоізоляція за допомогою n-області

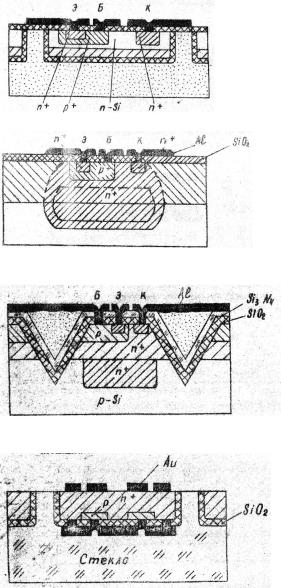

Рис 1.7. Структура n-p-n транзистора, виготовленого за V- технологією

Рис 1.8. Структура p-n-p транзистора

9

Рис 1.9. Структура n-p-n транзистора, виготовленого за V-АТБ- технологією

Рис 1.10. Фрагмент структура p-n-p транзистора

Рис 1.11. Cтруктура біполярного n-p-n- транзистора

Рис 1.12. Фрагмент КМДН-структури

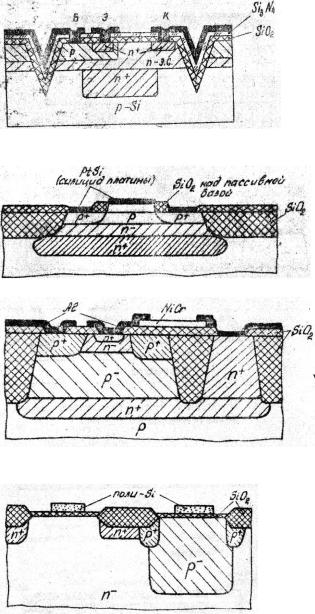

10

Рис 1.13. Структура струмопровідної системи на основі Al , одержана методом електролітичного анодування

Рис 1.14. Дворівнева струмопровідна система на основі Al та його анодних плівок з додатковим захистом шаром SiO2

Рис 1.15. Cтруктура біполярного транзистора з резистором суміщення

Рис 1.16. Структура КМДН-транзистора на сапфіровій підкладці