Материал: Захаров, Сайфутдинов - Вычислительная техника

Х3 Х2 Х1 |

|

|

& o Х2 Х1 |

|||

& oХ1 |

& o |

|||||

Х2 |

& o |

& |

Х2 Х1 |

|||

& o |

o |

|

|

|||

|

& o |

& |

Х |

Х |

|

|

& oХ3 |

o 2 |

|

1 |

|||

|

|

|

|

|

|

|

|

& |

o |

& |

Х2 Х1 |

||

|

|

|

o |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& o |

|

& o Y0 |

Х |

3 |

Х |

2 |

Х |

1 |

||

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

& o  & o Y1 Х3Х2Х1

& o Y1 Х3Х2Х1

& o  & o Y2 Х3Х2 Х1

& o Y2 Х3Х2 Х1

& o

& o Y3 Х3Х2 Х1

& o Y3 Х3Х2 Х1

&o

& oY4 Х3Х2 Х1

& oY4 Х3Х2 Х1

&o

& oY5 Х3Х2Х1

& oY5 Х3Х2Х1

& o

& o Y6 Х3Х2 Х1 & o

& o Y6 Х3Х2 Х1 & o

& o Y7 Х3Х2Х1

& o Y7 Х3Х2Х1

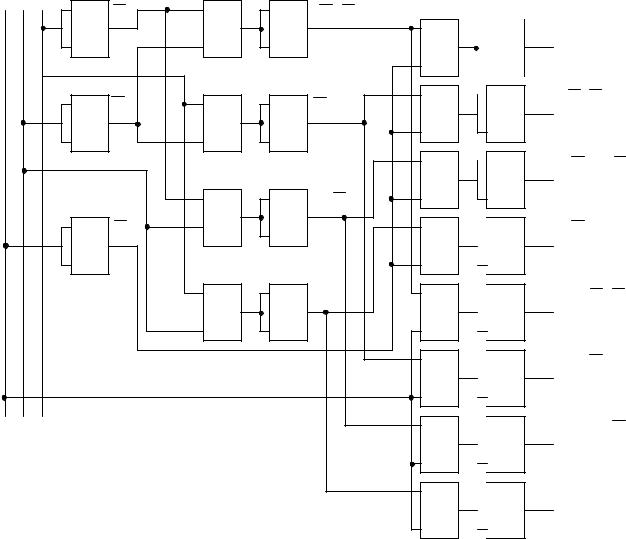

Рис. 3.8. Принципиальная схема пирамидального дешифратора

Дешифратор «открывает» соответствующий дешифратор второго каскада, подавая на инверсный вход С нулевой сигнал, а поскольку на прочих выходах DC формируется 1, все остальные дешифраторы второго каскада закрыты. На кодовые входы дешифраторов второго каскада поступают младшие разряды дешифрируемого кода. Причем работает единственный незакрытый дешифратор второго каскада, возбуждая в результате один из 16 выходов, соответствующий коду, поданному на вход.

61

|

|

|

|

|

|

|

|

Xc |

o С |

DC4 |

0 |

o |

|

||

|

|

|

|

1 |

o |

||

X3 |

|

1 |

|

||||

|

|

|

|

|

|

||

o |

|

2 |

o |

||||

X4 |

|

2 |

|

3 |

o |

|

|

|

|

|

|||||

o |

|

|

|||||

|

|

|

|

|

|

|

|

X1

X2

|

|

|

|

|

|

|

|

|

|

|

|

|

o С |

DC0 |

0 |

o |

|||

|

|

|

|

|

|

|

1 |

o |

|

|

|

|

|

|

1 |

|

|||

|

|

|

o |

|

2 |

o |

|||

|

|

|

|

||||||

|

|

|

|

|

2 |

|

3 |

o |

|

|

|

|

o |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

o С |

DC1 |

0 |

o |

|||

|

|

|

|

|

|

|

1 |

o |

|

|

|

|

|

|

1 |

|

|||

|

|

|

o |

|

2 |

o |

|||

|

|

|

|

|

2 |

|

3 |

o |

|

|

|

|

o |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

o С |

DC2 |

0 |

o |

|||

|

|

|

|

|

|

|

1 |

o |

|

|

|

|

|

|

1 |

|

|||

|

|

|

o |

|

2 |

o |

|||

|

|

|

o |

2 |

|

3 |

o |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

o С |

DC3 |

0 |

o |

|||

|

|

|

|

|

|

|

1 |

o |

|

|

|

|

|

|

1 |

|

|||

|

|

|

o |

|

2 |

o |

|||

|

|

|

|

||||||

|

|

|

|

|

2 |

|

3 |

o |

|

|

|

|

o |

|

|||||

|

|

|

|

|

|

|

|

|

|

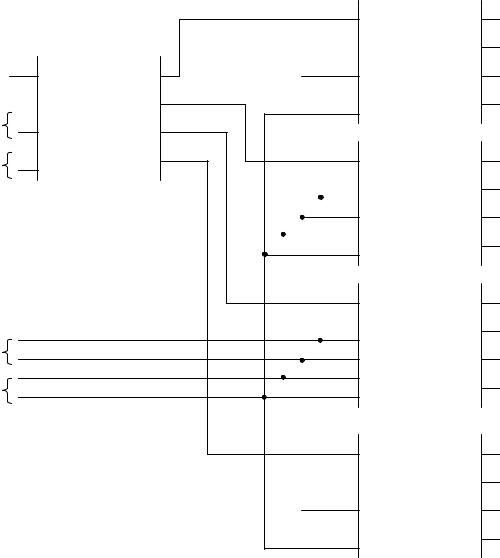

Рис. 3.9. Каскадное соединение дешифраторов

Таким образом, каскадно соединяя дешифраторы, можно строить схемы с большим числом выходов, используя вкачествесоставных частей малые дешифраторы.

3.5. Шифраторы

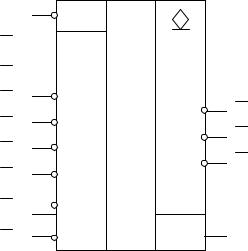

Шифраторы выполняют задачи обратные дешифраторам. С их помощью активным значением определяемых входных сигналов можно поставить в соответствие заданные выходные коды (комбинации выходных сигналов). Полный шифратор имеет n выходов и m = 2n входов (рис. 3.10, а). Выходной сигнал шифратора в числовой интерпретации соответствует номеру возбужденного входа. Таблица истинности одного

62

из вариантов восьмивходового полного шифратора с единичными активными значениями входных сигналов представлена в таблице 3.6.

Для построения схемы шифратора рассмотрим закономерности формирования двоичных переменных на его выходах. Выход y1 соответствующий младшему разряду выходного кода, имеющему вес 1, должен принимать значение 1 при возбуждении любого из нечетных входов. Следовательно, это должен быть выход ЛЭ ИЛИ, к m/2 входам которого подключены все входы с нечетными номерами, то есть такими, двоичное представление номера которых в младшем разряде имеет 1 (рис. 3.10, б).

Х0 |

|

0 |

CD |

|

|

|

|

|

|

||||

Х1 |

|

1 |

|

|

|

|

|

|

|

|

|

||

Х2 |

|

2 |

|

1 |

|

Y1 |

|

|

|

||||

Х3 |

|

3 |

|

|

||

|

|

2 |

|

Y2 |

||

|

|

|

||||

Х4 |

|

4 |

|

|

||

|

|

4 |

|

Y3 |

||

|

|

|

||||

Х5 |

|

5 |

|

|

||

|

|

|

|

|

||

|

|

|

|

|

||

Х6 |

|

6 |

|

|

|

|

|

|

|

|

|

||

Х7 |

|

7 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

||

Х1 |

|

|

|

|

Х2 |

|

|

|

|

|

Х4 |

|

|

|

|

1 |

|

|

1 |

|

|

|

1 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||||

Х3 |

|

|

Y1 |

Х3 |

|

|

|

Y2 |

Х5 |

|

|

Y3 |

|||

|

|

|

|

|

|

|

|||||||||

Х5 |

|

|

|

Х6 |

|

|

|

|

Х6 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Х7 |

|

|

|

|

Х7 |

|

|

|

|

|

Х7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

б

Рис. 3.10. Условное графическое обозначение шифратора (а); построение шифратора с помощью схем ИЛИ (б)

Следующий выход Y2, имеющий вес 2, должен возбуждаться при подаче сигнала на входы с номерами 2, 3, 6, 7, то есть с номерами, двоичное представление которых во втором по старшинству разряде имеет единицу. Следовательно, Y2 также формируется элементом ИЛИ, имеющим m/2 входов. Таким образом, в общем случае Yk формируется элементом ИЛИ с числом входов m/2, на который подаются те из входных переменных, двоичное представление номера которых в k-м разряде имеют единицу.

63

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.6 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х7 |

Х6 |

Х5 |

Х4 |

Х3 |

Х2 |

Х1 |

Х0 |

У3 |

У2 |

У1 |

||||||

1 |

|

0 |

|

0 |

|

0 |

0 |

|

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

|

1 |

|

0 |

|

0 |

0 |

|

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

|

0 |

|

1 |

|

0 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

|

0 |

|

0 |

|

1 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

|

0 |

|

0 |

|

0 |

1 |

|

0 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

|

0 |

|

0 |

|

0 |

0 |

|

1 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

|

0 |

|

0 |

|

0 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

1 |

|

0 |

|

0 |

|

0 |

|

0 |

0 |

|

0 |

|

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

При практической реализации шифратора может оказаться выгоднее использовать элементы И-НЕ. Тогда, в соответствии с двойственностью операций конъюнкции и дизъюнкции, входные переменные нужно брать с инверсией.

Рассмотренный шифратор обладает рядом недостатков:

1)невозможно наращивать информационную емкость (число входов и выходов), соединяя между собой шифраторы меньшей емкости;

2)для правильной работы шифратора необходимо, чтобы возбужден был всегда строго один из входов. Во всех других случаях получаемый на выходе сигнал не отражает реальной ситуации на входе.

От этих недостатков свободен приоритетный шифратор. Такой шифратор работает как и рассмотренный, когда возбужденным является единственный вход. Когда возбуждено несколько входов, на выходе формируется число, указывающее минимальный из номеров возбужденных входов. Так, если возбуждены входы 3, 5, 6, то на выходе установится код числа 3.

Чтобы выделить ситуацию, когда отсутствуют возбужденные входы, в приоритетном шифраторе имеется дополнительный выход Р, называемый выходом признака невозбуждения. Двоичная переменная Yp, формируемая на этом выходе, принимает значение 0, когда возбужден по крайней мере один из входов, и значение единицы в противном случае. Условное обозначение приоритетного шифратора с инверсными входами и выходами, имеющего m = 8 и n = 3, показано на рис. 3.11. Чтобы сделать возможным наращивание информационной емкости шифратора, в него введен дополнительный вход разрешения Е.

64

E PCD

Х0  0

0

Х1  1

1

Х2 |

2 |

1 |

Y 1 |

|

Х3 |

3 |

|||

2 |

Y 2 |

|||

Х4 |

4 |

|||

4 |

Y 3 |

|||

Х5 |

5 |

|||

|

|

|||

Х6 |

6 |

P |

YP |

|

Х7 |

7 |

Рис. 3.11. Условное обозначение приоритетного шифратора

С той же целью выходы Y1, Y2, Y3 выполняют либо с открытым коллектором, либо с тремя устойчивыми состояниями. Когда переменная ХЕ на разрешении равна 1, шифратор функционирует в соответствии с рассмотренным правилом. В противном случае сигнал на выходе Р принимает значение 1, а все остальные выходы переводятся в непроводящее состояние.

3.6. Мультиплексоры

Мультиплексоры обеспечивают коммутацию на выходе одного из нескольких информационных входных сигналов в соответствии с заданным кодом на управляющих входах. Условное графическое обозначение одного из вариантов мультиплексора представлено на рис. 3.12. В зависимости от комбинации сигналов управления Х1, Х2, Х3 он обеспечивает коммутацию одного из восьми информационных входных сигналов D0 – D7 на выход Y.

Сигнал синхронизации V в данном случае имеет нулевое активное значение, разрешающее передачу информации с одного из входов на выход.

Структурная формула, определяющая функционирование рассматриваемого восьмивходового мультиплексора, имеет вид:

Y |

|

|

3 |

|

2 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

X |

X |

X |

VD0 X3X2X1VD1 X3X2 X1VD2 X3X2X1VD3 |

(3.2) |

||||||||||||||||||||||||||||||||||||||

X3 |

|

|

2X1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

X |

VD4 X3X2X1VD5 X3X2 X1VD6 X3X2X1VD7 . |

|

|

|||||||||||||||||||||||||||||||||||||||

65 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |