Материал: Захаров, Сайфутдинов - Вычислительная техника

|

|

|

|

|

|

|

Х3Х4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х3Х4 |

|

|

|

|

|

|

|

||||||||

|

00 |

|

01 |

11 |

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

00 |

|

01 |

|

|

11 |

|

10 |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

1 |

|

0 |

|

1 |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

00 |

|

|

|

|

1 |

|

1 |

|

|

1 |

|

1 |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

01 |

0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

01 |

|

|

1 |

|

0 |

|

|

1 |

|

0 |

|

|

|

|||||||||||

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

Х1Х2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х1Х2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

11 |

|

|

|

1 |

|

|

1 |

|

1 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

11 |

|

|

1 |

|

1 |

|

|

1 |

|

1 |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

10 |

|

|

|

1 |

|

1 |

|

1 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

1 |

|

1 |

|

|

1 |

|

1 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

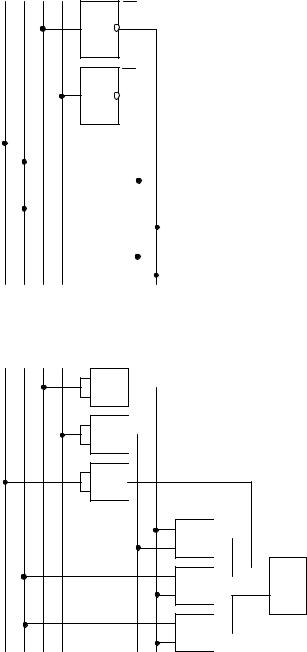

F2 X1 Х3 X2 X4 |

|

2 |

|

4 ; |

|

|

|

|

|

|

|

|

|

F3 X1 X2 X3X4 |

|

3 |

|

|

|

4 |

||||||||||||||||||||||||

X |

X |

|

|

|

|

|

|

|

|

X |

X |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

||

Рис. 3.18. Структура карты Карно для функции F2 (а) и функции F3 (б) |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х3Х4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

01 |

11 |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

00 |

|

|

1 |

|

1 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

01 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

Х1Х2 |

|

|

|

1 |

|

1 |

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

11 |

|

|

|

1 |

|

1 |

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

1 |

|

1 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.19. Структура карты Карно для функции F4

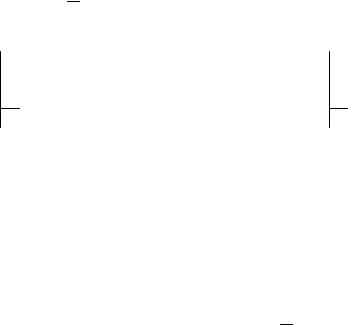

Каждая из рассмотренных функций может быть реализована в том или ином элементном базисе. Например, на рис. 3.20, а дана реализация функции Fl в базисе элементов И, ИЛИ, НЕ, а на рис. 3.20, б — реализация этой же функции в базисе элементов И-НЕ.

Соответствующая логическая формула легко устанавливается применением правила де Моргана:

F1 X1 X2 X4 X2 X3 X3X4 X1 X2 X 4 X2 X3 X3X4 .

Аналогично реализуются и другие логические функции.

71

X1 X2 X3 X4

1 Х3

1 Х4

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

F 1 |

|

|

|

|

|

& |

|

|||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a

X1X2 X3 X4

&

&

&

&

&

&

&  F1

F1

&

б

Рис. 3.20. Реализация функции F1 в базисе И, ИЛИ, НЕ (а),

реализация функции F1 в базисе И-НЕ (б)

72

Контрольные вопросы

1.Реализовать устройство неравнозначности в базисе И-НЕ.

2.Какие функции выполняет одноразрядный двоичный сумматор?

3.Какие существуют разновидности дешифраторов?

4.Какие функции выполняют мультиплексоры?

5.Найти выражения структурных формул для функций F5, F6, F7 (п. 3.7).

6.Реализовать функции F5, F6, F7 на ЛЭ в базисе И-НЕ.

73

4. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

Цифровое устройство называется последовательностным, если его выходные сигналы Y зависят не только от текущих значений входных сигналов X, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. В последовательностных устройствах (ПУ) предыстория поступления последовательности входных сигналов обязательно фиксируется с помощью специальных запоминающих элементов или элементов памяти, поэтому говорят, что ПУ обладает памятью. Элементы памяти помимо входных и выходных сигналов характеризуются состоянием, которое может изменяться в дискретные моменты времени под воздействием сигналов на его входе. Простейший элемент памяти может принимать одно из двух состояний, например, 0 или 1. Это состояние может сохраняться длительный период времени. К цифровым последовательностным устройствам относят триггеры, регистры, счетчики. Эти устройства называются также цифровыми автоматами, конечными автоматами или автоматами с памятью.

4.1. Триггеры. Общее определение

Триггером называют устройство, которое может находиться неограниченно долго в одном из двух состояний устойчивого равновесия и переходить из одного состояния в другое под воздействием входного сигнала. Состояние триггера определяют по выходному сигналу. В нем может храниться либо 0, либо 1. Обычно триггер наряду с основным прямым выходом Q имеет еще инверсный выход Р, потенциал которого имеет значение, обратное (в информационном смысле) значению прямого выхода, т. е. P = Q (если Q = l, то P = Q = 0). Состоянию триггера 1 соответствует на выходе Q высокий уровень сигнала (1), а на выходе Q низкий (0). Состоянию триг-

гера 0 соответствует на выходе Q низкий уровень сигнала (0), а на выходе Q высокий (1). Входы триггера подразделяются на информационные и вспомогательные (управляющие). Сигналы, поступающие на информационные входы, управляют состоянием триггера. Сигналы на вспомогательных входах используются для предварительной установки триггера в требуемое состояние и синхронизации.

74

Вспомогательные входы могут использоваться и в качестве информационных. Число входов триггера зависит от его структуры и назначения. Информационные входы триггера принято обозначать буквами S, R, J, К, D, Т, а управляющие входы С и V. Для триггера имеется стандартное обозначение (рис. 4.1). Здесь S и R являются информационными входами, Q и Q выходами, Т обозначает триггер.

|

|

S |

T |

|

|

Q |

|

|

Т |

T |

|

|

Q |

||

|

|

|

|

|

|

||||||||||

|

|

R |

о |

|

|

|

|

о |

|

|

|||||

|

|

|

|

|

|

|

|

||||||||

|

|

Q |

|

|

|

|

Q |

|

|||||||

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

Рис. 4.1. Условное обозначение |

Рис. 4.2. Условное обозначение |

||||||||||||||

|

|

RS-триггера |

|

|

|

|

Т-триггера |

|

|

||||||

Триггер на рис. 4.1 называют RS-триггером или триггером с раздельным запуском. При раздельном запуске управляющие сигналы поступают на два входа триггера от двух источников сигнала. При поступлении управляющего сигнала на вход S (установка 1) триггер устанавливается в состояние 1 (т. е. Q = l, Q = 0), а при поступлении управляющего сигнала на вход R (установка 0) триггер устанавливается в состояние 0. На рис. 4.2 представлен триггер с общим (счетным) входом или Т-триггер. При общем запуске управляющие сигналы поступают на один общий вход и при этом триггер изменяет состояние от каждого сигнала, т. е. каждый входной сигнал должен изменить состояние триггера на противоположное.

4.2. Классификация триггеров

Триггеры классифицируются по способу приема информации, по принципу построения, по функциональным возможностям. По способу приема информации триггеры подразделяются на асинхронные и синхронные. Асинхронные триггеры воспринимают информационные сигналы и реагируют на них в момент появления на входах триггера. Синхронные триггеры реагируют на информационные сигналы при наличии разрешающего сигнала на специальном управляющем входе С, называемом входом синхронизации. Синхронные триггеры подразделяются на триггеры со статическим и динамическим управлением по входу С. Триггеры со статическим управлением

75

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |