Материал: Захаров, Сайфутдинов - Вычислительная техника

|

D0 |

MS |

|

|

|

|

|||

|

D 1 |

8 / 1 |

|

|

|

|

|

||

|

D 2 |

|

|

|

|

|

|

|

|

|

D 3 |

|

|

|

|

|

|

|

|

|

D 4 |

|

|

|

|

|

|

|

|

|

D 5 |

|

Y |

|

|

|

|

||

|

D 6 |

|

|

|

|

|

|

|

|

|

D 7 |

|

|

|

|

|

|

|

|

|

Х1 |

|

|

|

|

|

|

|

|

|

Х2 |

|

|

|

|

|

|

|

|

|

Х3 |

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

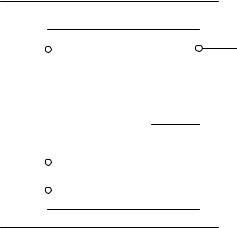

Рис. 3.12. Условное графическое обозначение мультиплексора

Мультиплексор можно реализовать с помощью ЛЭ заданного базиса. В его структуру можно ввести и более сложные цифровые устройства. Сопоставляя формулы (3.1) и (3.2), можно заметить, что для каждого входа D комбинации сигналов управления Х1, Х2, Х3 в мультиплексоре такие же, как и в дешифраторе. Следовательно, составной частью мультиплексора является дешифратор.

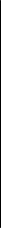

Структурная схема одного из возможных вариантов мультиплексора с четырьмя информационными входами D0 – D3 приведена на рис. 3.13.

V |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

D2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

Y |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

|

1 |

DC |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

1 |

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

X2 |

|

2 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.13. Схема мультиплексора с четырьмя информационными входами

66

3.7. Демультиплексоры

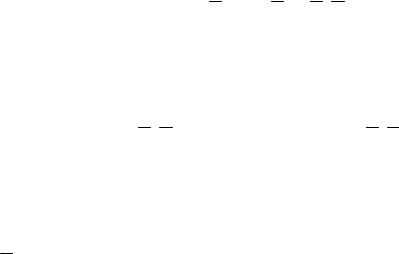

Демультиплексоры представляют собой цифровые устройства для коммутации информационного входного сигнала в одном из нескольких выходов в соответствии с заданным кодом на управляющих входах. Иными словами, демультиплексоры решают задачи обратные мультиплексированию. Условное графическое обозначение демультиплексора с четырьмя информационными выходами представлено на рис. 3.14. Структурные формулы, определяющие формирование выходных сигналов такого демультиплексора, имеют вид:

Y0 |

|

2 |

|

1D ; Y1 |

|

2X1D ; Y2 X2 |

|

1D ; Y3 X2 X1D . |

(3.3) |

X |

X |

X |

X |

|

D |

DMS |

Y0 |

|

|

|

|||

|

|

1/4 |

Y1 |

|

|

|

|

||

|

X1 |

|

Y2 |

|

|

|

|

||

|

X2 |

|

Y3 |

|

|

|

|

||

|

|

|

|

Рис. 3.14. Условное графическое обозначение демультиплексора

Точно такими же выражениями определяется формирование выходных сигналов дешифратора, использующего синхронизацию по входу D. Поэтому в качестве демультиплексора можно применять дешифратор, в котором информационный входной сигнал подан на вход синхронизации. Примером является реализация 2-разрядного демультиплексора с нулевыми активными сигналами на основе рассмотренного выше сдвоенного дешифратора К155ИД4 (см. рис. 3.6, б). Если первый разряд DP подать на вход V1, а второй разряд DP – на вход V3, то, в зависимости от комбинаций значений Х1, Х2, можно обеспечить коммутацию этого 2-разрядного кода DP1DP2 на любой из четырех выходов Y. На остальные входы синхронизации V2 и V4 можно подать постоянные значения (V2 = 1, V4 = 0), либо использовать их для организации синхронной передачи информации на выходы (рис. 3.15).

67

|

|

|

|

|

|

DMS |

||

DP1 |

|

|

|

V1 |

|

DC |

|

y0 |

|

|

|

|

|

||||

|

«1» |

|

|

|

||||

|

|

|

V2 |

|

|

|

y |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

y21 |

|

|

|

|

X |

|

|

|

|

X |

|

|

|

|

|

|

y |

|

|

|

|

|

|

|

|||

X12 |

|

|

|

X12 |

|

|

|

y3 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

y0 |

D |

|

|

|

V3 |

|

|

|

|

|

|

|

|

|

|

1 |

||

|

|

|

|

|

|

|

|

|

P2 |

|

«0» |

|

V4 |

|

|

|

y2 |

|

|

|

|

|

|

y3 |

||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Разряд Р1 Разряд Р2

Разряд Р1 Разряд Р2

Рис. 3.15. Условное графическое обозначение демультиплексора на основе двух ИМС К155ИД4

3.8.Преобразователи кодов

Вбольшинстве случаев задача перекодирования информации решается с помощью специальных КУ-преобразователей кодов. Синтез заданного преобразователя сводится к минимизации и реализации в выбранном базисе стольких функций, сколько разрядов содержится в выходном коде. Аргументами этих функций являются разряды входного кода. При наличии избыточных наборов их используют для доопределения и упрощения логической схемы.

Синтез преобразователя кодов рассмотрим на примере преобразования двоич- но-десятичного кода в специальный семиразрядный код, необходимый для управления работой семиэлементного цифрового индикатора, схема включения которого показана на рис. 3.16, а, а индикация цифр показана на рис. 3.16, б. Подсветка каждого из его элементов, образующих цифры от 0 до 9, производится подачей единичного сигнала на вход, соответствующий этому элементу. Сигналы поступают на цифровой индикатор с выхода преобразователя кодов (ПК). На входы преобразователя подаются логические сигналы четырехразрядных двоично-десятичных кодов. Задача заключается в синтезе такой логической схемы ПК, которая сформирует на индикаторе изображения цифр, соответствующих входным двоично-десятичным кодам.

68

Х1

Х2

Х3

Х4

|

|

|

F |

|

|

|

F2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

ПК |

|

F21 |

|

|

|

|

|

|

|

|

|

|

|

F1 |

|

|

F7 |

|

|

F3 |

|

|

||

|

|

F |

|

|

|

|

|

|

||||

|

|

|||||||||||

|

|

|

F3 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F4 |

F6 |

|

|

|

|

|

F4 |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|||||||||

|

|

|

F65 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F5 |

|

|

|

|

|

|

|

|

|

F7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

б |

|

Рис. 3.16. Структурная схема преобразователя кодов (а) и индикация цифр на семисегментном индикаторе (б)

Выходные логические переменные F1, ..., F7 являются функциями входных переменных Х1, ..., Х4. Таблица истинности этих логических функций представлена в таблице 3.7.

Единичные значения выходных переменных соответствуют элементам, подсвечиваемым при изображении цифры. Например, десятичная цифра 0 задается двоичнодесятичным кодом 0000. При этом подсвечиваются все элементы, за исключением F7. Цифра 7 задаемся кодом 0111, а подсвечиваются элементы F2, F3 и F4. Логические функции в таблице 3.7 определены не полностью: последние шесть кодовых комбинаций не соответствуют никаким десятичным цифрам и являются запретными.

Следуя изложенной выше методике, изобразим на рис. 3.17 карту Карно для логической функции F1 .

|

|

|

|

|

|

|

|

Х3Х4 |

|

|

|

|

|

|

|

|

|

00 |

|

|

01 |

11 |

10 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

|

|

1 |

|

|

0 |

|

0 |

0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х1Х2 |

01 |

|

|

1 |

|

|

1 |

|

0 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

1 |

|

|

1 |

|

1 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

1 |

|

|

1 |

|

1 |

1 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F1 X1 X 2 X4 X 2 X3 X3 X4

Рис. 3.17. Структура карты Карно для функции F1

69

Таблица 3.7

Цифра |

х1 |

х2 |

х3 |

х4 |

F1 |

F2 |

F3 |

F4 |

F5 |

F6 |

F7 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

3 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

4 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

5 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

- |

1 |

0 |

1 |

0 |

* |

* |

* |

* |

* |

* |

* |

- |

1 |

0 |

1 |

1 |

* |

* |

* |

* |

* |

* |

* |

- |

1 |

1 |

0 |

0 |

* |

* |

* |

* |

* |

* |

* |

- |

1 |

1 |

0 |

1 |

* |

* |

* |

* |

* |

* |

* |

- |

1 |

1 |

1 |

0 |

* |

* |

* |

* |

* |

* |

* |

- |

1 |

1 |

1 |

1 |

* |

* |

* |

* |

* |

* |

* |

|

|

|

|

|

|

|

|

|

|

|

|

Ячейки, в которых функция не определена, отметим знаком * и доопределим их единицами. Покрытие содержит четыре прямоугольника. Следовательно, минимизированная ДНФ этой функции должна содержать четыре элементарных произведения, что и показано на этом же рисунке.

F1 X1 X 2 X4 X 2 X3 X3 X4 .

Аналогично, доопределив единицами все неопределенные значения функций F2 и F3, получим для них наилучшие покрытия и минимальные дизъюнктивные формы, показанные на рис. 3.18, а, б.

F2 X1 Х3 X2 X4 X2 X4 ; F3 X1 X2 X3X4 X3X4 .

При минимизации функции F4, представленной на рис. 3.19, ячейку с координатами 1010 доопределим нулем. Формула минимизированной функции при этом существенно упростится.

F4 Х3 X4 X2 .

70

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |