Материал: Захаров, Сайфутдинов - Вычислительная техника

3.3. Комбинационные сумматоры

Рассмотрим логическую схему полусумматора, предназначенную для суммирования двух одноразрядных двоичных чисел. Логическая функция полусумматора задается следующей таблицей истинности (табл. 3.3).

|

|

|

Таблица 3.3 |

|

|

|

|

|

|

X1 |

X2 |

S' |

Р' |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

Здесь X1 и Х2 — переменные, S' — частичная сумма (сумма по модулю два), Р' — перенос в старший разряд. Из таблицы истинности видно, что

S' = X1 Х2, Р' = X1 Х2,

т. е. полусумматор имеет два выхода (S', P') и реализуется с помощью устройства неравнозначности и схемы И. Функциональная схема полусумматора представлена на рис. 3.4 (а, б).

=1 |

S' |

|

|

|

|

|

|

|

X1 |

|

|

|

P' |

|

|

|

|

|

|

|

HS |

P |

||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

& |

|

P' |

|

S' |

||||

|

|

|

|

X2 |

|

|

S |

||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

а б Рис. 3.4. Функциональная схема полусумматора (а)

и его условное графическое обозначение (б)

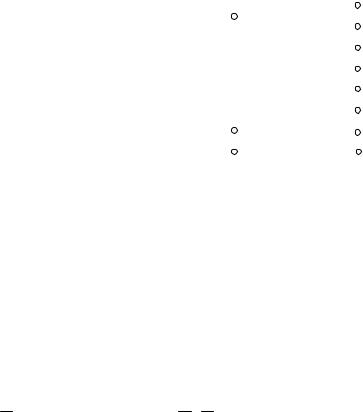

Два одноразрядных полусумматора образуют одноразрядный сумматор. Сумматор — логическая схема, имеющая три входа (входы разрядов Х1 и Х2

56

суммируемых чисел и вход Х3 для возможного переноса, образованного при сложении младших разрядов). Сумматор может быть образован с помощью двух полусумматоров и элемента ИЛИ. Таблица истинности (табл. 3.4) и функциональная схема сумматора показаны на рис. 3.5. В суммирующем устройстве последовательного действия для суммирования многоразрядных чисел перенос Р подается на вход Х3 с задержкой на один такт сложения. Для ускорения процесса сложения двух n-разрядных чисел можно построить суммирующее устройство параллельного действия, в которых используются n сумматоров одноразрядных чисел. В настоящее время одно-, двух- и четырехразрядные двоичные сумматоры выпускаются в виде отдельных ИМС

(К155ИМ1, К155ИМ2, К155ИМ3).

|

|

|

|

Таблица 3.4 |

||

|

|

|

|

|

|

|

Х1 |

Х2 |

Х3 |

S |

|

Р |

|

0 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

1 |

|

0 |

|

0 |

1 |

0 |

1 |

|

0 |

|

0 |

1 |

1 |

0 |

|

1 |

|

1 |

0 |

0 |

1 |

|

0 |

|

1 |

0 |

1 |

0 |

|

1 |

|

1 |

1 |

0 |

0 |

|

1 |

|

1 |

1 |

1 |

1 |

|

1 |

|

|

|

|

|

|

|

|

X1 |

|

HS |

P |

P' |

|

|

|

|

|

Р |

|

|

|

|

|

|

|

||

|

|

|

|

|

1 |

X1 |

|

X1 |

SM |

P |

|

P |

|||||||

|

|

|

|

|

|

|

|

||||||||||||

X2 |

|

|

S |

S' |

|

|

|

P" |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

HS |

|

P |

|

|

|

S |

X2 |

X2 |

|

|

|

|

||||

X3 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

S |

|

|

|

X3 |

|

X3 |

|

S |

|

S |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

а |

|

|

|

|

|

|

б |

|

|

|

|||

Рис. 3.5. Функциональная схема (а)

и условное графическое обозначение сумматора (б)

57

3.4. Дешифраторы

Дешифратором называется комбинационное устройство, имеющее несколько входов и выходов, у которого каждой комбинации входных сигналов соответствует активное значение только одного определенного выходного сигнала. Полный дешифратор с m входами имеет 2m выходов. Таблица истинности трехвходового полного дешифратора с единичным активным значением выходных сигналов Y представлена в таблице 3.5.

Таблица 3.5

Х3 |

Х2 |

Х1 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

На практике часто используются неполные дешифраторы, предусматривающие декодирование только отдельных входных сигналов. Если задачу синтеза соответствующего КУ с тремя входами и восемью выходами рассматривать как синтез восьми одновходовых КУ, то для каждой из булевых функций Y можно записать структурную формулу:

Y0 |

|

|

|

|

|

|

|

|

|

|

1, Y1 |

|

3 |

|

|

2 X1, Y2 |

|

3X2 |

|

|

1, Y3 |

|

3X2 X1 , |

|

||

X |

3 |

|

X |

2 |

|

X |

X |

X |

X |

X |

X |

|

||||||||||||||

Y4 |

X3 |

|

|

|

1, Y5 X3 |

|

2X1, Y6 X3X2 |

|

1 , Y7 X3X2 X1. |

(3.1) |

||||||||||||||||

X |

2 |

X |

X |

X |

||||||||||||||||||||||

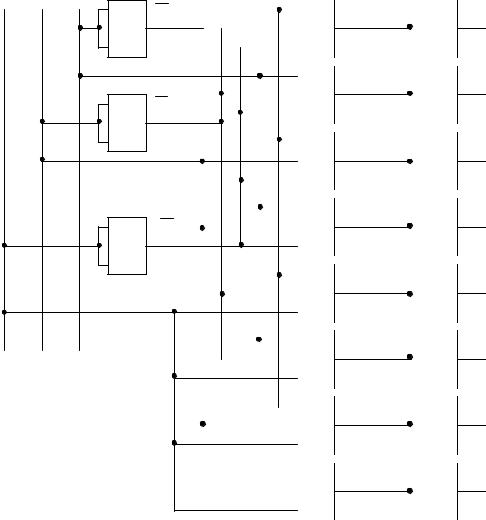

Условное графическое обозначение дешифратора, соответствующего табл. 3.5, представлено на рис. 3.6, а. В интегральном исполнении выпускаются различные структуры дешифраторов, в которых используются 2, 3, 4 входа. В одном корпусе может быть несколько дешифраторов.

58

Для увеличения функциональных возможностей устройств часто предусматривается использование нескольких сигналов управления. На рис. 3.6, б представлено графическое изображение микросхемы К155ИД4, содержащей сдвоенный двухвходовой дешифратор с активными нулевыми выходными сигналами.

|

|

|

DC |

y0 |

|

|

|

V1 |

DC |

y0 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|||||

Х1 |

|

Х1 |

y1 |

|

|

|

V2 |

y1 |

|

||

|

|

|

|

||||||||

|

|

|

|

|

|||||||

|

|

|

|

y2 |

|

|

|

X1 |

|

y2 |

|

Х2 |

|

Х2 |

|

y3 |

|

|

|

|

y3 |

|

|

|

|

|

|

|

|

|

|||||

|

|

y4 |

|

|

|

X2 |

|

y4 |

|

||

|

|

|

|

|

|

|

|

|

|||

Х3 |

|

Х3 |

|

y5 |

|

|

|

|

|

y5 |

|

|

|

|

|

|

V3 |

|

|

||||

|

|

y6 |

|

|

|

|

y6 |

|

|||

|

|

|

|

|

|

|

|||||

|

|

|

|

y7 |

|

|

|

V4 |

|

y7 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

а б Рис. 3.6. Условное графическое обозначение дешифратора (а)

и условное графическое обозначение ИМС К155ИД4 (б)

На выходах обоих дешифраторов формируются сигналы в соответствии с комбинациями входных сигналов Х1 и Х2. Синхронизация процесса формирования выходных сигналов Y0–Y3 для каждого дешифратора задается комбинациями управляющих сигналов V. Для верхнего дешифратора разрешает формирование выходных сигналов комбинация V1 V2 , для нижнего – V3 V4 . При отсутствии разрешающих комбинаций на каждом выходе Y устанавливается единичное значение сигнала. Введение такого управления расширяет возможности микросхемы при построении более сложных устройств, например, дешифраторов с увеличенным числом входов и выходов.

Переключательную функцию (формула 3.1) можно реализовать на отдельном элементе И, в этом случае мы получим наиболее простой по структуре дешифратор, который можно реализовать также на элементах И-НЕ (рис. 3.7).

Достоинство линейного дешифратора – высокое быстродействие; недостаток – большое количество требуемых входов логических элементов, равное количеству разрядов дешифрируемого слова. Кроме того, ограниченная нагрузочная способность ИМС ограничивает разрядность дешифрируемых слов до 4–5. Поэтому широко применяются пирамидальные дешифраторы, характерным отличием которых от линейных является использование только двухвходовых элементов.

59

Х3 Х2 Х1

& o Х1

& o Х2

& o Х3

|

|

|

|

|

Х |

|

Х |

|

Х |

|

|

|

|

|

Y |

|

|

|

|

|

|

|

|

|

|

|

|

3 |

2 |

1 |

|

|

|

|

Х |

Х |

Х |

1 |

|||||||

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

& o |

|

& |

o |

0 |

3 |

2 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

2 |

Х |

|

|

|

|

Y |

|

|

|

|

|

Х |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

Х |

Х |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

& |

|

1 |

|

& o |

Х |

Х |

|

1 |

|||||||||||||||||||||||||||||||

|

|

|

|

|

o |

|

|

|

|

|

|

|

1 |

3 |

|

2 |

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

& |

|

|

Х |

3Х2 |

Х |

1 |

|

& o |

Y |

Х |

|

|

Х |

2 |

|

Х |

1 |

||||||||||||||||||||||

|

|

|

|

|

o |

|

|

|

|

|

|

|

|

2 |

3 |

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

3Х2Х |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

Х |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

& |

|

|

& oY3 |

Х3Х2 Х1 |

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

o |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

& oХ3 |

Х |

2 |

|

Х |

1 |

|

& o Y4 |

Х3 |

Х |

2 |

Х |

1 |

|||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

Х3 |

|

|

|

2 Х |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

& |

|

Х |

|

& o |

Y Х |

Х |

|

|

Х |

1 |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

o |

|

|

|

|

|

|

|

|

5 |

3 |

|

2 |

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

Х3Х2 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

Х |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

& |

|

|

& o Y6 |

Х3Х2 Х1 |

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

o |

|

|

|

|

|

1 |

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

Х3Х2 Х |

|

|

|

Y Х |

Х |

2 |

Х |

1 |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

& |

o |

|

|

|

|

|

|

|

|

& o |

7 |

3 |

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.7. Принципиальная схема линейного дешифратора на элементах И-НЕ

На рис. 3.8 представлена схема пирамидального дешифратора на 3 входа, выполненная на двуxвходовых элементах И-НЕ. В пирамидальных дешифраторах требуется большее количество логических элементов, но по числу корпусов ИС пирамидальная схема может оказаться эквивалентной линейной, т. к. 2-входовых ЛЭ в одном корпусе размещается больше.

Третий вид структуры дешифратора — каскадное соединение дешифраторов. На рис. 3.9 показана группа из пяти дешифраторов, соединенных последовательно в два каскада. Все дешифраторы одинаковы и построены по структуре линейного дешифратора с инверсными выходами и дополнительным стробируемым входом С. На первый каскад, т. е. на входы DC4, поданы старшие разряды дешифрируемого числа Х3, Х4. При этом DC определяет, в какой четверке из возможных 16 вариантов находится избранный выход.

60

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |