Материал: Захаров, Сайфутдинов - Вычислительная техника

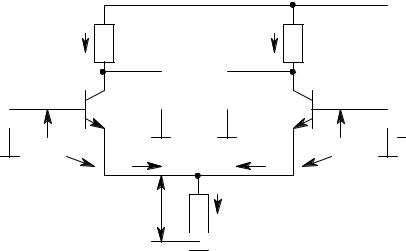

Логические элементы ЭСЛ выполняются на базе |

переключателей тока |

(рис. 2.22). На базу транзистора VT0 подано напряжение Е0. |

Пусть Uвх1 = E0, при |

этом оба транзистора работают в активном режиме. Ток через резистор Rэ равен: Iэ = |E0 Uбэо| Rэ. Транзисторы выбирают идентичными, поэтому i э1 = iэ0= Iэ/2.

+Eп

Ik1 |

|

Ik0 |

o |

|

R k1 |

Rk0 |

|

||

|

o |

o |

|

|

o |

Uk1 |

Uk0 |

o |

+ |

VT1 o |

o VT0 |

|||

Uвх1 o |

|

|

o |

E0 |

Uбэ1 |

I э1 |

Iэ0 |

Uбэ0 |

|

Uэ

I э

Rэ

Rэ

Рис. 2.22. Схема переключателя тока

Uk1 = Uk0 = Eп IэRk1/2 . Если входное управляющее напряжение Uвх1 > E0, то iэl, iк1 увеличиваются, напряжение Uk1 падает, а напряжение Uэ растет, что приводит к уменьшению Uбэ0 и, следовательно, к уменьшению ik0 и к увеличению Uk0. Дальнейшее увеличение Uвx приводит к полному запиранию транзистора VT0. При этом напряжение Uk0 = Eп (без учета неуправляемых тепловых токов), Uk1 = Eп IэRk. Ток Iэ I к1 течет только через транзистор VT1.

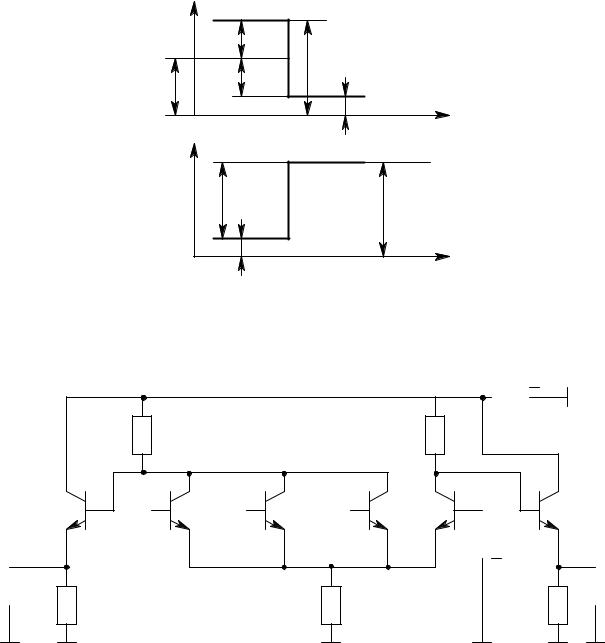

При уменьшении напряжения Uвх относительно Е0 уменьшается ток ik1, растет напряжение Uk1, растет ток ik0, уменьшается напряжение Uk0 . При некотором Uвx < U0 транзистор VT1 закрывается и ток Iэ течет только через транзистор VT0. В этом случае Uk0 = Eп - IэRk0: Uk1 = Еп. Таким образом, при изменении Uвх на некоторое значение 2 U симметрично относительно Е0, транзисторы переключаются (рис. 2.23).

Выходной перепад напряжения Umвых = IэRk. Отметим, что высокий входной уровень U1вх соответствует уровню логической единицы Е1, а низкий входной уровень U0вх – уровню логического нуля Е0. Обычно выбирают E0 = 0,5 (Е1 + Е0).

46

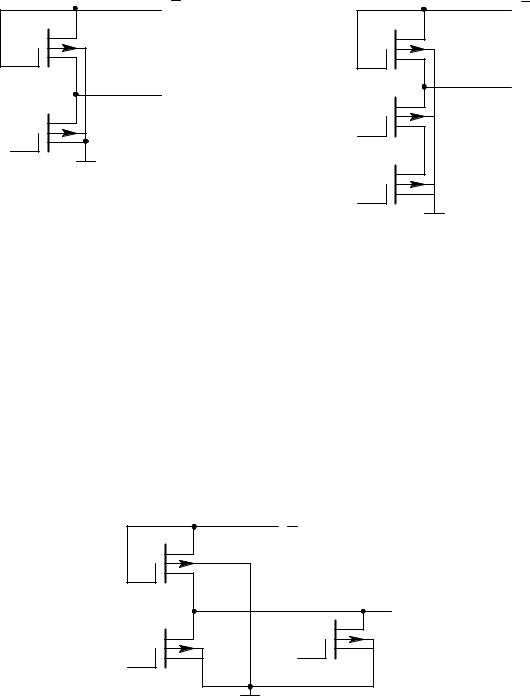

Схема ЭСЛ логического элемента представлена на рис. 2.24, в которой для реализации многовходовой переключательной функции входной транзистор заменяют группой параллельно соединенных транзисторов, а для согласования входных и выходных уровней логической единицы и нуля в схему включены эмиттерные повторители. При этом на выходе у формируется функция ИЛИ-НЕ, на выходе у2 – функция ИЛИ.

Uвх |

|

|

|

U |

1= U1вх |

|

|

E |

|

||

U |

|

|

|

Е0 |

|

0 |

0 |

|

|

E = U вх |

|

Uвых |

|

|

t |

|

|

|

|

(Uk1) |

|

|

|

Umвых |

|

|

Eп = U1вых = Uk1 |

|

|

|

|

U0вых = Eп IэRk |

|

t |

|

Рис. 2.23. Временная диаграмма состояния переключателя тока |

|||

|

|

|

|

+ |

|

|

|

|

|

|

|

о +E |

о |

|

|

|

Rk |

|

Rk0 |

|

п |

|

|

|

|

|

|

|

|

||

VT1 |

Х1 о VT2 Х2 о VT3 |

Х3 о VT4 VT0 о+ |

|

|

VT5 |

||

|

|

|

E |

0 |

|

|

|

о |

|

|

о |

|

|

|

о |

|

|

|

|

|

|

||

Y |

R |

R |

э |

|

R |

|

Y |

о1 |

1 |

|

|

|

2 |

о2 |

|

Рис. 2.24. Принципиальная схема ЭСЛ логического элемента

47

Имея высокое быстродействие, схемы ЭСЛ имеют и недостатки: низкая помехоустойчивость и большая потребляемая мощность, т. к. для достижения быстрого перезаряда паразитных емкостей в схеме используются резисторы с малым сопротивлением, через которые текут большие токи.

2.17. Логические элементы на МОП-транзисторах

Логические элементы на МОП-транзисторах изготавливаются по р-МОП, n- МОП, КМОП-технологиям. В первых используются р-канальные транзисторы, во вторых n-канальные транзисторы, а в третьих – используются комплементарные МОП-схемы, где в одной схеме применяются как р-канальные, так и n-канальные транзисторы. Схемы на МОП-транзисторах имеют меньшее быстродействие, чем схемы на биполярных транзисторах, что объясняется значительными емкостями между затвором, стоком, истоком и подложкой, на перезаряд которых требуется определенное время. Схемы на МОП-транзисторах потребляют малую мощность, имеют высокую нагрузочную способность и высокую помехоустойчивость, занимают малую площадь на поверхности кристалла, они технологичны и дешевы. Их применяют в тех случаях, где нужна большая степень интеграции и небольшое быстродействие. Особенность микросхем на МОП-структурах заключается в том, что в их схемах отсутствуют резисторы, а роль нелинейных резисторов выполняют соответствующим образом включенные транзисторы.

Логические элементы на р-канальных транзисторах. В основе всех логических схем на МОП-структурах лежит инвертор (рис. 2.25). При подаче на вход Х напряжения Е (логическая единица), транзистор VT2 открывается, его сопротивление становится малым и на выходе мы получаем напряжение близкое к нулю (логический нуль). При подаче на вход напряжения логического нуля транзистор VT2 закрывается и на выходе мы имеем напряжение –Е .

Для реализации функции И-НЕ ключевые транзисторы включают последовательно с нагрузочным транзистором VT1 (рис. 2.26). Если на каком-либо входе напряжение равно нулю (логический нуль), то соответствующий транзистор закрыт и напряжение на выходе равно –Е (логическая единица).

48

|

о |

E |

VT1 |

с |

|

|

и |

|

|

о |

Y |

VT2 |

с |

|

Х о |

и |

|

Рис. 2.25. Инвертор на р-МОП-транзисторах

|

с |

о |

E |

|

VT1 |

|

|

|

и |

|

|

|

о |

Y |

|

|

с |

||

|

VT2 |

|

|

Х1 о |

и |

|

|

|

|

||

|

с |

VT3 |

|

Х2 о |

и |

|

|

|

|

||

Рис. 2.26. Схема ЛЭ И-НЕ |

|

||

на р-МОП-транзисторах

Если на все входы подать напряжение, соответствующее логической единице (–Е), то транзисторы VT2 и VT3 будут открыты и иметь низкое сопротивление, выходное напряжение будет близко к нулю (логический нуль). Схема ИЛИ-НЕ образуется параллельным соединением переключательных транзисторов VT2 и VT3 и подсоединением их объединенных стоков к истоку нагрузочного транзистора VT1 (рис. 2.27).

|

|

о |

E |

|

|

VT1 |

|

|

|

|

оY |

|

|

VT2 |

VT3 |

|

|

|

|

Х |

1 о |

Х |

2 о |

|

|

||

Рис. 2.27. Схема ЛЭ ИЛИ-НЕ на р-МОП-транзисторах |

|||

Если на любом из двух входов схемы напряжение соответствует логической единице (–Е), то соответствующий транзистор открыт и имеет низкое сопротивление. При этом на выходе будет напряжение близкое к нулю (логический нуль). Если на все входы поданы логические нули, то все транзисторы будут закрыты и на выходе будет напряжение –Е.

49

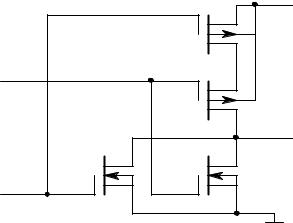

Логические схемы на КМОП-структурах. Преимущества ЛЭ на КМОП-

структурах: малая потребляемая мощность, высокая помехоустойчивость, высокое быстродействие. Высокое быстродействие таких схем реализуется за счет того, что в цепях заряда и разряда паразитных емкостей схемы включены малые сопротивления открытых транзисторов. Логические схемы И-НЕ, ИЛИ-НЕ образуются параллельнопоследовательным соединением ключевых транзисторов. На рис. 2.28 представлена схема, реализующая функцию ИЛИ-НЕ, использующая как р-канальные, так и n-канальные транзисторы.

|

|

|

|

и |

о + E |

|

|

|

|

VT1 |

|

|

|

|

|

|

c |

|

|

|

|

|

|

|

|

|

|

Х2 о |

|

|

VT2 |

и |

|

|

|

|

|

c |

|

|

|

|

|

|

|

о |

Y |

|

|

|

c |

|

c |

||

|

VT3 |

VT4 |

|

|

||

|

|

|

|

|

||

X1 о |

|

и |

|

и |

|

|

Рис. 2.28. Схема ЛЭ ИЛИ-НЕ на КМОП-структуре

Схема работает следующим образом. При подаче высокого уровня напряжения (+Е) на вход х1 транзистор VT1 закрывается, а транзистор VT3 открывается, на выходе будет напряжение близкое к нулю (логический нуль). То же самое будет и при подаче напряжения (+Е) на вход х2. При подаче на входы х1 и х2 логического нуля транзисторы VT3 и VT4 будут закрыты, а транзисторы VT1 и VT2 открыты. На выходе будет высокий уровень напряжения (+Е) – логическая единица.

Логическая схема, реализующая функцию И-НЕ, представлена на рис. 2.29. Если на вход х1 подан уровень логического нуля (0 В), то транзистор VT1 будет

открыт, а транзистор VT4 – закрыт. На выходе будет высокое напряжение (+Е) – логическая единица. То же самое будет и при подаче нуля на вход х2. При подаче на входы х1 и х2 логической единицы, транзисторы VT1 и VТ2 будут закрыты, а транзисторы VT3, VT4 открыты – на выходе будет уровень логического нуля. В КМОП-логических схемах ток постоянно не протекает.

50

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |