Материал: Захаров, Сайфутдинов - Вычислительная техника

Быстродействие логической схемы тем выше, чем меньше tЗ.ср.. Все логические элементы по быстродействию можно разделить условно на 4 группы: сверхбыстродействующие – t З.ср. < 5 нс; быстродействующие – t З.ср. = 5 – 10 нс; среднебыстродействуюшие – t З.ср. = 11 – 15 нс; медленнодействующие – t З.ср. > 15 нс.

Коэффициент объединения по входу или число входов (m) логического элемента определяет максимальное количество входных сигналов, над которыми можно произвести операции ИЛИ и И, в зависимости от типа элемента m = 2 – 12.

Нагрузочная способность или коэффициент разветвления по выходу (n) харак-

теризирует число входов аналогичных элементов, которые можно подключить к выходу данного элемента без нарушения его нормального функционирования. В зависимости от типа элемента n изменяется от 3 до 100.

Потребляемая мощность рассеивания в ЛЭ определяет не только его экономичность, но, что часто более важно, – степень его разогрева. Это ограничивает габариты элемента и всего устройства в целом. Уменьшение габаритов элемента и, следовательно, величины его охлаждающей поверхности при заданной величине его рассеивающей мощности приводит к росту температуры элемента сверх допустимого значения и к нарушению его работоспособности. Это обстоятельство оказывается особенно существенным в микроминиатюрных интегральных элементах. В сложном цифровом устройстве примерно половина входящих элементов в любой момент времени оказывается закрытой, а другая половина – открытой. Поэтому в качестве характеристики элемента пользуются понятием средней мощности Рср, под которой понимается полусумма мощностей, рассеиваемых в двух статических состояниях элемента: закрытом и открытом. Величина Рср достигает сотен милливатт.

2.11. Резисторно-транзисторные логические элементы

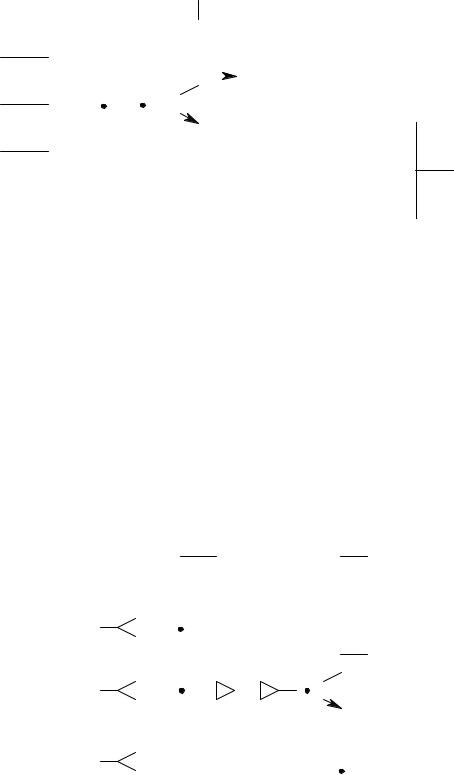

Схема базового элемента РТЛ изображена на рис. 2.13. Ее основой является простейший ключ – инвертор, а операция ИЛИ реализуется входной сборкой резисторов R1, R2, R3. Схема относительно проста, но обладает рядом недостатков, основным из которых является сильная зависимость глубины насыщения транзистора Т1 от числа логических единиц на входе, что приводит к ухудшению динамических характеристик транзистора. Эта же причина ограничивает функциональную сложность

36

ЛЭ – уменьшает коэффициент объединения по входу и коэффициент разветвления по выходу. Развитие интегральной схемотехники и технологии привело к тому, что в настоящее время система РТЛ практически не применяется.

|

|

|

|

|

|

|

|

o + Ek |

|

|

|

|

|

|

|

|

||||

Х1 o |

R1 |

|

|

|

R5 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

Y |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Х2 o |

R2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

VT1 |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

R3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х3 o |

|

|

|

|

|

|

|

|

Х1 |

|

1 |

|

|

Y = |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

X + X + X |

|

||||||

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

R4 |

|

|

|

|

Х2 |

|

|

o |

1 |

2 |

3 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

Х3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

||

Рис. 2.13. Принципиальная схема (а) и функциональное обозначение (б) РТЛ элемента

Диодно-транзисторные логические элементы

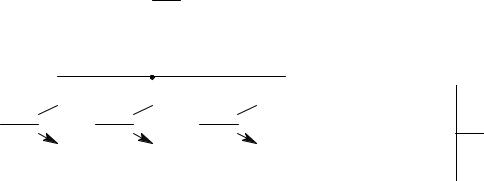

Диодно-транзисторные логические элементы находят широкое применение в цифровых устройствах. Они имеют повышенную помехоустойчивость, среднее быстродействие и сравнительно большой коэффициент разветвления по выходу n. Основная схема ДТЛ-элемента, выполняющая логическую функцию И-НЕ, дана на рис. 2.14.

|

|

|

|

|

|

|

о + Е1 |

|

|

|

|

|

|

|

о + Еk |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

VD1 |

|

|

R1 |

|

|

|

|

|

|

|

R3 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Х1 о |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

о Y = |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

VD2 |

|

|

VD4 VD5 |

|

|

|

|

|

|

|

X1 X2X |

|||||||||

Х2 о |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VT1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

VD3 |

|

|

|

|

|

R2 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Х3 о |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2.14. Принципиальная схема ДТЛ-элемента

37

Диоды VD1 – VD3 на входе схемы совместно с резистором R1 выполняют логическую операцию И. Транзистор VT1 выполняет роль усилителя-инвертора. Диоды VD4, VD5 создают напряжение смещения, необходимое для совместимости уровней входного и выходного сигналов в схеме. В закрытом состоянии схемы резистор R2 задает ток через смещающие диоды, обеспечивая требуемое увеличение порога запирания транзистора VT1.

Воткрытом состоянии схемы транзистор VT1 находится в режиме насыщения

ивыходное напряжение схемы равно напряжению насыщения коллектора транзистора UКН, а в закрытом состоянии оно близко к напряжению Еk. Схема задерживает сигнал при выключении. Это связано с рассасыванием избыточного заряда в базе, накопленного в режиме насыщения и наличием паразитных емкостей.

При подаче на все входы высокого уровня напряжения (логическая единица) входные диоды VD1 – VD3 смещаются в обратном направлении, и ток, протекающий через резистор R1, поступает в базу транзистора VT1 и вызывает его насыщение. Напряжение на выходе схемы равно напряжению нуля. Если на любом из входов схемы появляется низкий уровень напряжения, соответствующий уровню логического нуля, то соответствующий диод на входе открывается, диоды VD4, VD5 закрываются,

иток, протекающий через резистор R1, переключается из базовой цепи транзистора в цепь источника входного сигнала. Транзистор VT1 закрывается, выходное коллекторное напряжение схемы возрастает до напряжения Еk. Источник питания Е1 обеспечивает насыщение транзистора VT1.

2.12. Транзисторные элементы с непосредственной связью (НСТЛ)

Схема НСТЛ-элемента приведена на рис. 2.15.

Схема ЛЭ образована соединением коллекторов нескольких (на рисунке – трех) транзисторов. Здесь применена непосредственная связь выхода предыдущего каскада со входом последующего. Если на все входы поступают низкие уровни напряжения (логический нуль), то все три транзистора VT1 – VT3 закрыты и на выходе напряжение равно +Еk (без учета подключения ЛЭ к нагрузке), что соответствует уровню логической единицы.

38

|

|

|

|

|

|

|

|

|

|

|

о + Ek |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

R k |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Х |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

оY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

Х |

|

|

|

|

Х |

|

|

|

|

|

|

Х |

|

|

1 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y = X1+ X2+ X3 |

|||||||||

|

1 о |

|

|

|

о2 |

|

|

|

|

о3 |

|

|

|

|

|

|

|

1 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х2 |

|

|

о |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

VT1 |

|

|

|

VT2 |

|

|

|

|

VT3 |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х3 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

б |

|

|

|

|

|||||

Рис. 2.15. Принципиальная схема (а) и функциональное обозначение (б) НСТЛ-элемента

Если хотя бы на один вход поступает высокий уровень напряжения (логическая единица), то соответствующий транзистор открывается и насыщается и выходное напряжение снижается до Uкн , что соответствует логическому нулю.

При подаче логической единицы на большее число входов насыщается большее число транзисторов, но уровень выходного потенциала почти не изменяется и остается близким к нулю. Таким образом здесь реализуется операция ИЛИ-НЕ. При работе схемы на однотипные элементы уровень логической единицы определяется значением напряжения насыщения базы равным примерно 0,7–0,8 В кремниевых транзисторов, а значение напряжения насыщения коллектора равно 0,2–0,3 В. Такая малая разница уровней напряжения между логической единицей и нулем снижает помехоустойчивость данной схемы, но схема элемента НСТЛ отличается простотой и требует относительно небольшого числа компонентов, в результате чего эти элементы имеют особые преимущества для миниатюризации.

2.13. Транзисторно-транзисторные логические элементы

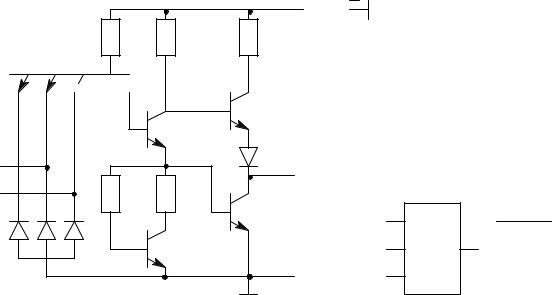

Схема ТТЛ ЛЭ, выполняющего логическую функцию И-НЕ, серии 155 представлена на рис. 2.16. Схема содержит входной каскад, реализующий функцию И, фазоинверсный каскад с источником тока и выходной каскад с активной нагрузкой.

39

X1

Uвх X2 X3

VD1 – VD3

|

|

+о Eп о |

R1 |

R3 |

R5 |

VT1

VT1

|

VT4 |

|

|

|

|

VT2 |

|

|

|

|

VD4 |

|

|

|

|

о Y |

|

|

|

R2 |

R4 |

|

|

|

|

VT5 |

Х1 |

& |

Y = X1 X2 X3 |

|

Uвых |

|||

|

Х2 |

|

||

|

VT3 |

|

о |

|

|

о |

Х3 |

|

|

|

а |

|

б |

|

Рис. 2.16. Принципиальная схема (а) ТТЛ-элемента серии 155 и его функциональное обозначение (б)

Эмиттеры транзистора VT1 служат входами логического элемента и соединены с шиной нулевого потенциала через обратно-смещенные антизвонные диоды VD1 - VD3. Эти диоды служат своего рода демпфером, защищая от отрицательного входного напряжения транзистор VT1. При поступлении хотя бы на один эмиттер потенциала, близкого к нулю, через эмиттер начинает вытекать базовый ток транзистора VT1, создавая на входе ток логического нуля, ограничивающийся сопротивлением резистора R1. В таком режиме потенциал коллектора VT1 низок и транзисторы VT2 и VT5 закрыты. Транзистор VT4 открыт, обеспечивая на выходе уровень напряжения логической единицы:

U1вых Еп IбVT4 R3 UVD4 .

Если на все эмиттеры транзистора VT1 подать напряжение U1вх, равное примерно напряжению питания Еп, то эмиттерные токи VT1 резко уменьшатся (входные токи логических единиц), а базовый ток уйдет в коллектор, создавая на базе транзистора VT2 высокий потенциал. Транзистор VT2 открывается, запирая при этом транзистор VT4 и отпирая транзистор VT5. Транзистор VT5 входит в насыщение, обеспечивая на выходе напряжение, равное примерно 0,4 В. Это напряжение есть напряжение логического нуля U0вых (положительная логика).

40

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |