Материал: Захаров, Сайфутдинов - Вычислительная техника

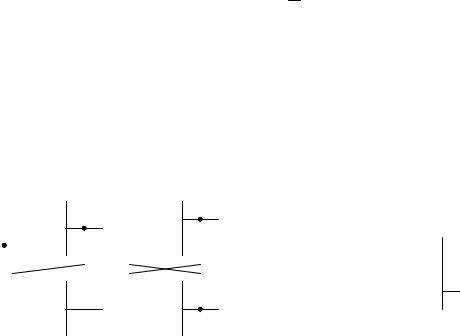

Карта Карно, описывающая работу синхронного RS-триггера на элементах И-НЕ, представлена на рис. 4.7. Используя карту Карно, можно получить минимальную булеву функцию для описания работы синхронного RS-триггера:

|

|

|

Qt+1 = |

|

|

t Qt |

|

t Qt CtSt . |

|

|

||||

|

R |

C |

|

|

||||||||||

|

|

|

|

|

|

|

|

Ct St |

|

|

||||

|

00 |

01 |

|

11 |

|

10 |

|

|||||||

00 |

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

|

0 |

|

|

|

|

0 |

|

||||||

|

|

|

|

|

1 |

|

|

|||||||

RtQt |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

01 |

|

|

1 |

|

1 |

|

|

|

|

1 |

|

1 |

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

|

|

|

*1 |

|

0 |

|

||

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

|

|

|

*1 |

|

0 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.7. Структура карты Карно для синхронного RS-триггера

Отсюда видно, что синхронный RS-триггер принимает состояние 1, если на входы С и S поступают уровни 1, или сохраняет единичное состояние Q при отсутствии единичных сигналов на входах С или R. Общее время установки состояния триггера t равно сумме задержек передачи сигнала через цепочку из трех логических элементов с задержкой t в каждом:

t = 3tЗср .

При этом длительность синхросигнала tc на входе С должна быть равна или превышать время переключения tT.

Длительность паузы tп между двумя сигналами на входе С должна быть достаточной для переключения входных элементов в схеме 1 (рис. 4.6):

tп 3tЗср .

Следовательно, минимальный период повторения синхронизирующих сигналов на входе С равен 4t, а наибольшая частота переключений

Fmax =l/4t Зср .

81

4.6. D-триггер

Триггер D-типа или триггер-задержка это синхронный триггер с одним информационным входом D, реализующий логическую функцию

Qt+1 = Сt Dt Ct Qt ,

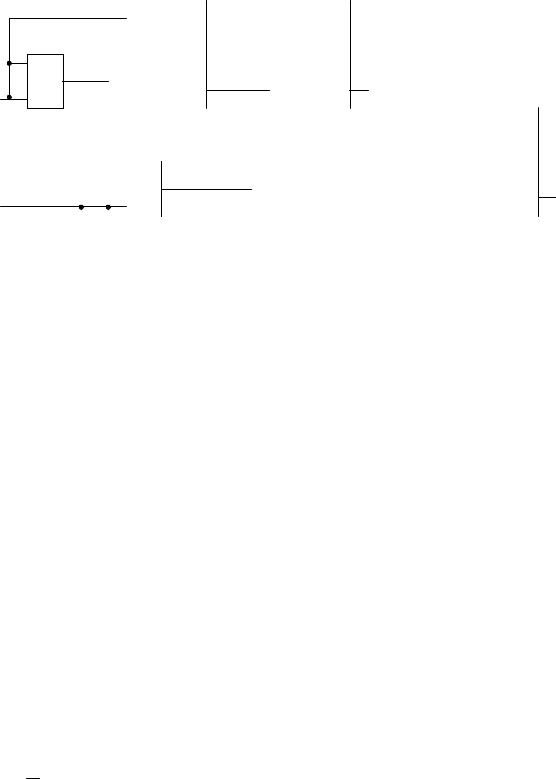

то есть значение сигнала на выходе Q триггера на t+1 такте (при Сt = 1) определяется значением входного сигнала D на предыдущем t такте. Основное назначение D-триггера заключается в задержке информации на один такт. Схема D-триггера на элементах И-НЕ приведена на рис. 4.8, а, а условное обозначение триггера на рис. 4.8, б.

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

& |

o |

|

|

|

|

|

& o |

|

|

Q |

|

|

|

|

|

|||||||||

С |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

T |

|

|

|

Q |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

o |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

& o |

|

|

|

& o |

|

|

Q |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

б |

|

|

|||

Рис. 4.8. Схема D-триггера на элементах И-НЕ (а) и его условное графическое обозначение (б)

В момент времени t действия тактового импульса, соответствующего появлению сигнала 1 на входе D, на выходе триггера Q единичного напряжения еще нет: оно появится только после окончания тактового импульса и может быть использовано только при поступлении тактового импульса в момент времени t+1, т. е. с задержкой на один такт.

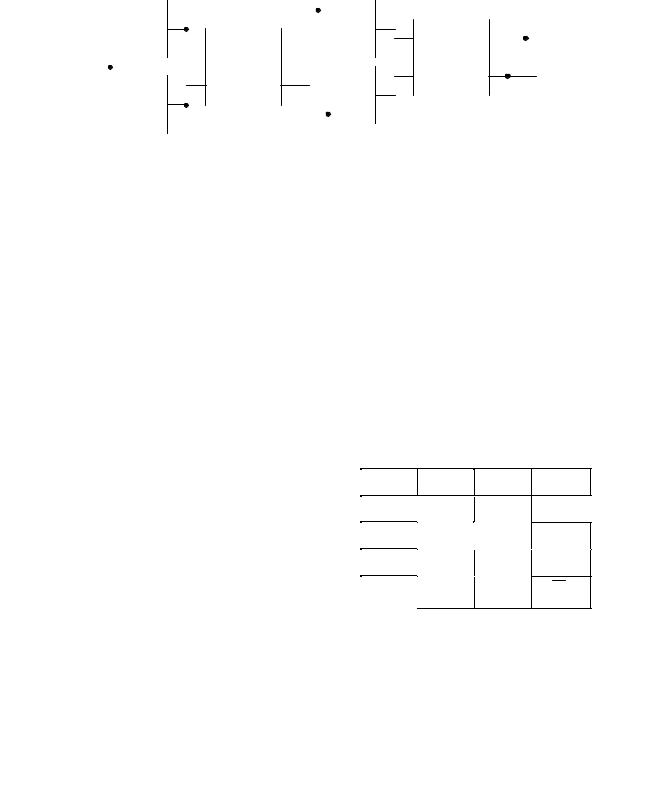

D-триггер (рис. 4.9, а) может быть построен на двух синхронных RS-триггерах Т1 и Т2 и двух инверторах Э1 и Э2. Такую схему триггера называют схемой «ведущийведомый» или двухступенчатым триггером. Его условное обозначение показано на рис. 4.9, б. Как и синхронные RS-триггеры Т1 и Т2, элементы Э1 и Э2 выполнены на элементах И-НЕ. Информационным входом триггера является вход D. Вход С служит для подачи тактовых импульсов. Пусть на вход D поступил сигнал 1. При D = l напряжение на входе Т1 соответствует сочетанию сигналов S = l, R = 0. Появление очередного тактового импульса на входе С приведет к установлению триггера в состояние, при котором напряжение на его выходе равно единице.

82

Э1 |

|

& |

o |

D |

|

С

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

S |

|

T1 |

|

|

S |

T2 |

|

|

|

Q |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

C |

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

R |

|

o |

Q |

|

|

R |

o |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Э2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

TT |

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

& o |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

o |

|

Q |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

|

||||

Рис. 4.9. Схема двухступенчатого триггера (а) и его условное графическое обозначение (б)

На входах R и S триггера Т2 появляется сочетание сигналов S = l, R = 0. Однако во время действия тактового импульса напряжение на выходе инвертора Э2 равно нулю. Сигнал на входе С триггера Т2 является нулевым и переключение триггера Т не происходит. Однако как только закончится тактовый импульс, сигнал на входе С триггера Т2 принимает значение 1 и триггер Т2 переключится в состояние единица. Если на входе D напряжение приняло нулевой уровень, то на выходе Э1 напряжение соответствует единичному значению. На триггер Т1 подается сочетание входных сигналов S = 0, R = l, которое должно установить триггер T1 в состояние 0. Это произойдет во время действия очередного тактового импульса, когда напряжение на выходе элемента Э2 равно 0. Поэтому, хотя на входы триггера Т2 и будет во время действия тактового сигнала подаваться сочетание сигналов S = 0, R = 1, переключение триггера не произойдет. После окончания действия тактового импульса на выходе триггера Т2, напряжение примет нулевой уровень. Двухступенчатые D-триггеры обладают расширенными функциональными возможностями, например, при соединении инверсного выхода Q со входом D образуется триггер Т-типа.

83

4.7. Универсальный JK-триггер

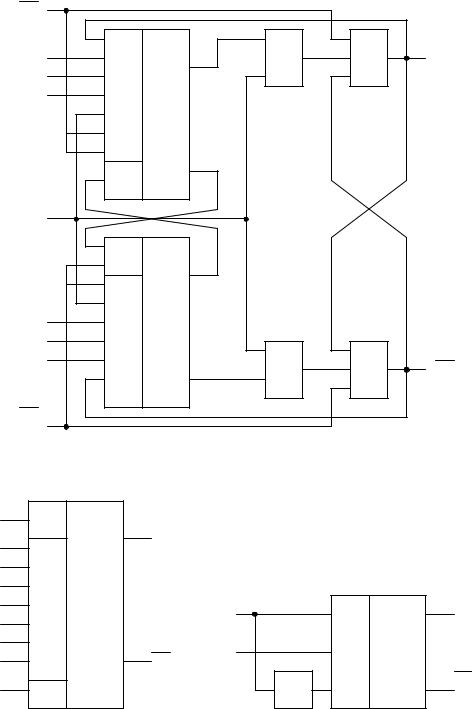

Универсальный JK-триггер, схема которого приведена на рис. 4.10, представляет собой двухступенчатый синхронный триггер.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

|

& o |

|

|

|

|

|

|

|

|

|

|

& o |

|

|

|

|

|

|

|

|

Q |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

o S |

T2 |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

C |

|

|

|

|

o S |

T1 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

o R |

o |

|

|

Q |

|||||||||

|

|

|

|

|

|

o R |

o |

|

|

|

|

|

|

|

|

|

||||||||||

K |

|

|

|

|

|

|

|

& |

o |

|

|

|||||||||||||||

|

& o |

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.10. Схема JK-триггера

Схема JK-триггера состоит из двух асинхронных RS-триггеров с инверсными входами и двух комбинационных устройств, каждое из которых содержит две схемы И-НЕ с тремя входами каждая. Закон функционирования JK-триггера задается таблицей 4.4. JK-триггер отличается от синхронного RS-триггера тем, что не имеет запрещенных комбинаций сигналов на входах J и К. Кроме того, при J = K = 1 триггер изменяет свое состояние на противоположное, т. е. работает как триггер со счетным входом (Т-триггер).

Сt |

0 |

0 |

0 |

0 |

Jt |

0 |

0 |

1 |

1 |

Kt |

0 |

1 |

0 |

1 |

Qt |

Qt |

Qt |

Qt |

Qt |

Qt+1 |

Qt |

Qt |

Qt |

Qt |

|

|

|

|

|

|

|

Таблица 4.4 |

|

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

Qt |

Qt |

Qt |

Qt |

Qt |

0 |

1 |

Q t |

При С = 0 входы J и К заблокированы и, следовательно, оказываются заблокированными входы S и R триггера Т1. При С = 1 в соответствии с информационными сигналами на входах J и К устанавливается состояние ведущего триггера Т1. При этом на входы S и R ведомого триггера Т2 поступают сигналы, при которых его предыдущее состояние сохраняется. При С = 0, когда входы триггера Т1 закрыты для входной

84

информации, входы триггера Т2 открываются и состояние ведущего триггера воспринимается ведомым триггером. Одним из широко используемых вариантов построения является схема JK-триггера с входной логикой (рис. 4.11, а). Условное обозначение триггера дано на рис. 4.11, б.

S |

|

|

|

|

|

|

|

|

|

|

|

& |

1 |

o |

1 |

o |

|

& o |

Q |

3K |

|

|

o |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

o |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

& |

1 |

|

|

|

|

|

|

|

|

|

o |

|

|

|

|

|

|

3J |

|

|

|

|

1 |

|

|

& o |

|

|

|

& |

o |

o |

o |

|

Q |

||

|

|

|

|

|

|

|

|||

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

о |

S |

ТТ |

Q |

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

|

|

D |

|

|

|

|

Q |

|

C |

|

|

|

|

D |

TT |

||

|

& |

|

|

|

|

|

|

||

|

|

|

C |

|

|

|

|

|

|

|

K |

о |

Q |

|

|

C |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

Q |

|||

о |

R |

|

|

|

|

1 о |

K |

о |

|

|

|

б |

|

|

|

|

|

в |

|

Рис. 4.11. Схема JK-триггера со входной логикой (а);

его условное графическое обозначение (б); триггер D-типа на основе JK-триггера (в)

85

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |