Материал: mekhatronika_UrGUPS

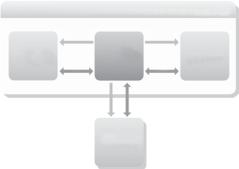

Цифровой сигнальный процессор

|

Ша |

Ша |

|

Память |

ЦПУ |

|

Память |

программ |

Шд |

данных |

|

|

Шд |

|

Внешняя

память

Рис. 3.6. Гарвардская архитектура DSP

Лучшие современные DSP имеют следующие параметры:

–тактовая частота – 1 ГГц и выше;

–многоядерность;

–наличие двухуровневой кэш-памяти (сверхоперативная буферная память для промежуточного хранения данных);

–встроенные многоканальные контроллеры прямого доступа к памяти;

–выполнение до 8 параллельных инструкций за такт;

–быстродействие порядка нескольких тысяч MIPS и MFLOPS;

–совместимость со стандартными шинами (PCI и др.). Области применения DSP:

–управление динамичными технологическими процессами;

–коммуникационное оборудование;

–анализаторы спектра;

–распознавание речи и изображений;

–речевые и музыкальные синтезаторы;

–системы гидро- и радиолокации;

–другие области, где необходима быстродействующая обработка сигналов (в том числе в реальном времени).

По назначению DSP делятся на две группы:

1.DSP общего назначения.

2.Проблемно-ориентированные DSP.

«Проблемная ориентация» обычно относится к набору встроенных специализированных периферийных устройств. Например, DSP, предназначенные для управления электродвигателями, могут содержать на кристалле генераторы сигналов ШИМ, контроллеры локальной промышленной сети и т. д. В цифровых фото- и видеокамерах

41

применяются DSP с модулями кодирования / декодирования MP3, JPG, AAC, MPEG1, MPEG4 и др. Среди проблемно-ориентированных DSP выделяются гибридные DSP – специализированные устройства, сочетающие в себе функцию микроконтроллера и цифрового сигнального процессора. Обычно такие изделия предназначены для выполнения одной функции – например, управления электрическими двигателями или другими объектами в реальном масштабе времени.

Американская компания Texas Instruments производила цифровые сигнальные микропроцессоры на двух DSP платформах TMS320C2000 и TMS320C6000 для встроенных приложений.

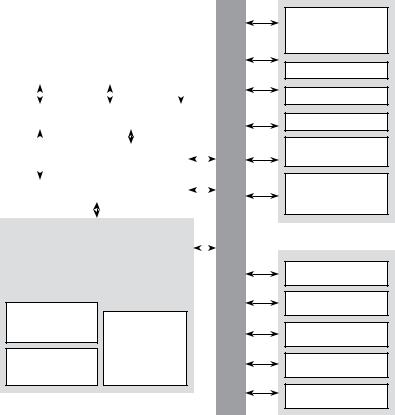

Блок-схема архитектуры цифрового сигнального процессора TMS320F28335 платформа C2000 приведена на рис. 3.7.

|

Код безопасности |

|

|

|

|

|

|

|

|

|

||||||||

|

512 кБ |

|

|

68 кБ |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||||||||

|

флэш |

|

|

|

ОЗУ |

|

|

|

Загрузоч- |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

ное ПЗУ |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Шина памяти |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

устройств |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Контроллер прямого |

|

|

|

|

|||||||||||

|

|

|

|

|

доступа к памяти |

|

|

|

|

периферийных |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Управление прерываниями |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

32-разр. ядро С28хТМ |

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Шина |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Умножитель |

|

|

|

АЛУ |

|

|

|

|

|

|

|||||||

|

32х32-разр. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32-разр. таймеры (3)

Real-Time

JTAG

32-разр. устройство

сплавающей

запятой

18 ШИМ (6 ШИМ высокого

разрешения

6 САР

2 QEP

12-разр. АЦП

88 портов ввода/вывода

16/32-разр. интерфейс внешней памяти

SPI

3 SPI

2 McBSP

I2C

2 CAN

Рис. 3.7. Блок-схема архитектуры TMS320F28335

42

Производительность данного процессора достигает 300 миллионов инструкций с плавающей точкой в секунду (MFLOPS) при работе на тактовой частоте 150 МГц. Цифровой сигнальный микропроцессор TMS320C6201 (платформа C6000) на тактовой частоте 200 МГц позволяет развить производительность 1600 миллионов инструкций с фиксированной точкой в секунду (MIPS).

Программируемые вентильные матрицы (FPGA – Field Programmable Gate Arrays) представляют собой интегральные микросхемы, обладающие уникальным сочетанием очень высокой производительности (скорость вычислений соизмерима с аппаратными вычислительными средствами) с возможностью программирования как обычных микропроцессорных устройств. На выходе блоков FPGA можно сформировать широтно-модулированный сигнал, который имеет цифровое представление.

Микросхема FPGA состоит из следующих основных блоков:

–блок ввода-вывода (БВВ), осуществляющий соединение внутренней логики кристалла с выводами корпуса микросхемы;

–конфигурируемые логические блоки (КЛБ), реализующие логические и регистровые функции;

–блочная память;

–модули управления синхронизацией (DLL);

–трассировочные ресурсы для соединения всех элементов. Программирование микросхем FPGA в отличие от традиционных

логических микросхем осуществляет пользователь. Для этого применяются специальное программное обеспечение, которое включает в себя: модули текстового и схемного ввода, моделирования, автоматической трассировки, создания и загрузки конфигурационных данных, специальные библиотеки макросов. Разработчик с внешнего устройства имеет возможность многократно загружать проект в микросхему и тестировать ее работу на реальном изделии [1].

В системах управления мехатронными и робототехническими системами преобладают встроенные контроллеры движения, которые технологически реализованы на отдельной плате. Лишь в некоторых случаях используются специализированные аппаратно оформленные сепаративные контроллеры.

На практике широко применяются микроконтроллеры семейства AVR фирмы Atmel. Это одна из самых популярных в наше время микропроцессорных серий. Микроконтроллеры серии AVR относятся к классу восьмиразрядных микроконтроллеров. Это означает, что подавляющее большинство операций процессоры производят с восьми-

43

разрядными двоичными числами. Все ячейки памяти и большинство регистров микроконтроллера также восьмиразрядные. Исключение составляет память программ, которая состоит из шестнадцатиразрядных ячеек. Микроконтроллеры AVR изготавливаются по КМОП – технологии, благодаря которой они имеют низкий ток потребления. Большинство команд микроконтроллера выполняются за один такт. Быстродействие составляет миллион операций в секунду (MIPS) при тактовой частоте 1 МГц. Программирование микроконтроллера ведется на языках Ассемблер и СИ [10].

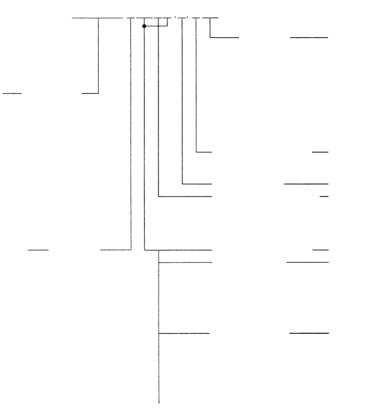

Более совершенным является микроконтроллер MSP-430 фирмы Texas Instruments. Система обозначений микроконтроллеров MSP-430 (production code), применяемая Texas Instruments, показана на рис. 3.8 [11].

MSP430XXXXX(A)XXX

наименование

семейства

тип памяти Е – EPROM

P – OTP (однократная) F – FLASH

C – ROM

U – User S/W (масочная)

тип корпуса

PW – TSSOP20/28

DW – SOWB20/28 JL – CDIP20JL DL – SSOP48/56 PG – QFP64 1 мм

PM – QFP64 0,5 мм PJM – QFP100

PN – QFP80

PZ – QFP100

FN/FZ – PLCC, JLCC HFD – CPF100

температурный диапазон

С – коммерческий (0...+70°С)

I – индустриальный (–40°С)...+85°C

зарезервировано размер внутренней памяти

0–1 кбайт |

3–8 кбайт |

6–24 кбайт |

1–2 кбайт |

4–12 кбайт |

7–32 кбайт |

2–4 кбайт |

5–16 кбайт |

8–48 кбайт |

|

|

9–64 кбайт |

конфигурация кристалла с драйвером LCD

31 – базовая версия

32 – с 14-разрядным АЦП

33 – с USART

41 – с FLL

43 – с 12-разрядным АЦП

44 – с 12-разрядным АЦП, MPY, USART

без драйвера LCD

11 – базовая версия 11х1 – базовая версия + компаратор А 12 – с USART

13 – с 12-разрядным АЦП

14 – с 12-разрядным АЦП, MPY, USART

15 – с 12-разрядным АЦП/ЦАП, USART, DMA

16 – с 12-разрядным АЦП/ЦАП, USART, DMA, MPY

Рис. 3.8. Система обозначений MSP-430

44

Одно из преимуществ микроконтроллеров MSP-430 – чрезвычайно простая и освоенная система команд. Предоставленные пользователю средства разработки программного обеспечения позволяют работать как в классическом ассемблеровском коде, так и на языках высокого уровня (например, на СИ). Фирма Texas Instruments выпускает отладочные средства (для отладки программ) – так называемые Starter Kits (стартовые наборы), в комплект которых входят: печатная плата с установленным микроконтроллером, ЖКИ-индикатор, кнопки, контактные разъемы для подключения других электронных компонентов. Еще одно направление отладочных средств – эмуляторы (программа или микросхема, позволяющая осуществить эмуляцию – точное выполнение микроконтроллером программы, записанной в системе другой ЭВМ).

Структура кристалла из «линейки» MSP-430 показана на рис. 3.9. Архитектура MSP-430 является дальнейшим развитием известной архитектуры ЭВМ PDP11, ныне ставшей достоянием истории. Буква «F» в обозначении на рис. 3.9 говорит о том, что микроконтроллер имеет встроенную внутреннюю flash-память (рис. 3.8), которая может быть электрически многократно перепрограммирована.

Структура MSP-430 использует 16-битную упрощенную организацию системы команд RISC-типа (Reduced Instruction Set Computer), которая может производить операции не только над байтами, но и над словами (напомним, что машинное слово состоит из двух байт). Центральный процессор (CPU) идентичен для всех представителей семейства и состоит из трехступенчатого конвейера инструкций, 16разрядного арифметик-логического (ALU) устройства, 16 внутренних регистров (четыре из которых используют в качестве счетчика команд – PC, указателя стека – SP, регистра состояния – SR, генератора констант – CG). Счетчик команд предназначен для фиксации текущего адреса исполняемой команды, указатель стека хранит данные о так называемой стековой памяти, регистр состояния сохраняет результаты выполнения команд, генератор констант формирует наиболее часто используемые целые числа. Остальные 12 регистров используются по усмотрению пользователя. ALU выполняет простейшие арифметические действия (сложение, вычитание, сравнение) и логические операции («и», «или», «исключающие «ИЛИ»»). В состав некоторых модификаций MSP-430 входит 16-разрядный аппаратный умножитель, осуществляющий аппаратное умножение (не в ALU). Умножать можно как комбинации 16-разрядных чисел, так и комбинации 8-разрядных и 16-разрядных чисел. При этом поддержива-

45