I/O modules • 235

Incremental-encoder-interface 750-631

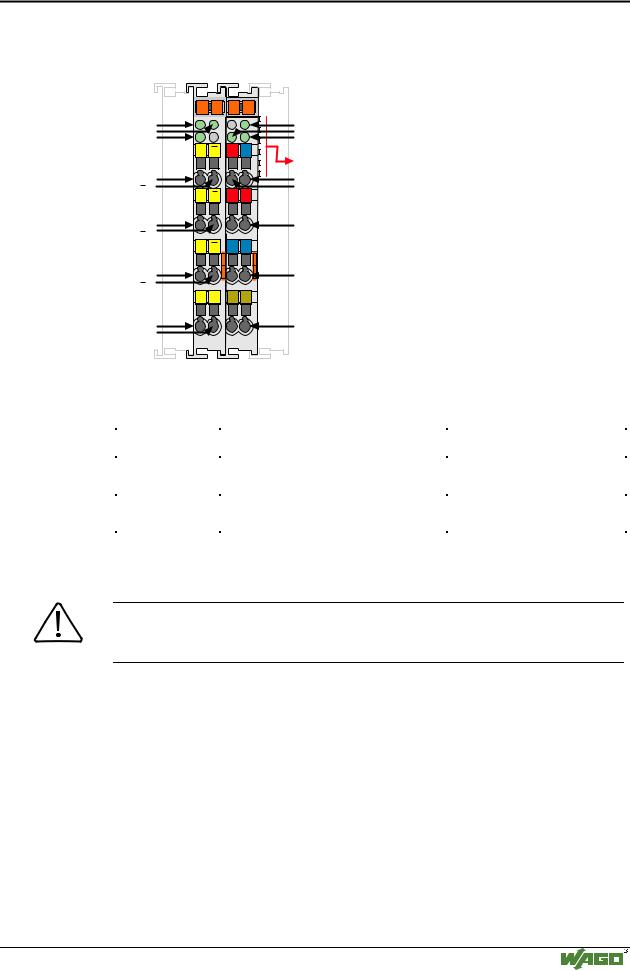

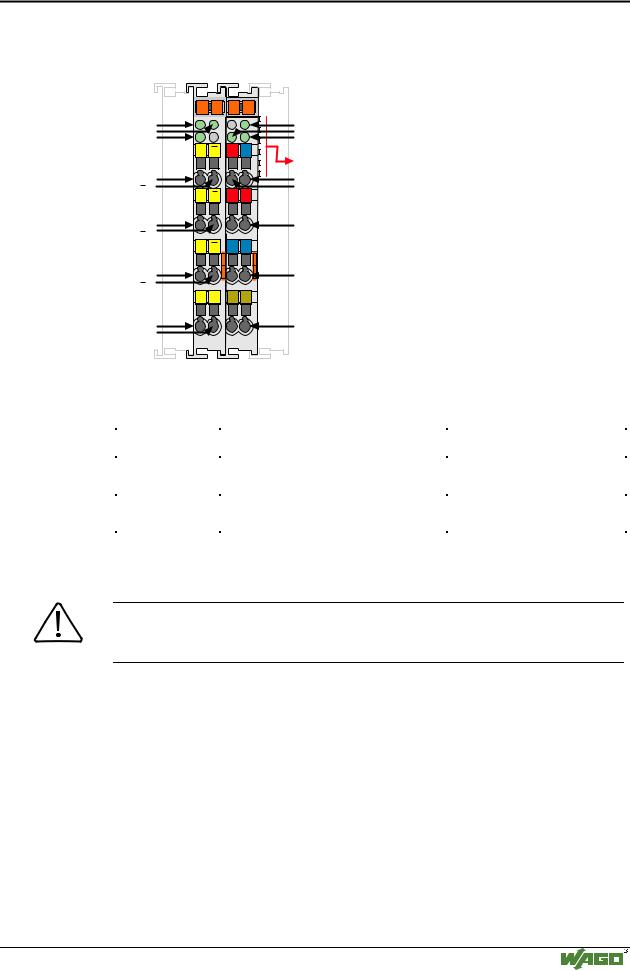

Most quadrature encoders have an Index signal, or Z rev, as well as the incremental signal. This signal provides one pulse per revolution with a duration equal to an incremental pulse.

The inputs to the quadrature encoder module must be supplied from an encoder with Line Driver Outputs for proper operation. The 5 Volt DC output may be used to power the encoder. The 24 Volt DC input supply must be provided from an external power supply.

The Gate and Latch inputs are 24 Volt DC.

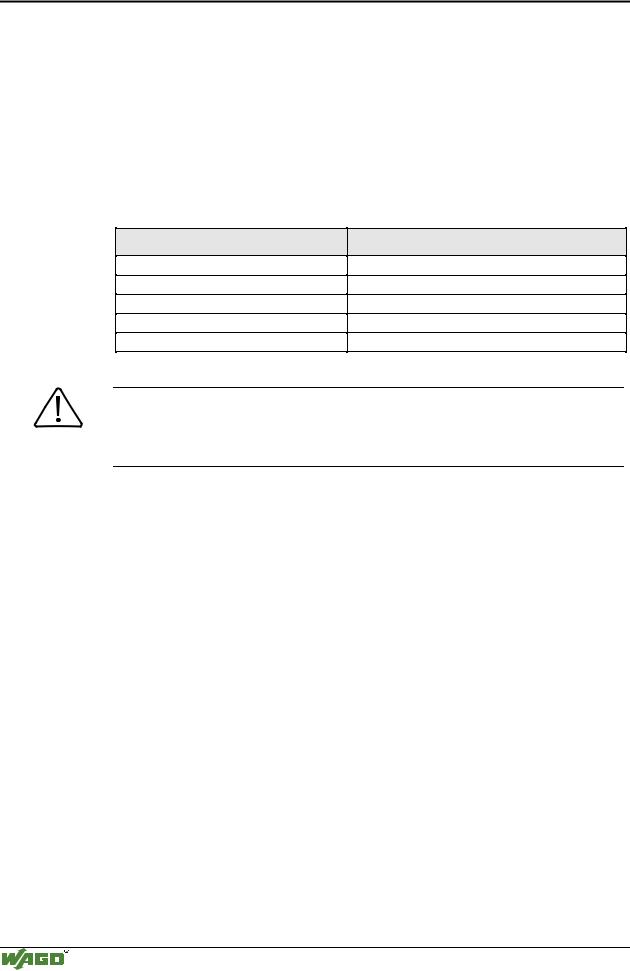

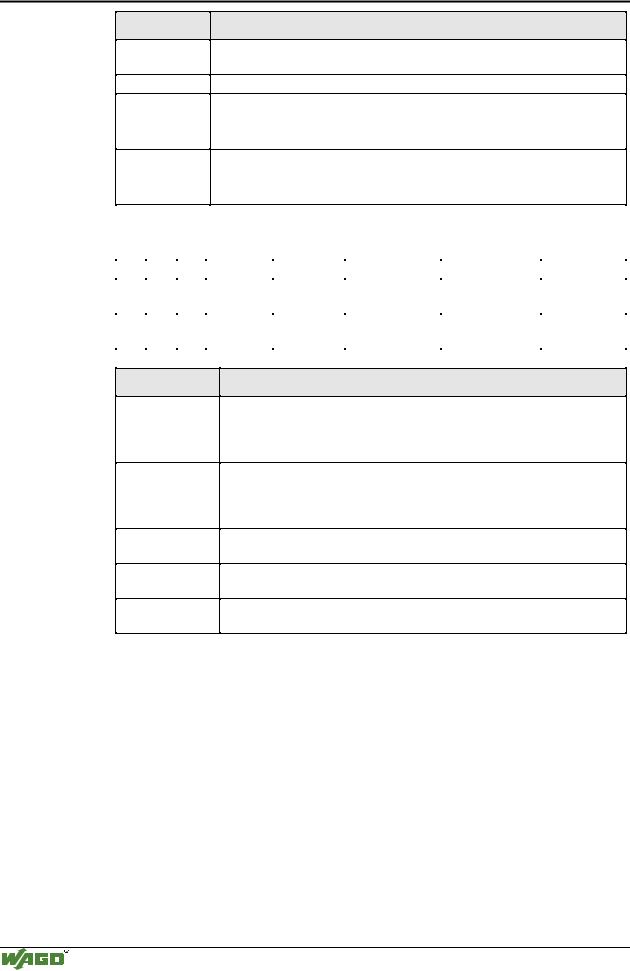

Module Inputs and Outputs:

Input |

Type |

Function |

Signal A and |

Input, TTL |

Incremental pulse signals for channel A |

Signal -A |

|

|

Signal B and |

Input, TTL |

Incremental pulse signals for channel B |

Signal -B |

|

|

Signal C and |

Input, TTL |

Index pulse signals |

Signal -C |

|

|

Shield |

Input |

Shield connection for encoder wiring |

Sensor 0V |

Output |

Supply return for encoder supply |

Sensor +5V |

Output |

5 Volt DC supply for encoder |

+24V |

Input |

24 Volt DC supply, field connection |

0V |

Input |

Supply return, field connection |

Gate |

Input, 24V |

24 Volt DC input for gate signal |

Latch |

Input, 24V |

24 Volt DC input for Latch signal |

The Input Gate stops the counter. Only 0 V or an open connection will initialize the counter.

24 V stops the counting process.

The input Latch controls the writing of the actual counter value into the Latch register. This input is activated by the control bit EN_LATEXT ("1"). EN_LACT has to be deactivated ("0"). The first change from 0 V to 24 V at the Latch input writes the actual counter value into the Latch register.

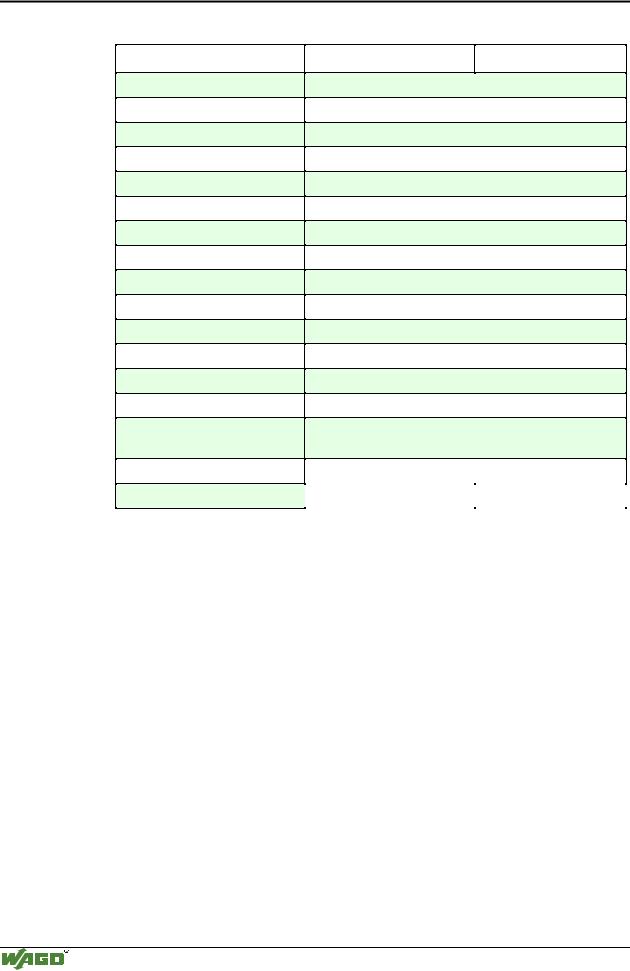

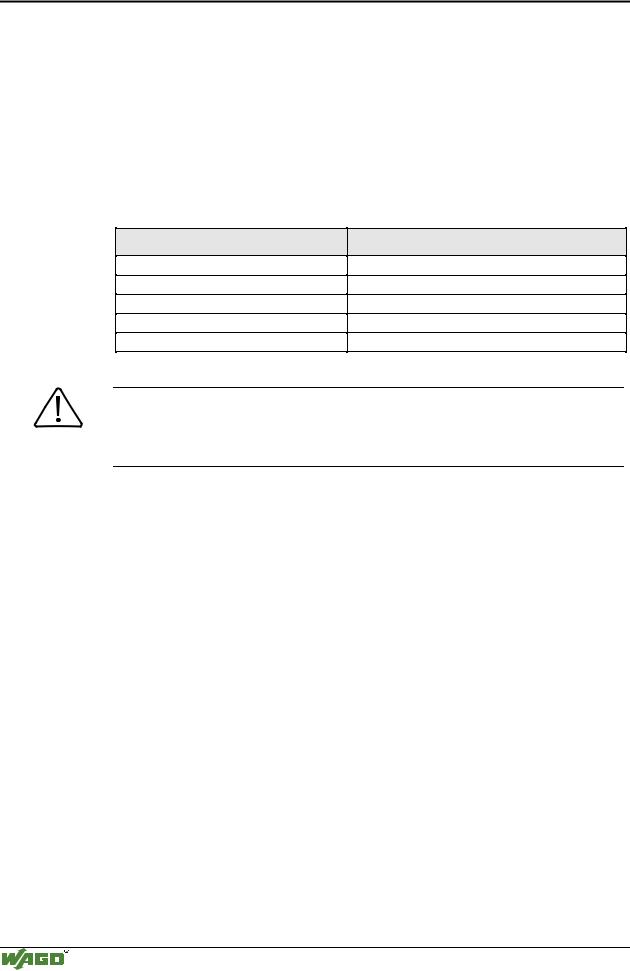

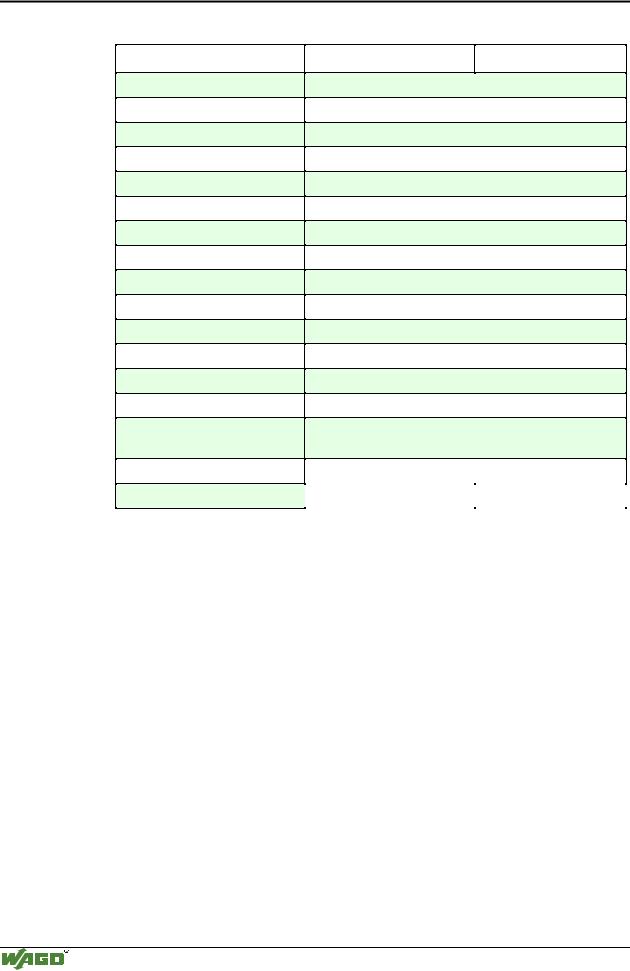

The control byte has the following bits:

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

0 |

x |

CFAST_M |

x |

x |

CNT_SET |

EN_LATEXT |

EN_LATC |

0 |

x |

Operating |

x |

x |

Counter set |

Release Latch |

Release |

|

|

mode |

|

|

|

|

Index Pulse |

Please note Bit 7 is a reserved bit and must always be set to 0. It is responsible for register communication which is not described in this chapter.

Modular I/O System

ETHERNET TCP/IP