Материал: 999

Блок

управления

SA1

SA2

SA3

SA4

SA5

6

П1 |

|

2 |

1 |

1 |

4 |

D1.1 |

D1.2 |

|

|

1 |

8 |

|

|

|

|

D1.3 |

|

|

1 |

10 |

|

|

|

|

D1.4 |

|

|

|

3 |

& |

& |

5 |

|

||

D2.1 |

D2.2 |

|

20 |

|

|

21 |

& |

7 |

D2.3 |

|

|

|

|

|

22 |

|

|

|

|

6 |

23 |

|

|

=1 |

=1 |

9 |

24 |

D3.2 |

|

D3.1 |

|

25

=1

D3.3

Блок индикации

HL2

HL4

HL8

HL1

HL3

HL5

HL7

HL6

HL9

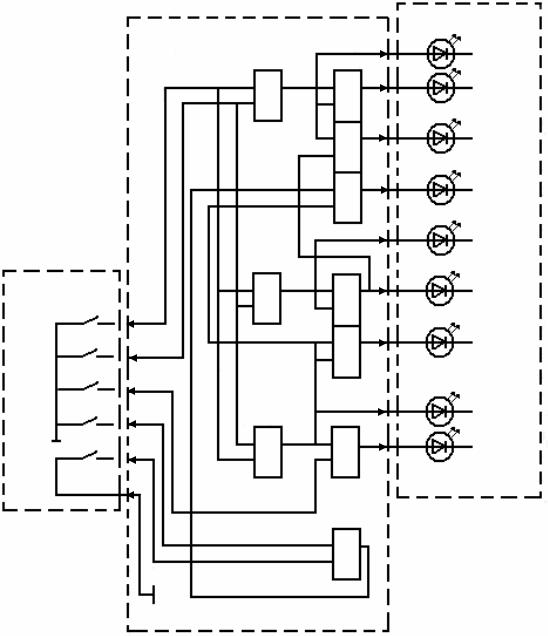

Рис. 2 Схема платы П1 и ее подключение к основному блоку

7.Исследовать одноразрядный полусумматор, используя ключи SA1, SA2 в качестве булевских переменных X1, Х2, светодиод HL8 для индикации суммы, a HL5 – переноса. Выделить и изобразить, часть схемы, реализующую полусумматор. Доказать тождественность уравнений полусумматора функциям выделенной схемы. Экспериментально исследовать схему. Синтезировать полусумматор на элементах И-НЕ (карта 1.9).

8.Исследовать устройство побитового сравнения двух двухразрядных чисел Х1Х0 и Z1Z0. В качестве X1, Х0 использовать SAl, SА4, a Z1, Z0 – SА2, SA5. Результат сравнения наблюдать на светодиоде HL1. Два числа равны, если X1=Z1 и X0=Z0. Составить таблицу истинности и по ней

7

логическое уравнение условия равенства чисел. По уравнению синтезировать устройство сравнения на элементах И-НЕ. Выделить и изобразить схему сравнения на элементах D1, D3. Составить уравнение функционирования схемы и, преобразовав его к СДНФ, сравнить с предыдущим. Исследовать работу схемы экспериментально (карта 1.8).

9. Исследовать трехразрядное устройство проверки на нечетность. Источниками сигнала являются тумблеры SAl, SA2, SA3. Индикатором нечетного количества истинных бит в слове – HL9. Выделить, и изобразить схему контроля. Получить экспериментально таблицу истинности и по ней составить уравнение в СДНФ. Составить уравнение в СДНФ непосредственно по виду схемы. Сравнить оба полученных уравнения (карта 1.7).

Отчет о работе

Отчет должен содержать:

1.Схему (выделенную из рис. 2) и экспериментальную таблицу истинности функции ИЛИ.

2.Аналогично п.1, но для ИЛИ-НЕ.

3.Аналогично п.1, но для И.

4.Аналогично п.1, но для И-НЕ.

5.Аналогично п.1, но для "исключающего ИЛИ".

6.Схему элемента "исключающее ИЛИ", синтезированного по элементам И-НЕ.

7.Аналогично п.1. но для элемента "исключающее ИЛИ-НЕ".

8.Аналогично п.6, но для элемента "исключающее ИЛИ-НЕ".

9.Схемы (выделенную из рис. 2 и общепринятую условную) полусумматора.

10.Экспериментальные таблицы истинности для суммы и переноса.

11.Аналитическое доказательство тождественности уравнений полусумматора по рис. 2 и по таблице истинности.

12.Схему полусумматора, синтезированного на элементах И-НЕ.

13.Схему сравнения двух чисел (выделенную из рис. 2), экспериментальную таблицу истинности, логическое уравнение, составленное по схеме.

14.Доказательство эквивалентности уравнения для схемы сравнения по рис.2 и по таблице истинности.

15.Схему проверки на нечетность, таблицу истинности, уравнения в СДНФ, составленные но таблице.

16.Уравнения в СДНФ для схемы проверки нечетности, составленные непосредственно по схеме рис.2.

17.Доказательство эквивалентности уравнения по п.п. 15, 16.

Вопросы для самоконтроля

8

1.Таблицы истинности, логические уравнения, обозначение конъюнкции, дизъюнкции, инверсии, сумматора, а также графические обозначения элементов, реализующих указанные функции.

2.Булевские переменные и их реализация в элементах.

3.Синтез примитивного автомата по таблице истинности.

4.Основные законы алгебры логики.

5.Определение ДНФ и СДНФ.

6.Функциональная полнота логических функций.

7.Приведение булевских уравнений к монофункциональному базису.

ЛАБОРАТОРНАЯ РАБОТА N 2

Исследование триггеров

Цель работы – исследование режимов работы триггеров на ИМС.

Описание сменной платы П2

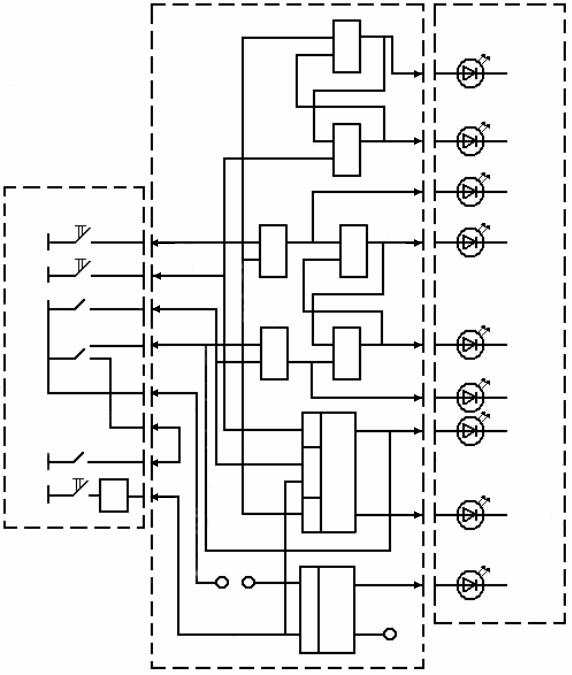

Принципиальная схема платы П2 приведена на рис. 3. Цифры на границах пунктирного прямоугольника означают номера контактов на разъеме X1. Блоки управления и индикации расположены в основном блоке ввода-вывода стенда и используются при работе с данной платой.

Порядок выполнения работы

1.Выделить и изобразить отдельно схемы RS-триггера на элементах ИЛИ-НЕ. В качестве источника сигнала использовать кнопки SB2, SB3. Состояние триггера определять с помощью диодов HL3, HL4.Сигналы управления триггером индицируются со светодиодами HL1, HL2.

Заготовить форму таблицы переходов триггера и экспериментально заполнить ее. Обратить внимание на запрещенное состояние.

2.Аналогично п.1, но для RS-триггера на элементах И-НЕ. Сигналы управления в инверсном виде индицируются светодиодами HL1, HL2.

Блок управления

SB2

SB3

SA1

SA5

SA3

SB1 F

|

9 |

|

|

П2 |

|

& |

Блок индикации |

|

|

|

|

|

|

D1.1 |

|

|

|

|

5 |

|

|

|

HL5 |

|

|

& |

6 |

|

|

HL6 |

|

|

|

D1.2 |

|

|

|

|

|

|

|

|

10 |

|

|

|

HL1 |

19 |

|

|

3 |

|

& |

& |

HL3 |

18 |

D2.1 |

D2.2 |

|

|

|

|

|

20 |

|

|

|

31 |

|

|

4 |

|

& |

& |

HL4 |

|

D2.3 |

D2.4 |

|

24 |

|

|

2 |

|

|

|

HL2 |

26 |

|

|

9 |

|

R |

T |

|

|

HL9 |

||

|

|

||

22 |

D |

|

|

|

|

|

|

27 |

C |

|

|

|

|

|

|

|

|

D3.1 |

8 |

|

S |

HL8 |

|

X1 |

X2 |

|

7 |

|

D |

|

|

|

T |

HL7 |

Y1

CD3.2

Рис. 3 Схема платы П2 и ее подключения к основному блоку

3.Аналогично п.2, но используется RS-триггера в интегральном исполнении на микросхеме D3.1. Выходы D, С не используются (кнопка SB1 не нажата, a SA1 находится в выключенном состоянии). Выходная информация выводится на индикаторы HL9 (прямой выход) и HL8 (инверсный).

4.Выделить и изобразить отдельно схему тактируемого D-триггера на ИМС D3.1. На выходы R, S подать логические единицы. Экспериментально получить таблицу переходов. По полученной таблице составить временную диаграмму напряжений на инверсном выходе по известным сигналам на входах D и С. Провести эксперимент, подтверждающий, что запись

10

информации происходит по фронту синхроимпульсов.

5.На базе ИМС D3.2 путем надлежащей коммутации превратите D- триггер в Т-триггер. Исследовать работу Т-триггера.

6.Соединив перемычки X1 и X2 получить последовательное включение D-триггеров на ИМС D3.1 и D3.2. Манипулируя SA1, наблюдать продвижение информации по системе, используя светодиоды HL9, НL7. Изобразить временные диаграммы процессов.

Отчет о работе

Отчет должен содержать:

1.Схему RS-триггера на элементах ИЛИ--ИЕ и экспериментальную таблицу переходов.

2.Аналогично п.1, но на элементах И-НЕ.

3.Аналогично п.1, но на ИМС D3.1.

4.Схему тактируемого D-триггера, экспериментальную таблицу переходов, временные диаграммы напряжения на инверсном выходе, сигнальном и тактовом входах.

5.Схему Т-триггера на базе D-триггера, экспериментальную таблицу переходов, временные диаграммы.

6.Схему последовательно соединенных двух D-триггеров и временные диаграммы продвижения цифры Е.

Вопросы для самоконтроля

1.Схемы и таблицы переходов тактируемых и нетактируемых RSтриггеров на логических элементах.

2.Схемы и таблицы переходов D, Т, JК-триггеров .на ИМС.

3.Принцип работы двухступенчатых триггеров.

4.Способы превращения JK-триггера на ИМС в RS, D, Т - триггеры.