Материал: Проектирование комбинационных схем цифровых устройств

Проектирование комбинационных схем цифровых устройств

ВВЕДЕНИЕ

С внедрением в промышленность цифровых

технологий появилась возможность строить устройства обработки оцифрованных

сигналов вычислительным методом. Такой способ обладает рядом важных

преимуществ, таких как повышенная точность обработки, меньшая зависимость

параметров от внешних условий, а также возможность реализации таких

обрабатывающих устройств, которые невозможно или трудно было реализовать в

аналоговом виде. Одни из наиболее распространенных узлов цифровых схем -

дешифраторы. Навыки создания дешифраторов необходимы при разработке практически

любого цифрового устройства.

1. Устройство

дешифрации кодов

.1 Описание

дешифратора и структурная схема устройства

Целью задачи является синтез устройства дешифрации кодов двоичных чисел, имеющего «к=7» входов и «I=70» выходов, используя стандартные промышленные ИМС К155ИД3, .

К155ИД3 - двойной высокоскоростной дешифратор. Каждый из дешифраторов микросхемы (рис 1.1.1) имеет 2 адресных входа А0-А1 и вход разрешения Е. Избыточные коды дают на всех выходах высокий уровень. Выходы 0-3 взаимоисключающие, их активные выходные уровни - низкие. Активный уровень для входа Е- низкий.

Состояния выходов дешифратора показаны в таблице

1.1.1

Таблица 1.1.1 - Состояния выходов дешифратора 74LS154

где Н - низкий уровень, В -

высокий уровень.

Структурно-логическая схема дешифратора показана

на рисунке 1.1.1

Рисунок 1.1.1 - Структурно-логическая схема ИМС К155ИД3

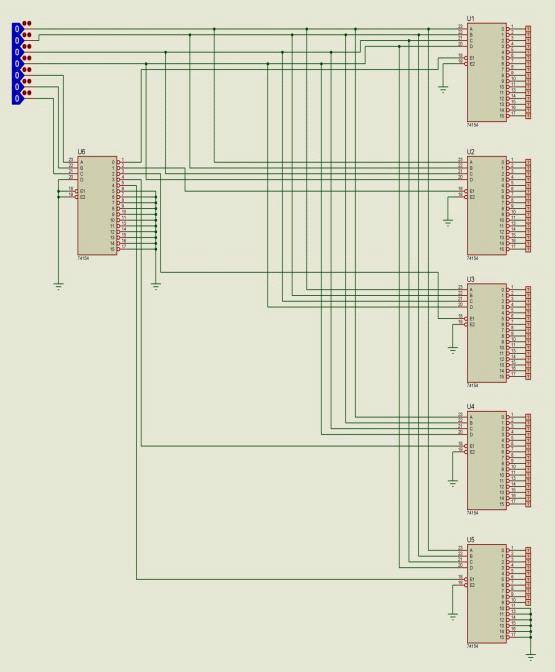

Поскольку число входов устройства k=4, то четыре старших разряда подаются на первую ступень, которая состоит из одного дешифратора К555ИД6. Его выходы соединяются с входами А3 каждого дешифратора второй ступени для управления ими. Так как по заданию число выходов устройства I=70, то необходимо использовать 5 дешифраторов для второй ступени. Четыре младших разряда подаются на адресные входы этих дешифраторов.

Зарубежным аналогом К531ИД14 является ИМС 74LS154.

Таблица 1.1.2 - Таблица дешифрации

|

X0 |

X1 |

X2 |

X3 |

Выход |

X0 |

X1 |

X2 |

X3 |

Выход |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

7 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

8 |

|

0 |

0 |

1 |

0 |

2 |

1 |

0 |

0 |

1 |

9 |

|

0 |

0 |

1 |

1 |

3 |

1 |

0 |

1 |

0 |

10 |

|

0 |

1 |

0 |

0 |

4 |

1 |

0 |

1 |

1 |

11 |

|

0 |

1 |

0 |

1 |

5 |

1 |

1 |

0 |

0 |

12 |

|

0 |

1 |

1 |

0 |

6 |

1 |

1 |

0 |

1 |

13 |

|

|

|

|

|

|

1 |

1 |

1 |

0 |

14 |

Рисунок 1.1.2 - Структурная схема устройства

дешифрации кодов

.2 Расчет

потребляемой мощности и времени задержки

По рисунку 1.1 определим общее число логических элементов, входящих в дешифратор, - N=25. Средняя мощность потерь одного логического элемента - Pср.пот.=10 мВт [2]. Энергопотребление одного дешифратора равно:

![]()

Так как устройство состоит из пяти дешифраторов,

то общее энергопотребление равно:

![]()

Определяем число элементов, участвующих в

распознавании одного любого слова, оно равно К=3. Находим время задержки:

![]()

![]()

Так как наше устройство двухступенчатое, то

общее время задержки передачи сигнала по одному каналу равно:

![]()

Таблица 1.2.1 - Перечень элементов

|

Позиционное обозначение |

Наименование |

Количество |

Примечание |

|

U1;U2;U3; U4;U5 ;U6 |

ИМС К155ИД3 |

6 |

Дешифратор |

2. Коммутатор параллельных

кодов

.1 Описание

мультиплексора и структурная схема устройства

Коммутатор параллельных входов получает заданное

число слов, каждое из которых состоит из заданного количества разрядов. По

заданию число слов - 4, количество разрядов в слове - 8. Следовательно, общее

число входных бит 4*8=32. Количество адресных сигналов будет равно:

![]()

Из справочника [1] выбираем ИМС мультиплексора

К155КП1, который имеет 4 адресных входа и 16 информационных входов. Также

имеется вход разрешения, при подаче на который низкого уровня коммутации

разрешены. Этот мультиплексор позволяет передать на выход сигнал с входа, номер

которого подается на адресные входы.

Таблица 2.1.1 - Состояния выходов ИМС К155КП1

|

Входы |

Выходы W |

||||

|

Информационные входы |

Разрешения S |

|

|||

|

D |

C |

B |

A |

|

|

|

X |

X |

X |

X |

H |

H |

|

L |

L |

L |

L |

L |

E0 |

|

L |

L |

L |

H |

L |

E1 |

|

L |

L |

H |

L |

L |

E2 |

|

L |

L |

H |

H |

L |

E3 |

|

L |

H |

L |

L |

L |

E4 |

|

L |

H |

L |

H |

L |

E5 |

|

L |

H |

H |

L |

L |

E6 |

|

L |

H |

H |

H |

L |

E7 |

|

H |

L |

L |

L |

L |

E8 |

|

H |

L |

L |

H |

L |

E9 |

|

H |

L |

H |

L |

L |

E10 |

|

H |

L |

H |

H |

L |

E11 |

|

H |

H |

L |

L |

L |

E12 |

|

H |

H |

L |

H |

L |

E13 |

|

H |

H |

H |

L |

L |

E14 |

|

H |

H |

H |

H |

L |

E15 |

Количество мультиплексоров соответствует

количеству разрядов в слове. На входы каждого мультиплексора подается по одному

разряду из каждого слова, номер разряда соответствует номеру мультиплексора, а

номер входа мультиплексора соответствует номеру слова. Таким образом, при

подаче какого-либо числа на адресные входы мультиплексоров на выходе будем

иметь слово, номер которого соответствует этому числу.

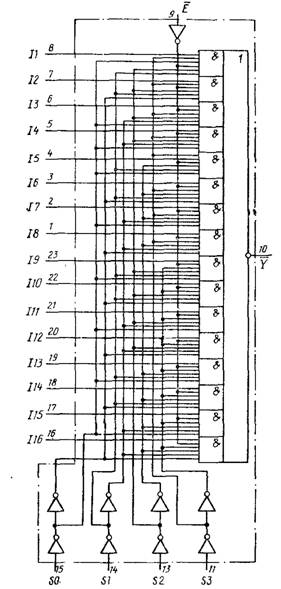

Рисунок 2.1.1 - Структурно-логическая схема мультиплексора К155КП1

дешифратор мультивибратор коммутатор код

Таблица 2.1.2 - Таблица коммутации

|

A0 |

А1 |

А2 |

А3 |

Источник слов |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

2 |

|

0 |

0 |

1 |

1 |

3 |

|

0 |

1 |

0 |

0 |

4 |

|

0 |

1 |

0 |

1 |

5 |

|

0 |

1 |

1 |

0 |

6 |

|

0 |

1 |

1 |

1 |

7 |

|

1 |

0 |

0 |

0 |

8 |

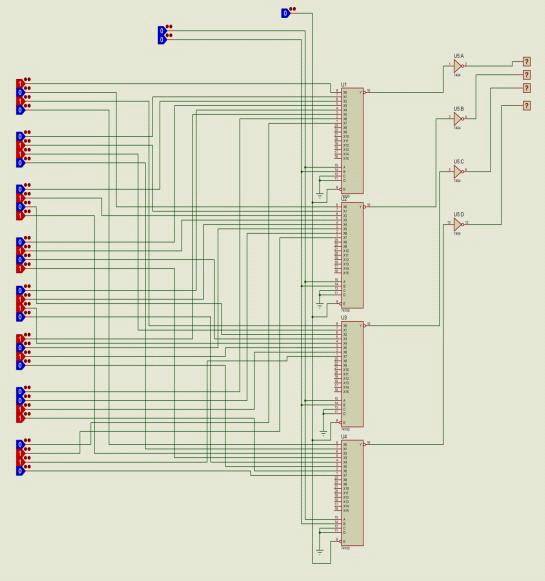

Рисунок 2.1.2 - Структурная схема коммутатора

параллельных кодов

Таблица 2.1.3 - Перечень элементов

|

Позиционное обозначение |

Наименование |

Количество |

Примечание |

|

U1-U4 |

ИМС К155КП1 |

4 |

Мультиплексор |

2.2 Расчет потребляемой

мощности и времени задержки

По структурно-логической схеме

мультиплексора К155КП1 определяем число логических элементов, входящих в состав

стандартного мультиплексора, - N=25.

Средняя потребляемая мощность одним элементом Pпот.ср

=

22 мВт. Энергопотребление одного мультиплексора равно:

![]()

В схеме используется М=5

стандартных мультиплексоров К155КП1. Общее энергопотребление всего устройства

равно:

![]()

Расчет времени задержки осуществляется для передачи одного слова со входа коммутатора на выход для одной ИМС мультиплексора, так как все ИМС работают во времени одновременно (параллельно). Считается, что входные слова и стробирующие сигналы поданы на устройства заранее, а искомая задержка определяется относительно момента подачи адресных сигналов.

Средняя величина временной

задержки элемента равна:

![]()

По структурно-логической схеме К155КП1 определяем количество логических элементов, участвующих в прохождении сигнала, - К1 =4.

Задержка передачи сигнала

стандартным мультиплексором равна:

![]()

3.

Устройство параллельного ввода слов в

регистры

.1 Описание регистра

и структурная схема устройства

Устройство параллельного ввода в регистр состоит из информационной части (регистры) и управляющей (счетчик, дешифратор). Счетчик считает слова и отправляет номер этого слова в дешифратор, который по этой комбинации выбирает регистр для записи слова.

По заданию необходимо записать шесть слов, каждое из которых состоит из семи разрядов, с частотой 900 кГц.

Для записи всех слов необходимо использовать 5

регистров, способных принять не менее 12 разрядов. Для записи слов выберем

регистры марки 74198

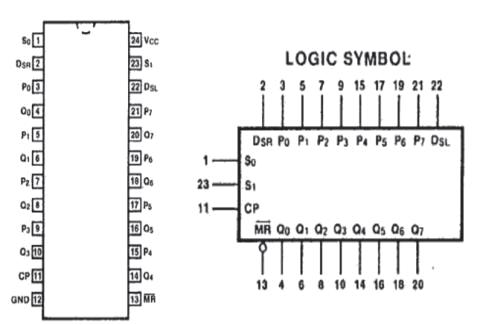

Рисунок 3.1 - Микросхема 74198

P0, P1, … ,P7; − параллельные информационные входы;

Q0, Q1, … ,Q7; − выходы триггеров регистра;

DSR − последовательный информационный вход (сдвиг разрядов вправо);

DSL − последовательный информационный вход (сдвиг разрядов влево);

S0, S1 − входы выбора режима загрузки данных;

CP − вход для подачи тактовых импульсов;

![]() − Master

reset (очистка регистра).

− Master

reset (очистка регистра).

Напряжение питания микросхемы составляет GHH =

+5В. Регистр имеет 8 D-триггеров, выполненных по схеме ТТЛ. Вход CP

−

динамический (управление происходит по положительному фронту). При загрузке

данных через DSL

смещение разрядов происходит справа налево, т.е. самый младший разряд

загружаемого слова будет на выходе Q0,

а самый старший - на выходе Q7.

При загрузке через вход DSR

−

наоборот. Записать данные в триггеры можно одновременно через входы P0,

P1,

… ,P7.

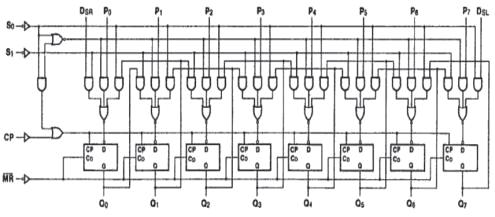

Рисунок 3.2 - Структура микросхемы 74198

При подаче на ![]() лог.0

происходит очистка регистра, т.е. на все выхода будет лог.0 (таблица 3.1).

Когда S0

= 0 и S1

= 0 регистр хранит записанную информацию.

лог.0

происходит очистка регистра, т.е. на все выхода будет лог.0 (таблица 3.1).

Когда S0

= 0 и S1

= 0 регистр хранит записанную информацию.

Таблица 3.1.1 - Выбор режима загрузки данных

|

Входы |

Функция |

|||||||

|

MR |

CLK |

S0 |

S1 |

|

||||

|

0 |

X |

X |

X |

Асинхронный сброс |

||||

|

1 |

|

1 |

1 |

Параллельная нагрузка |

|

0 |

1 |

Сдвиг вправо |

|

1 |

|

1 |

0 |

Сдвиг влево |

||||

|

1 |

X |

0 |

0 |

Хранение данных |

||||

При S0 = 1 и S1 = 1, а также по фронту на CP, в регистр загружаются данные с входов P0, P1, … ,P7. Когда S0 = 0, а S1 = 1 будет происходить запись с последовательного входа DSR. По первому положительному фронту на CP происходит сдвиг, и состояние на входе DSR передастся в триггер с выходом Q0. По второму фронту состояние этого триггера передастся триггеру с выходом Q1, а вQ0 запишется новое состояние входа DSR и т.д. Аналогично вводятся данные с входа DSL при S0 = 1, а S1 = 0, только в этом случае сдвиг будет происходить в обратную сторону.

В качестве счетчика выбираем микросхему 7490,

обладающую четырехразрядным выходом. Входы синхронного сброса RI и R2

(двухвходовой элемент И) запрещают действие импульсов по обоим тактовым входам

и входам установки S. Импульс, поданный на вход R, дает сброс данных по всем

триггерам одновременно.

Таблица 3.1.2 - Режим работы счётчика 7490

|

Счет |

Выход |

|||

|

|

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

|

10 |

1 |

0 |

1 |

0 |

|

11 |

1 |

0 |

1 |

1 |

|

12 |

1 |

1 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

|

14 |

1 |

1 |

1 |

0 |

|

15 |

1 |

1 |

1 |

1 |