Материал: Процесс проектирования блока обработки данных в структурном базисе серии К1804ВС2

При отсутствии подачи электроэнергии к памяти этого типа происходит разряд конденсаторов, и память опустошается (обнуляется). Для поддержания необходимого напряжения на обкладках конденсаторов ячеек и сохранения их содержимого, их необходимо периодически подзаряжать, прилагая к ним напряжения через коммутирующие транзисторные ключи. Такое динамическое поддержание заряда конденсатора является основополагающим принципом работы памяти типа DRAM и называется регенерацией памяти.

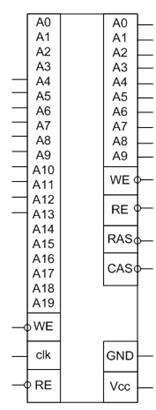

В рамках курсового проектирования использовались

микросхемы KM44C1000D производства компании Samsung Electronics (организация 1M

х 4бит). Таким образом, использование этих микросхем позволило обойтись всего 8

корпусами для достижения необходимой конфигурации памяти. Для работы

построенной памяти был выбран контроллер Renesas H8S/2377R.

Рисунок 5.1 - Условное обозначение микросхемы

памяти

Таблица 5.1 - Описание выводов микросхемы ОП

|

Обозначение |

Описание |

|

A0 - A9 |

Адресные входы |

|

DQ0 - 3 |

Вход/выход данных |

|

Vss |

Земля |

|

-RAS |

Строб адреса строки |

|

- CAS |

Строб адреса столбца |

|

-W |

Разрешение записи |

|

-OE |

Разрешение чтения |

|

Vcc |

Питание (+5) |

Рисунок 5.2 - Структурная схема микросхемы

памяти КМ44С100D.

5.2 Работа динамического ОЗУ

Адрес в микросхему вводится через контроллер, который автоматически генерирует необходимые сигналы для выбора необходимой строки и столбца. По линиям адреса вводится адрес и фиксируются. Внутри микросхемы имеются регистры-защелки для хранения адреса строки и столбца, а также регистр-защелка для фиксации данных.

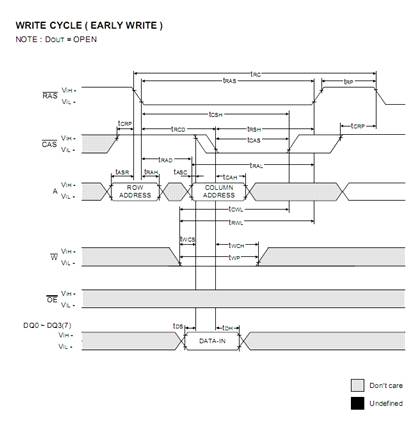

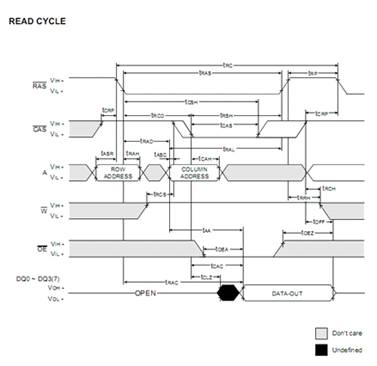

Цикл обращения к памяти начинается по сигналу ¬RAS, при этом стробируется адрес строки, дешифрируется и выбирается одна из строк матрицы в регистр-защелку строки (информация в выбранной строке разрушается).

По сигналу ¬CAS адрес из линий адреса стробируется в регистр-защелку адреса столбца, который после дешифрации выбирает соответствующий элемент из регистра строки. При пассивном ¬WE (чтение) выбранный разряд появляется на входе DQ, при активном ¬WE (запись) входной сигнал DQ заменяет выбранный разряд. Цикл обращения к ОЗУ заканчивается, когда ¬RAS становится пассивным, после чего происходит перезаряд выбранной строки - копирование данных из регистра строки в соответствующую строку матрицы.

Поскольку обращения (запись или чтение) к различным ячейкам памяти обычно происходят в случайном порядке, то для поддержания сохранности данных применяется регенерация (Memory Refresh - "освежение" памяти) - регулярный циклический перебор ее ячеек (обращение к ним) с холостыми циклами. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. Максимальный период обращения к каждой строке (refresh time) для гарантированного сохранения информации у современной памяти лежит в пределах 16 мс.

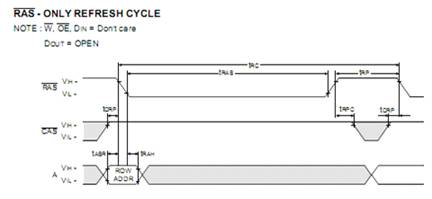

Циклы регенерации могут организовываться разными

способами. Для регенерации спроектированной памяти была использована

регенерация без импульса ¬CAS, сокращенно именуемый ROR (RAS Only Refresh -

регенерация только импульсом ¬RAS). В этом цикле для регенерации информации в

одной строке адрес очередной регенерируемой строки выставляется контроллером

памяти и подается сигнал ¬RAS при пассивных ¬CAS и ¬WE. По этому сигналу строка

матрицы копируется в регистр-защелку строки, а по спаду ¬RAS строка

восстанавливается. Порядок перебора регенерируемых строк последовательный.

Рисунок 5.3 - Временная диаграмма режима записи

Рисунок 5.4 - Временная диаграмма режима чтения

Рисунок 5.5 - Временная диаграмма режима регенерации

5.3 Контроллер ОП

Контроллер динамической памяти предназначен для полного управления работой памяти. Как описано выше, адрес памяти условно разбит на две части: адрес строк и адрес столбцов. Адреса передаются поочередно вместе со стробирующими сигналами подачи адреса. Так же контроллер условно “открывает” и “закрывает” двунаправленную шину данных. Внутри контролера находятся три основные цепи - это чтения, записи и регенерации. Цепи чтения и записи устанавливают необходимые сигналы активности входа/выхода микросхем памяти, а так же подают в необходимом порядке адрес и стробирующие сигналы. Цепь регенерации блокирует подачу сигнала строба по столбцам, а в это время активирует строб перебора по строкам и передает управление адресом на счетчик. Счетчик, который находится в цепи регенерации, необходим для перебора двоичных адресов по строкам памяти. По этим адресам из счетчика будет проводиться регенерация соответствующих строчек. Основа логики контроллера лежит на сигналах с шины. Наиболее важны сигналы индикации записи/чтения, строба адреса и синхронизации.

В рамках курсового проекта был выбран контроллер

марки Renesas H8S/2377R, который выполняет все описанные выше действия.

Рисунок 5.6 - Условное графическое изображение

контроллера

Таблица 5.2 - Назначение выводов контроллера

|

Название вывода |

Описание |

|

|

A0-A19 |

Адрес |

|

|

WE |

Сигнал разрешения записи |

|

|

RE |

Сигнал разрешения чтения |

|

|

clk |

Вход тактового сигнала |

|

|

RAS |

Сигналы выбора строки |

|

|

CAS |

Сигналы выбора столбца |

|

|

Vcc |

Напряжение питания |

Земля |

6. Интерфейс шины процессор -

память: ISA

Связь между процессором и модулем динамического ОЗУ необходимо выполнить с помощью стандартного интерфейса. Для адресации заданного объема оперативной памяти 4 МБ при четырехбайтовом слове наиболее подходящей оказалась системная магистраль ISA. Она имеет 20 разрядов адреса и 16 разрядов данных. Системная магистраль предназначена для обмена данными между центральным процессором и оперативной памятью.

Так как разрядность канала данных шины равна 16 разрядам, а длина слова ОП равна 32 разряда, то существует необходимость передачи данных через шину за два цикла. Это реализуется с помощью временного хранения половины слова ОП в регистре и последующей его передачи, по завершении передачи первой половины.

Подобным же образом организован и прием данных

для записи в ОП. Сначала передается первая часть слова, которая записывается в

регистр для временного хранения, затем передается вторая часть слова, после

чего уже происходит запись данных.

Таблица 6.1 - Описание сигналов шины

|

Обозначение |

Описание |

|

SA<19..0> |

Адресные сигналы шины |

|

BALE |

Сигнал разрешения на «защелкивание» адреса на шине |

|

AEN |

Разрешение адреса |

|

SD<15..0> |

Шина данных |

|

-MEMR |

Сигнал разрешения чтения памяти |

|

-MEMW |

Сигнал разрешения записи в память |

|

-REFRESH |

Сигнал информирования о том, что совершается регенерация памяти |

|

-MASTER |

Сигнал захвата устройством шины |

|

SYSCLK |

Сигнал тактовой частоты |

|

IRQ<15..0> |

Сигналы запроса прерывания |

|

-0WS |

0 тактов ожидания |

Заключение

В ходе курсового проектирования был сформирован блок обработки дынных в заданном архитектурном базисе, а также - приведены чертежи его основных блоков. При проектировании были использованы различные подходы построения цифровых устройств, в случаях, когда микросхему невозможно было подобрать, применялись эквивалентные схемы, собранные на других микросхемах.

Таким образом по завершении курсового проектирования был разработан блок обработки данных в заданном структурном базисе с небольшими отступами от него, где это было необходимо. По завершении были представлены чертежи и документация, описывающая проделанную работу.

Список использованных источников

шина данная автомат интерфейс

1. Аверьянов Н. Н., Березенко А.И., Борщенко Ю.И. и др.; Под ред. Шахнова В.А. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2 т. - М.: Радио и связь, 1988. - 368 с.: ил. ISBN 5-256-00371-2

. Райхлин В.А. Основы цифровой схемотехники.: Учебное пособие для вузов. Казань: Изд-во Казан. гос. тех. ун-та, 2000. - 352 с. ISBN 5-7579-0311-2

. Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник. - М.: Машиностроение, 1993. - 256 с.: ил. ISBN 5-217-02604-9

. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т. 5. - М.: КубК-а, 1997. 608 с.: ил. ISBN 5-85554-158-4

. Интерфейсы систем обработки данных: Справочник/А.А. Мячев, В.ЯН. Степанов, В.К. Щербо; Под ред. А.А. Мячева.- М.: Радио и связь, 1989.- 416 с.

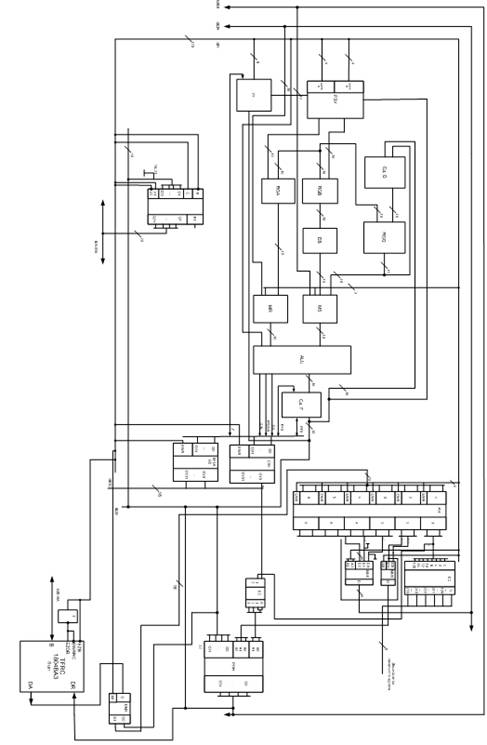

Приложение A

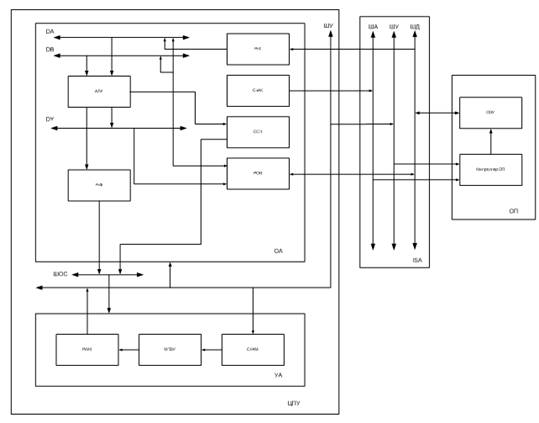

Рисунок A1 - структурная схема БОД

Приложение Б

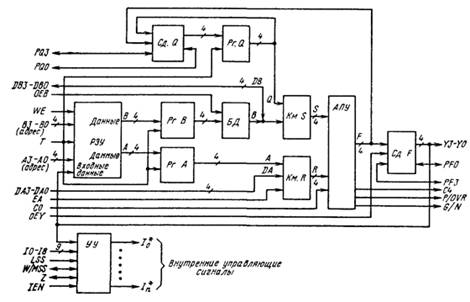

Описание схемы К1804ВС2

Рисунок Б1 - Схема электрическая структурная МПС

К1804ВС2

Таблица Б1 - Основные электрические параметры МПС

Таблица Б2 - назначение выводов К1804ВС2

Рисунок Б2 - функциональная схема ОА

Приложение В

Описание схемы К1804ВР1

Талица В1 - назначение выводов К1804ВР1

Таблица В2 - основные электрические параметры

Приложение Г

Описание схемы К1804ИР2

Таблица Г1 - назначение выводов К1804ИР2

Таблица Г2 - основные электрические параметры К1804ИР2

Приложение Д

Описание схемы К155КП7

Таблица Д1 - обозначение выводов К155КП7

Приложение Е

Таблица Е1 - обозначение выводов К155ИД3

Приложение Ж

Описание схемы К1804ВУ4

Таблица Ж1 - назначение выводов К1804ВУ4

Рисунок Ж1 - общая структура УА

Описание схемы К1804ВУ4

Таблица Ж2 - основные электрические характеристики схемы

Приложение З

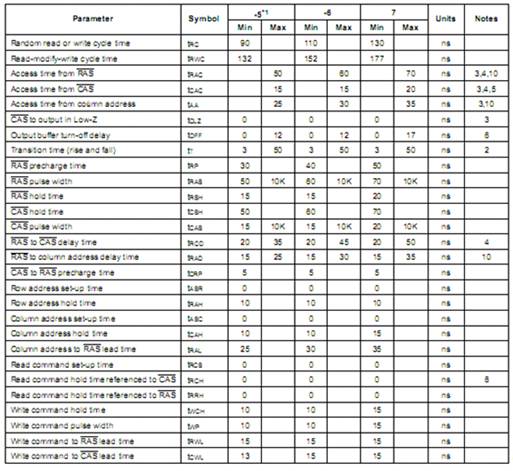

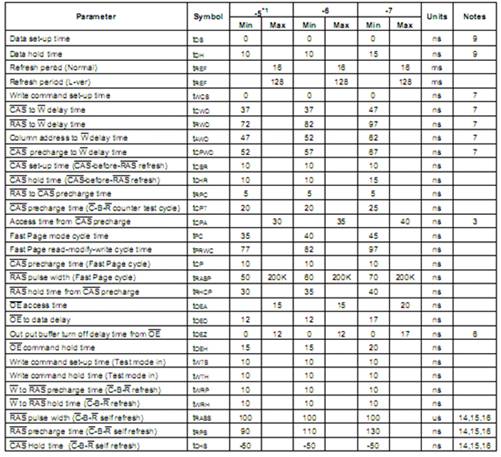

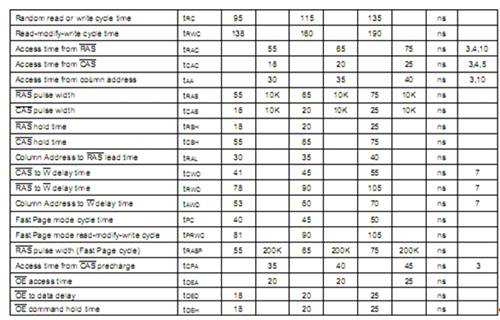

Таблица З1 - Динамические характеристики KM44C1000D