248 • I/O modules

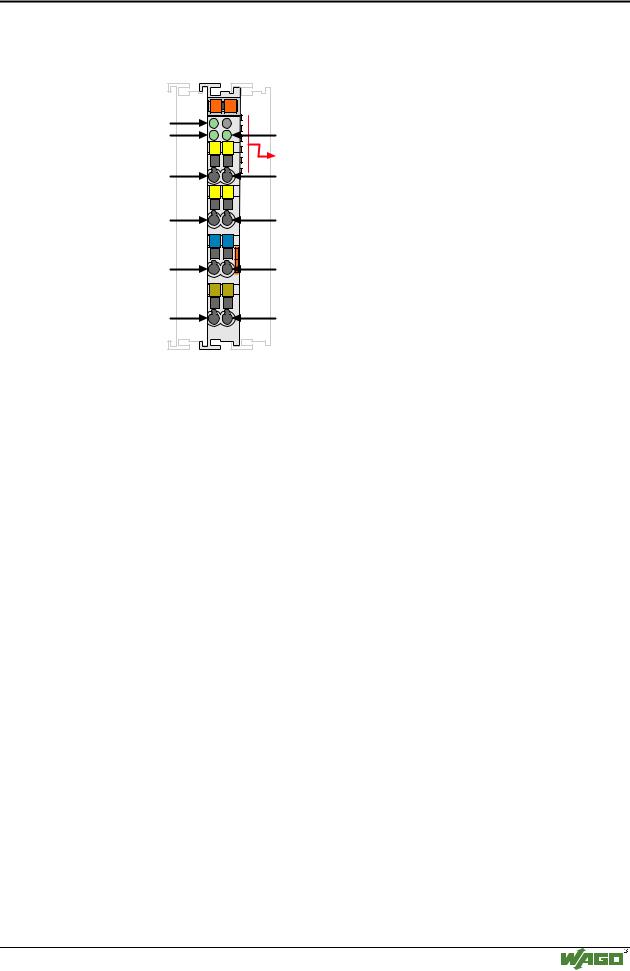

TTY interface 750-651

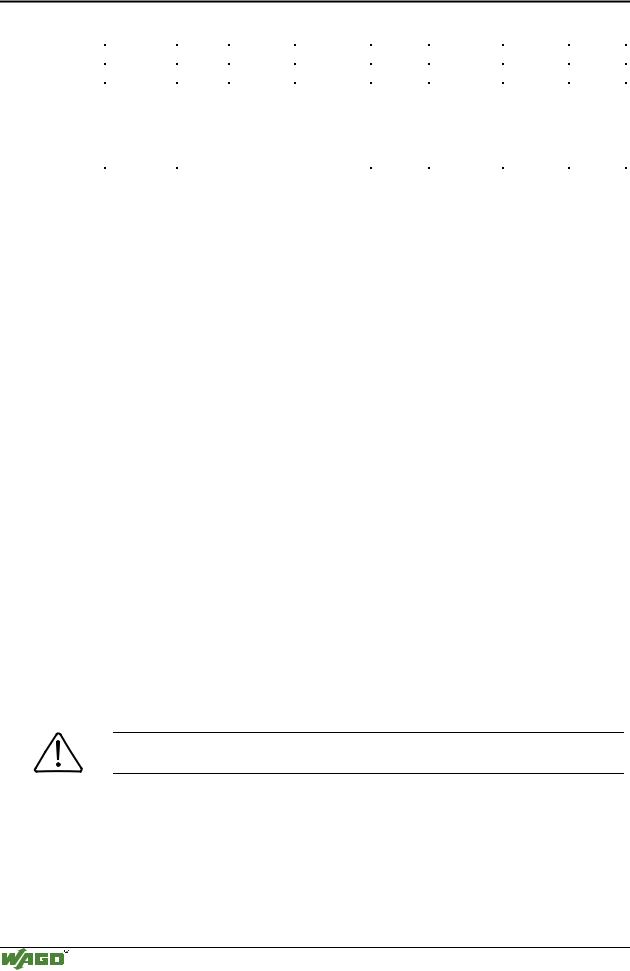

The status byte consists of the following bits:

Bit 7 |

Bit 6 |

Bit 5 |

|

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

0 |

IL2 |

IL1 |

|

Il0 |

BUF_F |

IA |

RR |

TA |

Constant |

rames available in input area IL2 is |

Input |

Initialization |

Receive |

Transmit |

value should |

|

always 0. |

|

buffer is |

acknow- |

request |

acknow- |

always be 0. |

i.e. IL2, IL1, IL0 = 0,1,0 |

full. |

ledge |

|

ledge |

|

2 characters were received and |

|

|

|

|

|

reside in input 0 and input 1. |

|

|

|

|

The PLC is able to control transmission and reception of data by means of the control byte and the status byte.

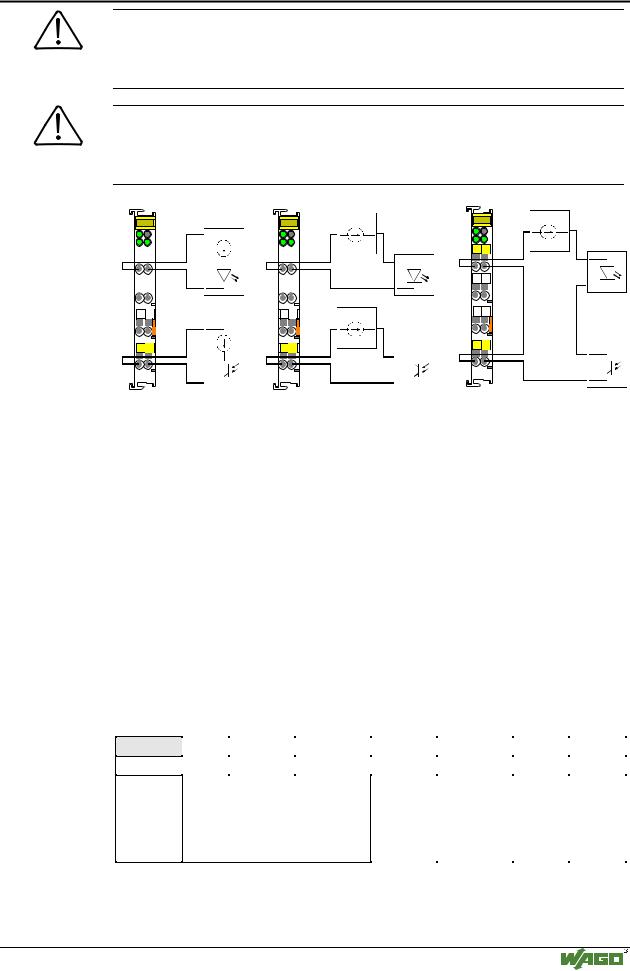

Initialization of the module:

•set IR bit in the control byte to "1"

•transmit/receive functions are blocked

•output/input buffers are erased

•serial interface module will load its configuration data

Transmitting data:

•TR≠ TA: put characters into output bytes 0 to 2

•amount of characters is specified in OL0 to OL2

•TR is inverted and read out

•characters are put into output buffer if TR=TA

Receiving data:

•RR≠ RA: input bytes 0 to 2 characters are available

•amount of characters is specified in IL0 to IL2

•characters in IL0 to IL2 are read out

•RA is inverted and read out

•all characters are read when RR=RA

The transmitting and receiving of data can be done simultaneously. The initialization request has prioirity and will stop the transmitting and receiving of data immediately.

Attention

Resetting the initialization bit can be performed with the following message.

Message: input buffer full (Bit 3)

Input buffer is full. Data which is being currently received is now lost.