Материал: Захаров, Сайфутдинов - Вычислительная техника

|

|

1 |

|

|

|

|

|

Q1 o |

1 |

|

|

|

|

Q2 o |

1 |

|

|

|

|

Q3 o |

|||||||||

|

|

|

|

J |

T1 |

|

|

|

|

|

|

J |

T2 |

|

|

|

|

|

|

J |

T3 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

K |

o |

|

|

|

|

|

K |

o |

|

|

|

|

|

K |

o |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

C |

|

|

|

|

|

C |

|

|

|

|

|

C |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

||||||||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

||

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

б |

||||||||||

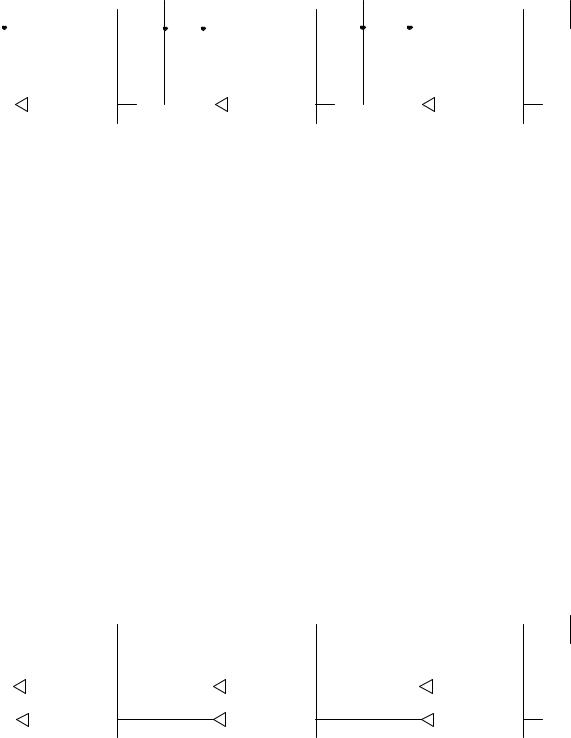

Рис. 4.20. Схема суммирующего двоичного счетчика (а) и временная диаграмма его работы (б)

|

|

1 |

|

|

|

|

|

Q1 |

1 |

|

|

|

|

Q2 |

1 |

|

|

|

|

Q3 o |

||||

|

|

|

|

J |

T1 |

|

|

J |

T2 |

|

|

J |

T3 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

K |

|

|

|

|

|

|

K |

|

|

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

C |

o |

|

|

C |

o |

|

|

C |

o |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

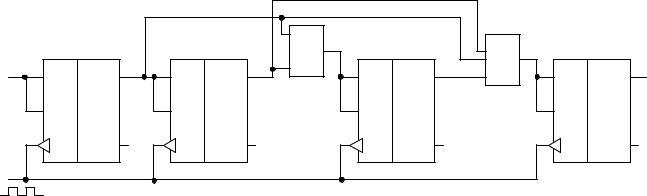

Рис. 4.21. Схема вычитающего двоичного счетчика

96

4.12.1. Параллельные счетчики

На рис. 4.20, а и 4.21 показаны схемы двоичных последовательных счетчиков, т. е. таких счетчиков, в которых при изменении состояния определенного триггера возбуждается последующий триггер, причем триггеры меняют свои состояния не одновременно, а последовательно. Если в данной ситуации должны изменить свои состояния n триггеров, то для завершения этого процесса потребуется n интервалов времени, соответствующих времени изменения состояния каждого из триггеров. Такой последовательный характер работы является причиной двух недостатков последовательного счетчика: меньшая скорость счета по сравнению с параллельными счетчиками и возможность появления ложных сигналов на выходе схемы. В параллельных счетчиках синхронизирующие сигналы поступают на все триггеры одновременно.

Последовательный характер переходов триггеров счетчика является источником ложных сигналов на его выходах. Например, в счетчике, ведущем счет в четырехразрядном двоичном коде с «весами» 8421, при переходе от числа 710 = 01112 к числу 810 = 10002 на выходе появится следующая последовательность сигналов:

0111 0110 0100 0000 1000.

Это означает, что при переходе из состояния 7 в состояние 8 на входах счетчика на короткое время появятся состояния 6; 4; 0. Эти дополнительные состояния могут вызвать ложную работу других устройств.

С целью уменьшения времени протекания переходных процессов, схему, приведенную на рис. 4.20, а, можно реализовать в варианте с подачей входных импульсов одновременно на все триггеры. В этом случае получим параллельный суммирующий счетчик (рис. 4.22).

Здесь на информационные входы триггеров подаются сигналы, являющиеся логической функцией состояния счетчика и определяющие конкретные триггеры, которые изменяют свое состояние при данном входном импульсе. Принцип стробирования сводится к следующему: триггер меняет свое состояние при поступлении очередного импульса синхронизации, если все предыдущие триггеры находились в состоянии логической единицы.

97

|

|

Q0 |

|

Q1 |

& |

Q2 |

& |

Q3 |

1 |

|

|

|

|||||

|

|

|

|

|||||

|

J |

T0 |

J |

T1 |

J |

T2 |

J |

T3 |

|

K |

|

K |

|

K |

|

K |

|

|

C |

o |

C |

o |

C |

o |

C |

o |

C

Рис. 4.22. Схема параллельного суммирующего счетчика

Параллельные счетчики имеют более высокое быстродействие по сравнению с последовательными, поскольку синхронизирующие импульсы поступают на все триггеры одновременно.

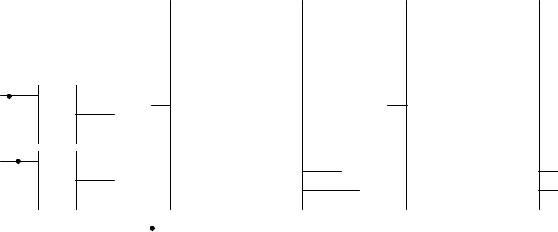

4.12.2. Реверсивные счетчики

Реверсивные счетчики позволяют суммировать или вычитать входные импульсы в зависимости от значений сигналов управления. Он реализуется путем объединения схем управления входами суммирующего и вычитающего счетчиков.

Реверсивные счетчики выпускаются в виде отдельных ИМС. Например, ИМС типа 155 ИЕ7 представляет собой реверсивный четырехразрядный двоичный счетчик. На рис. 4.23 представлена схема реверсивного восьмиразрядного двоичного счетчика, построенного на двух ИМС типа 155 ИЕ7. Разряд Q8 является знаковым. Счет ведется в дополнительных кодах.

Каждая ИМС имеет по два счетных входа C1 и C2, обеспечивающих соответственно работу в режиме суммирования и вычитания. Изменения состояния счетчика происходит в момент поступления переднего фронта импульса на вход C1 или C2. Если счетчик работает в режиме суммирования, то изменяется сигнал на входе C1. Сигнал на входе C2 должен иметь при этом высокий логический уровень. При работе в режиме вычитания изменяется сигнал на входе C2, а вход C1 находится в состоянии логической единицы.

98

|

|

|

|

|

|

|

|

|

|

|

D1 |

CT |

1 |

|

|

|

Q |

1 |

|

|

|

D1 |

CT |

1 |

|

|

Q |

5 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

2 |

|

|

|

Q |

|

|

|

D2 |

|

2 |

|

|

Q |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

6 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

D3 |

|

3 |

|

|

|

Q |

|

|

|

D3 |

|

3 |

|

|

Q |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

7 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

D4 |

|

4 |

|

|

|

Q |

|

|

|

D4 |

|

4 |

|

|

Q |

||||

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

8 |

|||||||||

|

|

o & |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

«1» |

|

|

|

|

|

|

|

|

|

«1» |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

o |

o V |

|

|

|

|

|

|

o V |

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

C1 |

|

|

|

|

|

|

|

|

|

|

|

C1 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

C |

|

|

|

|

|

|

|

|

|

|

C2 |

|

|

|

|

|

|

|

|

|

|

|

C2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

o & |

o |

|

|

|

|

P |

o |

|

|

|

|

|

P o |

P |

+ |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

R |

|

W o |

|

|

|

|

|

R |

|

W o |

P |

||||||||||

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

_ |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.23. Схема реверсивного восьмиразрядного счетчика на микросхемах 155ИЕ7

ИМС 155ИЕ7 имеет два выхода переполнения: выход Р (переноса при суммировании) и выход W (заема при вычитании). Сигналы Р и W формируются аналогичным образом. На выходе переноса Р отрицательный спад импульса образуется при переполнении счетчика, т. е. при появлении па выходах Q1 – Q4 максимального числа и условии, что тактирующий сигнал на входе С имеет нулевое состояние. На выходе заема W импульс формируется при появлении на выходах всех разрядов Q1 – Q4 счетчика нулевого логического уровня, при этом вход С2 должен находиться в состоянии логического нуля. Микросхема имеет входы D1 – D4, по которым возможна параллельная запись четырехразрядных кодов при условии, что на входы V и R поданы сигналы нулевого логического уровня.

Контрольные вопросы

1.Какое принципиальное отличие последовательностных устройств от комбинационных?

2.В чем отличие асинхронных и синхронных триггеров?

3.Какие входы может иметь регистр памяти?

4.Какие функции может выполнять регистр сдвига?

5.Какие способы используются для построения счетчиков по модулю не кратному степени два?

6.Какие основные недостатки счетчиков последовательного типа?

99

5. ЦИФРО-АНАЛОГОВЫЕ И АНАЛОГОВО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ

5.1. Цифро-аналоговые преобразователи

Цифро-аналоговые преобразователи (ЦАП) – это преобразователи коднапряжение (ПКН). Задача рассматриваемого преобразователя состоит в выработке напряжения U на выходе ПКН, пропорционального входному двоичному числу N. Используя известную форму представления двоичных чисел

n 1

N = a020 + a121 + …+ an-12n-1 = ai 2i ,

i 0

запишем операцию, выполняемую ПКН, в виде

|

U |

max |

n 1 |

2i |

|

|

U(N) = |

|

N Umax |

|

ai |

||

Nmax |

2n 1 |

|||||

|

i 0 |

|

||||

n 1 |

|

Uiai , |

(5.1) |

i 0

где отношение максимального выходного напряжения Umax к максимальному входному числу Nmax = 2n – l играет роль масштабного коэффициента, определяемого как напряжение, соответствующее единице входного числа, т. е. U(1) = Umax /Nmax.

Из выражения (5.1) следует, что операция преобразования код-напряжение

сводится к суммированию элементарных напряжений: |

|

Ui = Umax2i /2n – 1 Umax/2n-i = UmaxKi , |

(5.2) |

которые образуются путем деления некоторого эталонного напряжения Umax с помощью резистивных делителей с коэффициентом передачи Кi = 1/2n-i. При этом из операции суммирования исключаются те слагаемые Ui, которые соответствуют нулевым значениям элементов аi, составляющих входное двоичное число (аn-1 аn-2 ... а1 а0).

Для реализации этого принципа преобразования на практике используются две разновидности схем, представленные на рис. 5.1 а, б. Первую схему (рис. 5.1, а) называют ПКН с двоично взвешенными резистивными цепями (или схемой с суммированием напряжений), а вторую (рис. 5.1, б) ПКН с многозвенной резистивной цепью типа R-2R. В обеих схемах при появлении единицы в i-м разряде двоичного числа эталонное напряжение Umаx проходит через соответствующий замкнутый ключ и резистивную цепь на выход. Различие этих схем в том, как формируется требуемый коэффициент деления эталонного напряжения с помощью резистивной матрицы.

100

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |