Материал: Разработка однокристального RISC-процессора для встроенных применений

Рис. 13

процессор кристалл число регистровый

В двух из трех разрядов, следующих за кодом операции, содержатся признак разрядности операнда (8/16-разрядный) (Р) и бит разрешения/запрета установки флажков (если он равен единице, все команды сдвига помещают значение бита, сдвинутого за границы операнда, во флаг переноса) (Ф).

В зависимости от значения признака разрядности операнда может быть выполнен сдвиг 8- или 16-разрядного содержимого регистра.

В первом случае осуществляется сдвиг только

старшей половины регистра, содержимое младшей половины при этом не определено.

.5 Команды переходов и работы с подпрограммами

Команды безусловного/условных переходов и команда вызова подпрограммы имеют общий формат (рис. 14) и содержат прямой адрес следующей команды или ее смещение относительно текущего значения программного счетчика.

Различие между простым переходом и вызовом

подпрограммы заключается в том, что при переходе к подпрограмме адрес следующей

за вызовом команды помещается в стек для последующего возврата.

![]()

Рис. 14

В одном из трех разрядов, следующих за кодом операции, содержится признак (П), определяющий, как следует использовать значение адресного поля команды. В одном случае адрес перехода вычисляется с помощью сложения адреса текущей команды, который содержится в регистре PC, со значением смещения в соответствующем поле команды. В другом случае в программный счетчик помещается находящийся в адресном поле прямой адрес перехода в памяти команд.

Команда возврата из подпрограммы имеет

безадресный формат (рис. 15) и содержит только код операции. Адрес возврата

извлекается из стека.

![]()

Рис .15

.6 Команда загрузки в регистр непосредственного

значения

Команда загрузки значения в регистр (рис. 16)

содержит в двух младших байтах непосредственный операнд, заносимый в регистр

AРЕГ. Формат полей команды аналогичен командам обращения к памяти при

использовании относительной адресации (см. рис. 10) и командам сдвигов (см.

рис. 13).

![]()

Рис. 16

Непосредственный операнд, заносимый в регистр,

всегда является 16-разрядным словом. Биты признаков в данной команде

игнорируются.

.7 Команды управления

Команды управления микропроцессором имеют

безадресный формат (рис. 17) и содержат только код операции.

![]()

Они включают в себя команды управления флагами

(например, установка и сброс флага разрешения прерываний), команды внешней

синхронизации (например, команда останова), команду холостого хода и др.

7. Система команд

В табл. 2 приведена система команд разрабатываемого процессора (включая семантику их выполнения и установку флажков). Синтаксис большинства команд состоит из мнемонического обозначения операции, вслед за которым идут операнды. Различные типы данных или способы адресации определяются указанными операндами, а не изменениями мнемонических обозначений.

Обозначения, используемые при описании семантики

операций, приведены под таблицей.

Табл. 2

|

N |

Мне- |

Название |

Содержание |

Флажок |

Код |

||

|

|

моника |

|

|

C |

Z |

S |

|

|

Команды обращения к памяти |

|||||||

|

1 |

LOAD |

Чтение из внешней памяти данных |

(Rn) := (AПАМ) или (Rn) := ((BPi)) или (Rn) := ((BPi) + смещ) |

- |

- |

- |

00000001 |

|

2 |

STORE |

Запись во внешнюю память данных |

(AПАМ) := (Rn) или ((BPi)) := (Rn) или ((BPi) + смещ) := (Rn) |

- |

- |

- |

00000010 |

|

Команды обращения к стеку |

|||||||

|

3 |

PUSH |

Запись в стек |

(SP) := (SP) - 1 ((SP)) := (Rn) |

- |

- |

- |

00000011 |

|

4 |

POP |

Чтение из стека |

(Rn) := ((SP)) (SP) := (SP) + 1 |

- |

- |

- |

00000100 |

|

Арифметические и логические команды |

|||||||

|

5 |

ADD |

Сложение |

(Rn) := (Ri) + (Rj) или (Rn)[15-8] := (Ri)[15-8] + (Rj)[15-8] |

+ |

+ |

+ |

00000101 |

|

6 |

SUB |

Вычитание |

(Rn) := (Ri) - (Rj) или (Rn)[15-8] := (Ri)[15-8] - (Rj)[15-8] |

+ |

+ |

+ |

00000110 |

|

7 |

MUL |

Умножение |

(Rn) := ((Ri) * (Rj))[15-0] (R0) := ((Ri) * (Rj))[31-16] или (Rn)[15-8] := ((Ri)[15-8] * (Rj)[15-8])[7-0] (R0)[15-8] := ((Ri)[15-8] * (Rj)[15-8])[15-8] |

+ |

+ |

00000111 |

|

|

8 |

DIV |

Деление |

(Rn) := (Ri) / (Rj) или (Rn)[15-8] := (Ri)[15-8] / (Rj)[15-8] |

+ |

+ |

+ |

00001000 |

|

9 |

AND |

Поразрядное "И" |

(Rn) := (Ri) AND (Rj) |

- |

+ |

- |

00001001 |

|

10 |

OR |

Поразрядное "ИЛИ" |

(Rn) := (Ri) OR (Rj) |

- |

+ |

- |

00001010 |

|

11 |

XOR |

Поразрядное "ИСКЛЮЧАЮЩЕЕ ИЛИ" |

(Rn) := (Ri) XOR (Rj) |

- |

+ |

- |

00001011 |

|

Команды сдвигов |

|||||||

|

12 |

SL |

Сдвиг влево |

(Rn)[N+1] := (Rn)[N] (Rn)[0] := 0 или (Rn)[8] := 0 |

+ |

- |

- |

00001100 |

|

13 |

SAR |

Сдвиг вправо арифметический |

(Rn)[N] := (Rn)[N+1] (Rn)[15] := (Rn)[15] |

+ |

- |

- |

00001101 |

|

14 |

SLR |

Сдвиг вправо логический |

(Rn)[N] := (Rn)[N+1] (Rn)[15] := 0 |

+ |

- |

- |

00001110 |

|

15 |

RL |

Сдвиг влево циклический |

(Rn)[N+1] := (Rn)[N] (Rn)[0] := (Rn)[15] или (Rn)[8] := (Rn)[15] |

+ |

- |

- |

00001111 |

|

16 |

RR |

(Rn)[N] := (Rn)[N+1] (Rn)[15] := (Rn)[0] или (Rn)[15] := (Rn)[8] |

+ |

- |

- |

00010001 |

|

|

Команды переходов и работы с подпрограммами |

|||||||

|

17 |

JMP |

Переход безусловный |

(PC) := (PC) + смещ или (PC) := (AКОМ) |

- |

- |

- |

00010010 |

|

18 |

JZ |

Переход, если флаг нуля установлен |

если (Z) = 1, то (PC) := (PC) + смещ или (PC) := (AКОМ) |

- |

- |

- |

00010011 |

|

19 |

JC |

Переход, если перенос установлен |

если (С) = 1, то (PC) := (PC) + смещ или (PC) := (AКОМ) |

- |

- |

- |

00010100 |

|

20 |

CALL |

Вызов подпрограммы |

(SP) := (SP) - 1 ((SP)) := (PC) + 1 (PC) := (PC) + смещ или (PC) := (AКОМ) |

- |

- |

- |

00010101 |

|

21 |

RET |

Возврат из подпрограммы |

(PC) := ((SP)) (SP) := (SP) + 1 |

- |

- |

- |

00010110 |

|

Команда загрузки в регистр непосредственного значения |

|||||||

|

22 |

CNST |

Загрузка в регистр константы |

(Rn) := значение |

- |

- |

- |

00010111 |

|

Команды управления |

|||||||

|

23 |

CLI |

Сброс флага прерываний |

(I) := 0 |

- |

- |

- |

00011000 |

|

24 |

STI |

Установка флага прерываний |

(I) := 1 |

- |

- |

00011001 |

|

|

25 |

HLT |

Останов |

|

- |

- |

- |

00011010 |

|

26 |

NOP |

Нет операции |

(PC) := (PC) + 1 |

- |

- |

- |

00000000 |

При описании операций в таблице используются следующие обозначения:, Rj, Rn - регистры общего назначения;- адресные регистры;ПАМ - прямо адресуемая ячейка памяти данных;КОМ - прямо адресуемая ячейка памяти команд;

смещ, значение - непосредственные данные, входящие в команду;

(X) - содержимое X;

((X)) - содержимое по адресу, хранящемуся в X;

(X)[N] - разряд N в X;

(X)[N1-N2] - группа разрядов N1-N2 в X.

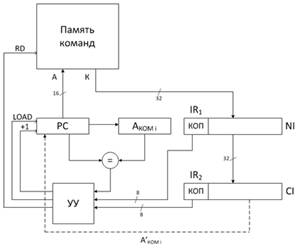

8. Организация конвейера

В процессоре реализован конвейерный принцип

обработки информации. Используется двухступенчатый конвейер по выборке команд

из памяти и по размещению их в очередь для дальнейшего исполнения (рис. 18).

Рис. 18

Для двухступенчатого конвейера выделяются фаза

выборки команды и фаза выполнения команды (рис. 19). Параллельно и асинхронно

могут работать два процессора: процессор памяти и исполнительный процессор.

Процессор памяти обеспечивает работу с памятью команд и памятью данных, а также

с кэш-памятью. На исполнительный процессор возлагаются функции, связанные с

дешифрацией и выполнением команд.

Рис. 19

На рис. 18 содержимое программного счетчика и

адрес следующей подготовленной к выполнению команды (next instruction) подаются

на схему сравнения. Если в результате выполнения текущей команды (current

instruction) в программный счетчик был занесен адрес перехода в программе, то

операция проверки равенства даст отрицательный результат, на основании которого

устройство управления блокирует выполнение следующей команды и заносит

прочитанную из памяти новую команду в регистр. В случае, если адреса равны,

следующая подготовленная команда передается на выполнение, содержимое

программного счетчика увеличивается на единицу, и запускается процесс выборки

очередной команды.

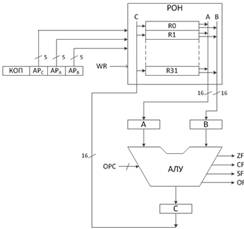

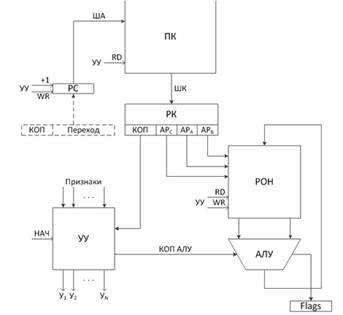

9. Структура исполнительной подсистемы

Структура исполнительной подсистемы показана на

рис. 20. Основными элементами исполнительной подсистемы являются регистровый

файл (РОН) и АЛУ. Трехшинная организация РОН допускает в одном такте выборку

двух операндов и запись одного операнда. Данные при этом выбираются из РОН по

переднему фронту импульса синхронизации и записываются по заднему фронту.

Операционное устройство представляет собой комбинационную схему. Все операции

выполняются за один такт.

Рис. 20

По переднему фронту синхроимпульса из РОН

одновременно выбираются два операнда, соответствующие адресам AРA и AРB. В

течение времени длительности тактового импульса сигналы распространяются через

комбинационные схемы АЛУ. При этом выполняемая операция определяется подаваемым

на вход АЛУ кодом операции (OPC). Если на управляющий вход РОН подается сигнал

разрешения записи WR, то по заднему фронту в РОН по адресу AРC запоминается

результат выполнения операции.

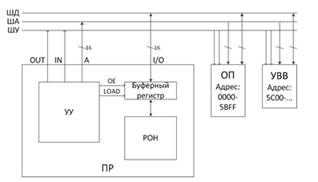

10. Ввод-вывод

Поскольку по требованию технического задания

объем внешней 16-тиразрядной памяти данных должен составлять 46 Кбайт, то, имея

16-тиразрядную шину адреса, часть доступных адресов остается незадействованной.

Таким образом, мы можем разместить в одном адресном пространстве с памятью

данных и другие внешние устройства ввода/вывода, расположив их адреса в

различных диапазонах (рис. 21).

Рис. 21

Для ввода-вывода данных используется

двунаправленный буферный регистр с тремя состояниями. Ввод-вывод организован с

использованием специальных команд ввода-вывода. Идентификация обращения к

внешним устройствам осуществляется по их адресу.

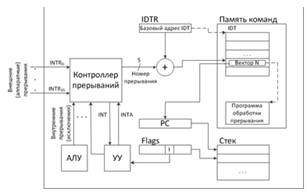

11. Система прерываний

Для автоматической реакции на внешние и на

внутренние события в процессоре реализована векторная система прерываний;

таблица векторов может находиться по произвольным адресам. Используется

внутренний контроллер прерываний (рис. 22).

Рис. 22

В зависимости от источника возникновения сигнала прерывания могут быть:

внешние (аппаратные) - события, которые исходят от внешних источников (периферийных устройств, датчиков и т.п.);

внутренние (исключения) - события в самом процессоре, как результат нарушения каких-то условий при исполнении машинного кода: деление на ноль или переполнение, обращение к недопустимым адресам памяти или недопустимый код операции.

За каждым источником прерывания закрепляется номер - вектор прерывания, который идентифицирует соответствующий обработчик прерывания. Векторы прерываний объединяются в таблицу векторов прерываний (IDT), содержащую адреса обработчиков прерываний. Местоположением таблицы является память команд. Адрес в физической памяти и размер таблицы прерываний определяется регистром IDTR.

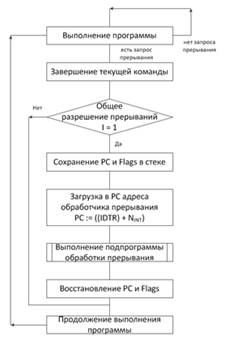

Алгоритм обработки прерывания при обнаружении

запроса прерывания представлен на рис. 23.

Рис. 23

Следует отметить, что при вызове подпрограммы

обработки прерывания аппаратно в стеке сохраняются только программный счетчик и

регистр флагов. Остальные регистры должны сохраняться и восстанавливаться в

прерывающей программе при помощи команд обращения к стеку (PUSH / POP).

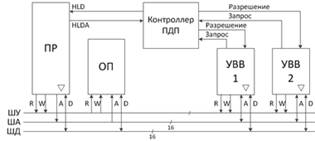

12. Прямой доступ к памяти

В разрабатываемом процессоре предусмотрена

поддержка прямого доступа к памяти, то есть режима обмена данными между

устройствами и основной памятью без участия процессора. В результате скорость

передачи увеличивается, так как данные не пересылаются в процессор и обратно.

Рис. 24

Режим прямого доступа к памяти позволяет любому

устройству заявить о возникновении потребности к захвату шины (см. рис. 24).

При поступлении запроса на захват шины ПДП-контроллер анализирует приоритет

устройства, посылает запрос HLD в процессор и после получения от процессора

сигнала HLDA разрешает устройству захватить шину. Внешнее устройство, успешно

осуществившее захват шины, самостоятельно выставляет на шину сигналы адреса и

управления и исполняет в течение какого-то времени ту же ведущую роль на шине,

что и процессор. На это время процессор отключается от системной шины и

переходит в пассивное состояние.

13. Обобщенный алгоритм функционирования системы

На рис. 25 представлена обобщенная структурная

схема разрабатываемого процессора. На схеме опущены разрядности шин (см. рис.

3, 18, 20). Также с целью упрощения схемы отсутствует изображение конвейерной

обработки команд (см. рис. 18).

Рис. 25

Для выполнения программы процессор выбирает команды из памяти и выполняет определяемые ими действия. Команды выбираются из последовательных адресов памяти, пока не встретится команда перехода. Для этого в программном счетчике (PC) отслеживается адрес очередной подлежащей выполнению команды. После выборки этой команды содержимое регистра PC обновляется, чтобы он указывал на следующую команду в памяти в порядке расположения адресов. Команда перехода может загрузить в PC другой адрес.

На рис. 26 представлен обобщенный алгоритм

функционирования. С целью упрощения алгоритма при описании базового принципа

функционирования не затрагиваются вопросы, связанные с конвейеризацией (см.

раздел "Организация конвейера").

Рис. 26

Как видно из приведенного алгоритма, процессор

завершает цикл выборки и выполнения команд, если очередной выбранной командой

оказывается команда останова (HLT).

14. Алгоритмы выполнения основных команд

.1 Команды обращения к памяти

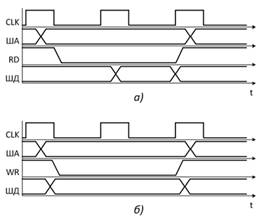

На рис. 27а и 27б соответственно приведены

временные диаграммы циклов чтения и записи при работе процессора с внешней

памятью данных.

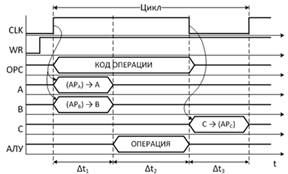

.2 Арифметические и логические команды

Алгоритм функционирования исполнительной подсистемы (см. рис. 20) предполагает выделение следующих фаз выполнения команды:

) выборка команды из кэш-памяти команд;

) выборка данных из регистровой памяти (при этом одновременно дешифрируется код операции);

) выполнение операции в АЛУ;

) запись в РОН результата выполнения операции.

На рис. 28 показано, как происходит

синхронизация этих действий.

Рис. 28

По переднему фронту импульса синхронизации дешифрируется и подается на вход АЛУ код операции. При этом из РОН одновременно выбираются два операнда, соответствующие адресам AРA и AРB, и их значения передаются в регистры A и B соответственно. На это требуется время Δt1. Затем АЛУ начинает оперировать поступившими данными. После промежутка Δt2 сигналы распространятся через комбинационные схемы АЛУ, и выходные сигналы АЛУ стабилизируются. Если на управляющий вход РОН подается сигнал разрешения записи WR, то по заднему фронту в РОН по адресу AРC запоминается результат выполнения операции.

Никаких внешних сигналов, указывающих на начало

и конец подцикла и сообщающих АЛУ, когда нужно начинать работу и когда нужно

передавать результаты на шину C, нет. В действительности АЛУ работает

постоянно. Однако его входные сигналы недействительны в течение периода Δt1.

Точно

так же его выходные сигналы недействительны в течение периода Δt1

+ Δt2. Единственными внешними сигналами,

управляющими исполнительной подсистемой, являются нарастающий фронт

синхронизирующего сигнала, с которого начинается цикл исполнительной

подсистемы, и задний фронт синхронизирующего сигнала, который загружает

регистры из шины C. Границы подциклов определяются только временем прохождения

сигнала.