Материал: Разработка аппаратно-программного комплекса для безопасной передачи сообщения, с использованием алгоритмов шифрования и электронно-цифровой подписи

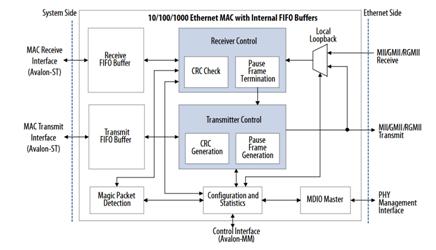

Для этой задачи было взято готовое IP ядро фирмы

AlteraTripleSpeedEthernetMegaCore. Ядро предоставляется без лицензии на

ограниченный промежуток времени. Это значит, что по прошествии часа реального

времени ядро отключается и ПЛИС необходимо перепрограммировать. Ядро

поддерживает стандарт IEEE 802.3 10/100/1000 Мбит в секунду. Структура MAC

уровня ядра показана на рис. 35.

Рис. 35. Структура MAC[27].

Конфигурация ядра MAC

Для того, чтобы ядро заработало корректно, необходимо сконфигурировать его должным образом. Для конфигурации регистров ядра используется шина AvalonMemoryMapped. AvalonMM- простая шинная архитектура, предназначенная для объединения процессоров на кристаллеи внешних устройств этих процессоров в system-on-a-programmable chip (SOPC). Avalon-интерфейс, который определяет подключение порта шины между мастером и подчиненными компонентами, определяет синхронизацию, которой эти компоненты связываются. По адресам 0x00-0x17 находятся базовые регистры, без конфигурации которых, ядро не будет работать корректно. Стоит обратить внимание на адреса 0x03 и 0x04. В них находится MAC-адрес. Это значит, что то значение, которое будет присвоено этим регистрам по заданным адресам, будет являться MAC-адресом ПЛИС. Так же одним из основных регистров является Command_ConfigRegister. Он находится в памяти с адресом 0x02 и, в основном, содержит в себе настройки MAC, такие как: _ENA (Разрешение приема кадров)._GEN (Пауза генерации кадров)._SPEED (Контроль скорости, логическая единица при режиме 1Гбит в секунду)._EN (Разрешение всех пакетов без фильтрации MAC адреса)._FWD (Выбор обсчета контрольной суммы кадров, логический ноль для обсчета КС модулем MAC, логическая единица для обсчета КС пользовательским модулем).

Архитектура стандарта GigabitEthernet

На рис. 36. показана модель OSI и структура

GigabitEthernet. В GigabitEthernet не существует универсального кодирования

сигналов, например 8б/10б кодирование используется в стандартах

1000Base-LX/SX/CX, а для стандарта 1000Base-T используется кодирование TX/T2.

Функция кодирования выполняет подуровень PCS.

Рис. 36. Стандарт GigabitEthernet в модели

OSI[1].

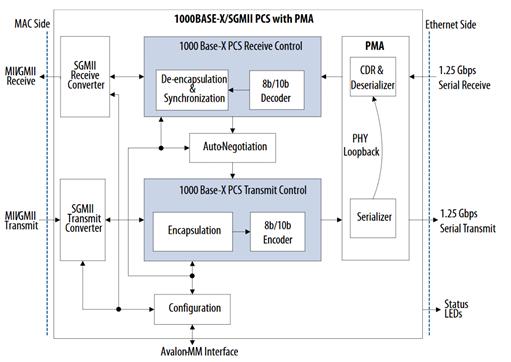

В данной работе используется стандарт 1000Base-X. Для реализации 1000BASE-X необходимо реализовать PCS и PMA. Реализация в ядре MAC показана на рис. 37.

Рис. 37. Реализация PMA и PCS[27].

Проведем анализ рис. 36 и 37, показанные выше. Прием кадра осуществляется по дифференциальной паре с трансивера. Кадр идет последовательно с частотой 1250Мгц. Далее он поступает в десериализатор на PMA модуль. Этот модуль преобразует последовательные данные в параллельные. Далее эти данные уходят в PCS модуль. Здесь происходит 8-10 битное кодирование и синхронизация. Далее эти данные конвертируются в параллельный интерфейс SGMII (по заданным настройкам), выполняется подсчет контрольной суммы и передается в буфер памяти FIFO, откуда по шине AvalonST пользовательский модуль получает кадр. AvalonST - это шина потокового интерфейса, отличие от AvalonMM в том, что в AvalonMM имеется адресация, а в AvalonST данные непрерывно проходят пачками. При передаче информации с пользовательского модуля происходит такой же порядок действий, только наоборот.

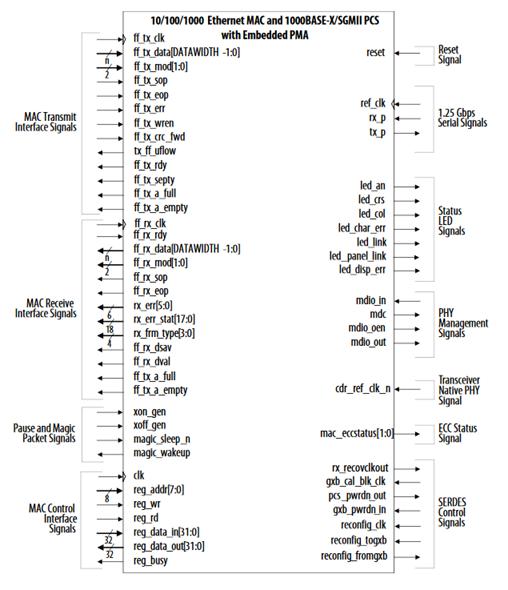

Входные и выходные сигналы модуля MAC показаны на рис. 38.

Рис. 38. Сигналы MAC модуля.

Разработанные модули для ПЛИС

Модуль приемника UART на ПЛИС

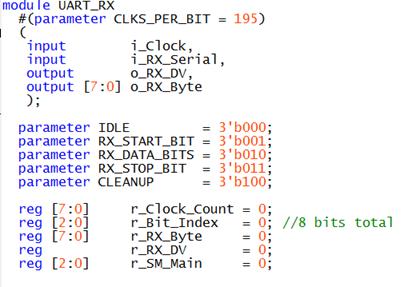

Для приема сообщений с ПК(1) и для дальнейшего формирования ЭЦП был разработан модуль приемника и передатчика UART. Формат стандартен: стартовый бит, 8 бит информационных данных, стоповый бит, без контрольного бита четности. Листинг приемника FT-232 представлен на рис. 39.

Рис. 39. Листинг приемника UART.

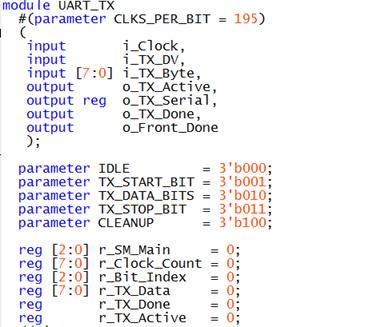

Так как ячейка ММ693 была изготовлена позже модуля формирования ЭЦП, для отладки использовался модуль передатчика UART. Он проще в отладке, чем модуль Ethernet, а по сложности модуль передатчика Ethernet равноценен имплементации алгоритма RSA. Листинг передатчика FT-232 показан на рис. 40.

Рис. 40. Листинг передатчика

Входы и выходы:

CLKS_PER_BIT._Clock.

I_TX_DV - Входной сигнал о начале передачи._TX_Byte - Входной 8-разрядный регистр данных._TX_Active - Выходной сигнал, означающий активность передачи._TX_Serial - Выходной последовательный сигнал UART._TX_Done - Выходной сигнал, означающий полную передачу пакета._Front_Done -Выходной передний фронт сигнала O_TX_DONE.

Модули формирования электронно-цифровой подписи

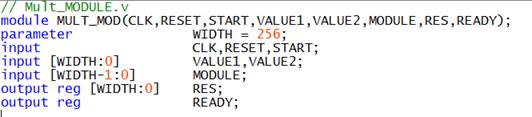

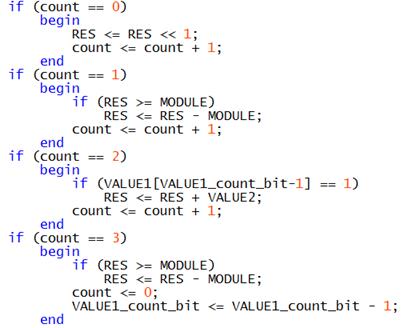

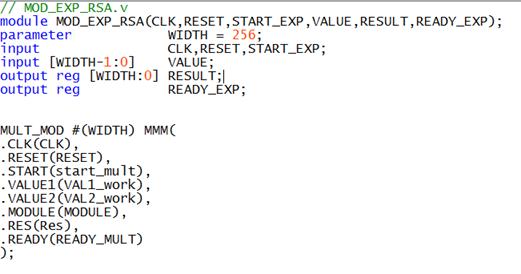

Сообщение принимается в виде 32 посылок по 8 бит. Сделано это из-за специфики алгоритма RSA. Модуль и его секретный ключ хранится в ПЛИС изначально. Размер ключа составляет 256 бит. Для формирования ЭЦП было разработано 2 модуля: модуль умножения по модулю и модуль возведения в степень по модулю. Модули являются параметризируемыми, это значит, что размеры ключа могут быть изменены перед синтезом проекта и «зашиты» в ПЛИС. Листинг модуля умножения по модулю показан на рис. 41 и 42.

Рис. 41. Модуль умножения по модулю.

Рис. 42. Основной алгоритм на языке Verilog.

По сигналу приема полного сообщения модуль формирования ЭЦП начинает работу. Сообщение передается в нужный регистр модуля и происходит процесс формирования ЭЦП. Процесс длится 8 мс и на выходе сформированная ЭЦП и исходное сообщение перенаправляются в память по кускам в 32 бита. Листинг модуля показан на рис. 43.

Рис. 43. Листинг модуля формирования ЭЦП.

Модуль передатчика по Ethernet.

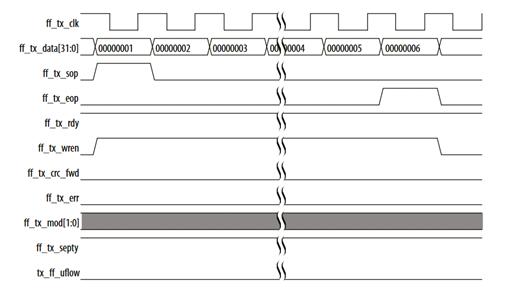

После формирования ЭЦП, по сигналу готовности модуля из памяти в модуль передатчика по Ethernet поступает части сообщения и ЭЦП по 32 бита. Первым идет сообщение, затем ЭЦП. По сигналу готовности модуль передатчика формирует сигнал ff_tx_sop и ff_tx_wren. Сигнал ff_tx_sop показывает MAC уровню о том, что пошла первая 32-разрядная пачка и переходит в активное состояние. Сигнал ff_tx_wren активен на всем промежутке передачи данных. После передачи всех 512 бит информации из памяти становится активен сигнал ff_tx_eop. Он становится активным, когда из памяти приходит последняя посылка. Временная диаграмма цикла передачи показана на рис. 44.

Рис. 44. Временная диаграмма передачи по

Ethernet.

Заключение

В ходе выполнения дипломной работы были изучены основы криптографии, а именно принципы работы симметричного и асимметричного шифрования, подробно был рассмотрен алгоритм шифрования AES. Также были рассмотрены протоколы распределения ключей и по результатам анализа существующих решений был изучен и реализован протокол Диффи-Хеллмана. Помимо этого, были рассмотрены методы передачи данных в локальной сетиинтернет. Результатом данной работы являются выполненные модули для шифрования и расшифровки, передачи и приема сообщения, а также модуль генерации общего ключа. В дальнейшем для развития и улучшения полученных результатов можно реализовать протокол передачи TCP или STS без использования встроенных библиотек C#, также возможно выбрать более сложный протокол распределения ключей, обеспечивающий более высокую защиту, а для уменьшения количества итераций функций шифрования и расшифровки алгоритм AES можно заменить алгоритмом ГОСТ Р 34.12-2015 [26].

В ходе выполнения данной дипломной работы были

изучены преимущества использования криптографических алгоритмов на ПЛИС.

Поскольку обычно компании специализирующиеся на криптографической защите

информации используют свои алгоритмы защиты (кроме ГОСТ 34.10-2012[24])

использование алгоритма RSA в качестве надежного алгоритма формирования

электронно-цифровой подписи, например в структурах государственной оборонной

промышленности или космических технологий, нецелесообразно, нотем не менее, для

показательного примера преимущества использования ПЛИС в криптографии результат

очевиден. Так же с использованием технологий фирмы Altera был реализован

физический и канальный уровень модели OSI на ПЛИС. В перспективе предполагается

разработка криптографического модулей формирования ЭЦП и хэшфункций на ПЛИС

ГОСТ 34.10-2012[24] и ГОСТ 34.11.2012[25], которые одобрены ФСБ Россиии

применение этих алгоритмов в АО «Концерн «Автоматика».

Список источников

Блог компьютерного специалиста [Электронный ресурс]. - Режим доступа: http://www.lostop.ru/ (Дата обращения: 01.04.2017).

Национальный открытый университет «ИНТУИТ» [Электронный ресурс]. - Режим доступа: http://www.intuit.ru/ (Дата обращения: 10.02.2017).

Gilmore J. Cracking DES: Secrets of Encryption Research, Wiretap Politics & Chip Design. - 1998.M., Mishra P. A comparative survey on symmetric key encryption techniques //International Journal on Computer Science and Engineering. - 2012. - Т. 4. - №. 5. - P. 877.[Электронный ресурс]. - Режим доступа: http://networkdoc.ru/ (Дата обращения: 01.04.2017).

Панасенко С. П. Алгоритмы шифрования. Специальный справочник. - БХВ-Петербург, 2009. - C. 135 - 141.[Электронный ресурс]. - Режим доступа: http://infotecs.ru/ (Дата обращения: 19.03.2017).

Информационная безопасность: ФСТЭК, инсайдеры, шифрование, ЭЦП, вирусы, трояны, спам [Электронный ресурс]. - Режим доступа: http://www.itsec.ru/main.php (Дата обращения: 20.03.2017).

Хабрахабр [Электронный ресурс]. - Режим доступа: https://habrahabr.ru/ (Дата обращения: 15.01.2017).[Электронный ресурс]. - Режим доступа: http://cryptowiki.net/ (Дата обращения: 01.02.2017).[Электронный ресурс]. - Режим доступа: https://www.opengsm.ru/ (Дата обращения: 29.03.2017).

Daemen J., Rijmen V. Rijndael specification //AES specification. - 2004.

MSDN - сеть разработчиков Microsoft [Электронный ресурс]. - Режим доступа: https://msdn.microsoft.com/ru-ru/default.aspx (Дата обращения: 01.02.2017).

Rahman M., Rokon I. R., Rahman M. Efficient hardware implementation of RSA cryptography // 2009 3rd International Conference on Anti-counterfeiting, Security, and Identification in Communication. - IEEE, 2009. - P. 316-319.S. FPGA implementation of RSA encryption system. - 2012. - P. 2-4.C. C., Tseng S. Y. Integrated design of AES (Advanced Encryption Standard) encrypter and decrypter // Application-Specific Systems, Architectures and Processors, 2002. Proceedings. The IEEE International Conference on. - IEEE, 2002. - P. 277-285.R. et al. FPGA Implementation of RSA cryptosystem // World Academy of Science, Engineering and Technology, International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering. - 2008. - Vol. 2. - No. 8. - P. 1667-1671.D. et al. Implementation of RSA cryptoprocessor based on Montgomery algorithm // Solid-State and Integrated Circuit Technology. Proceedings. IEEE 1998 5th International Conference. - IEEE, 1998. - P. 524-526. S. RSA Security’s Official Guide To Cryptography. - 2001. - P. 98-105.B. Applied cryptography: protocols, algorithms, and source code in C. - John Wiley & Sons, 2007. - P. 384-387.

ГОСТ Р. 34.10 2012 Процессы формирования и проверки электронной цифровой подписи //М.: Изд-во стандартов. - 2012.

Гост Р. Р 34.11-2012: Национальный стандарт Российской Федерации. Информационная технология. Криптографическая защита информации. Функция хэширования. Издание официальное //М. Стандартинформ. - 2012.

ГОСТ Р. Р 34.12-2015 //Информационная технология. Криптографическая защита информации. Блочные шифры. М.: Стандартинформ. - 2015.V. R., Gad R. S., Naik G. M. Implementation of gigabit ethernet standard using fpga //International Journal of Mobile Network Communications & Telematics (IJMNCT). - 2012. - Т. 2. - №. 4.