Материал: Проектування спеціалізованого мікрокомп’ютера з неоптимізованою системою команд

Проектування спеціалізованого мікрокомп’ютера з неоптимізованою системою команд

КУРСОВА РОБОТА

з дисципліни

Цифрові ЕОМ

Проектування

спеціалізованого мікрокомп’ютера з не оптимізованою системою команд

Технічне

завдання

1. Спроектувати спеціалізований мікрокомп’ютер з не оптимізованою системою команд.

. Вихідні дані:

) область призначення - рішення науково-технічної задачі F=Sh(Z1*Z2);

) елементна база - МПК КМ1804 (ВУ4, ВС1, ВР1), КР1533;

) адресний простір пам’яті АП=64 Кслів;

) ємність ОЗП NRAM=48Кслів, ІМС К132РУ10;

) ємність ПЗП NROM=16Кслів, ІМС КМ555PE4;

) кількість ПВВ NПВВ=32;

) адресність команд АК=3;

) адреса першої команди програми 100h;

) довжина машинного слова n=24;

) команди та дані мають однакову довжину, що дорівнює довжині машинного слова;

) для адресації ПВВ використовується адресний простір пам’яті;

) за ІМС малої та середньої інтеграції використовується серія КР1533.

. Креслення:

) Схема алгоритму рішення задачі.

) Схема алгоритму функціонування мікрокомп’ютера.

) Структурна схема мікрокомп’ютера.

) Формат мікрокоманди.

) Принципова схема мікрокомп’ютера.

ЗМІСТ

Вступ

. Система команд мікрокомп’ютера

.1 Схема алгоритму рішення задачі

.2 Програма задачі в змістовній формі

. Розподіл адресного простору пам’яті

. Визначення формату команди

.1 Довжина поля КОП

.2 Кодування машинних операцій

.3 Вибір режиму адресації

.3.1 Пряма адресація

.3.2 Опесердковано-регістрова адресація

. Формати команд і алгоритм функціонування мікрокомп’ютера

.1 Формати і цикли команд

.2 Схема алгоритму функціонування мікрокомп’ютера

. Програмно-мікропрограмна модель мікрокомп’ютера

. Мікропрограми операцій

.1 Арифметичні операції

.1.1 Операція «Додавання»

.1.2 Операції «Множення» і «Ділення»

.1.3 Операція «Множення»

.1.4 Операція «Ділення»

.1.5 Операція умовного переходу JNZ

.1.6 Такт збереження ТО3

.2 Мікропрограми тактів Твк, ТО1, ТО2

.2.1 Такт вибірки команди Твк

.2.2 Такти вибірки операндів То1, То2

.2.3 Мікропрограма IPL

.3 Такт декодування коду операції Тд

.4 Розподіл адресного простору пам’яті мікрокоманд

. Структурна схема мікрокомп’ютера

.1 Процесор

.1.1 Блок мікропрограмного керування

.1.2 Блок регістрів

.1.3 Блок обробки даних БОД

.2 Пам’ять

.2.1 Оперативна пам’ять

.2.2 Постійна пам’ять

.2.3 Дешифратор ПВВ

.2.3 Дешифратор DC АП

.3 Генератор тактових імпульсів (ГТІ)

. Формат мікрокоманди.

. Закодована мікропрограма мікрокомп’ютера

Висновки

Список

використаних джерел

Вступ

Завданням даного курсового проекту було спроектувати спеціалізований мікрокомп’ютер.

Процес проектування буде розділений на два етапи: архітектурний та технічний. На архітектурному етапі буде розроблений алгоритм рішення задачі, визначена система команд, розроблений алгоритм функціонування мікрокомп’ютера, розроблені мікропрограми арифметичних, логічних операцій та основних тактів, розроблена структура мікрокомп’ютера, а також вибрані оптимальні мікросхеми для їх реалізації. Результатом технічного етапу буде принципова схема.

.

1. Система команд мікрокомп’ютера

.1 Схема

алгоритму рішення задачі

Задача F=Sh(Z1*Z2)

відноситься

до класу науково-технічних. Для обчислення функції Sh

використовується степеневий ряд:

Схема алгоритму рішення

задачі наведена нижче і деталізована до арифметичних операцій (операторів

присвоювання). Зі схеми випливає такий набір арифметичних операцій: { + , * , /

}.

1.2

Програма задачі в змістовній формі

Програма задачі наведена в табл. 1.

З неї випливає система операцій мікрокомп’ютера:

{ + , * , / , JNZ

, HLT}.

Отже, загальне число машинних операцій М=5.

Таблиця 1

|

№ |

КОП |

А1 |

А2 |

A3 |

|

1 |

* |

Z1 |

Z2 |

R1 |

|

2 |

* |

R1 |

R1 |

R1 |

|

3 |

+ |

k |

k |

R2 |

|

4 |

+ |

R2 |

<1> |

R3 |

|

5 |

* |

R2 |

R2 |

R3 |

|

6 |

/ |

R1 |

R3 |

R3 |

|

7 |

* |

R3 |

Uk-1 |

Uk |

|

8 |

+ |

Uk |

<0> |

Uk-1 |

|

9 |

+ |

∑Uk |

Uk |

∑Uk |

|

10 |

+ |

k |

<1> |

k |

|

11 |

JNZ |

3 |

- |

- |

|

12 |

+ |

U0 |

∑Uk |

F |

|

13 |

HLT |

- |

- |

- |

. Розподіл адресного простору пам’яті

Адресний простір пам’яті АП=64Ксл розподіляться для розміщення підмножин адрес RAM, ROM та ПВВ.

Підмножина адрес RAM

NRAM=48Kсл,

nA

RAM=]log248K[=16;

число шістнадцяткових цифр в адресі дорівнює 16/4 = 4.

Діапазон адрес RAM (0000h - BFFFh).

Підмножина адрес ROM

NROM=4Ксл,

nA

ROM=]log24K[=12;

число шістнадцяткових цифр в адресі дорівнює 12/4 = 3.

Діапазон адрес RОM (000h - FFFh).

Підмножина адрес ПВВ

NПВВ=32, nA ROM=]log232[=5

Діапазон адрес ПВВ (00h

- 1Fh).

Адресний простір АП=64Ксл. Необхідна розрядність адреси:

nA АП=]log264K[=16; число шістнадцяткових цифр в адресі дорівнює

6/4 = 4.

Діапазон адрес АП (0000h - FFFFh).

Можливий розподіл АП пам’яті

показаний на рис. 1. Максимальне значення адрес пам’яті:

Amax=D01Fh.

Цьому значенню відповідає довжина двійкової фізичної адреси коду n=16.

Таким чином, адресна шина мікрокомп’ютера має 16 ліній.

Рис. 1

Такому розподілу АП пам’яті

відповідає структурна схема вибору RAM,

ROM, ПВВ, що зображена

на рисунку 2.

Рис. 2

.

Визначення формату команди

Відповідно до технічного завдання

команда має структуру:

3.1

Довжина поля КОП

Мінімальна довжина поля КОП визначається за формулою:

nКОП=]log2(M+1)[=]log2(5+1)[=3

3.2

Кодування машинних операцій

Ніяких обмежень на коди операцій в полі КОП немає, тому використовуємо довільні значення кодів.

Коди машинних операцій подано в

табл.2.

Таблиця 2

|

КОП(15:13) |

Операція |

|

000 |

NOP - нема операції |

|

001 |

+ - додавання |

|

010 |

* - множення |

|

011 |

/ - ділення |

|

100 |

JNZ - умовний перехід |

|

101 |

HLT - зупинка |

3.3 Вибір

режиму адресації

.3.1 Пряма адресація

Коди адрес А1(А2,A3) є фізичними. Довжина адресного поля А1(А2,A3)

визначається за формулою:

A1(A2,A3)=(n-nКОП)/3=(24-3)/3=7.

Через те, що nA1(A2,A3)=7<nФА=16,

використання прямої адресації неможливе.

3.3.2 Опесердковано-регістрова адресація

У цьому випадку команда має

структуру:

де ПА1(ПА2,ПА3) - однака режиму адресації

- регістрова

ПА1(ПА2,ПА3) =

- опосередкована

R1(R2,R3) - адреси РЗП.

Нехай кількість РЗП NРЗП=8. Тоді довжина поля R1(R2) буде

Ri=]log2NРЗП[=]log28[=3.

Перевіримо виконання умови

КОП+3*nПАі+3*nRi=3+3+9=15<n=24.

Використання опосередковано-регістрової адресації можливе.

Формат команди мікрокомп’ютера буде:

.

Формати команд і алгоритм функціонування

мікрокомп’ютера

4.1

Формати і цикли команд

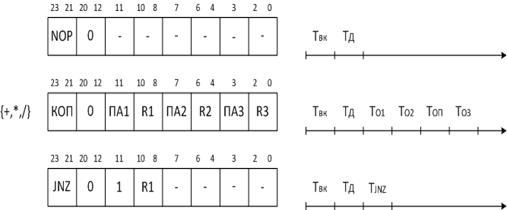

На рис.3 наведені формати і цикли команд мікрокомп’ютера. Перші два

такти Твк та Тд

є спільними для усіх команд і реалізують вибірку команд з пам’яті та їх

декодування. Такти ТО1 та ТО2 забезпечують вибірку

операндів на мікрокомандні регістри внутрішньої пам’яті

мікокомп’ютера.

Рис.3

.2 Схема

алгоритму функціонування мікрокомп’ютера

Схема алгоритму являє собою сукупність мікропідпрограм (МПП):

- IPL - пуск мікрокомп’ютера та завантаження початкової адреси в програмний лічильник;

Твк - вибірка команди з пам’яті;

ТО1, ТО2 - вибірки першого та другого операндів;

(+,*,/) - відповідні арифметичні операції;

- TO3 - запис результату;

- JNZ - операція умовного переходу;

- HLT - зупинка мікрокомп’ютера.

Переключальній вершині КОП відповідає такт декодування коду операції.

.

Програмно-мікропрограмна модель мікрокомп’ютера

Модель мікрокомп’ютера базується на використанні ВІС КМ1804ВС1, що має регістрову пам’ять ємністю в 16 слів.

У програмній моделі відображені

регістри, які представляються в командах мікрокомп’ютера;

в мікропрограмній моделі - регістри, вмістом яких оперують мікрокоманди. Моделі

мікрокомп’ютера відповідає

структура проілюстрована на рис.4.

Рис. 4

Регістри R0-R7 є регістрами загального призначення (РЗП). Регістр R8 - програмний лічильник (ПЛ). Регістри R9-R15 є програмно доступними, причому R9, R10 використовуються для зберігання операндів після тактів ТО1 і ТО2, а регістр R11 - для запису результату після завершення такту ТО3.

Регістри RDI, RDO призначені для короткочасного зберігання даних під час запису в ОП та при читанні з неї. Регістр RA зберігає адресу звернення до ОП.

Регістр команд RK зберігає код команди.

Кнопковий регістр Rкн фіксує адресу першого командного слова програми.

.

Мікропрограми операцій

.1 Арифметичні

операції

.1.1 Операція «Додавання»

Цю операцію ВІС реалізує апаратно.

Мікропрограма операції показана на рис. 5.

Рис.5

пам'ять мікропрограма алгоритм мікрокомп'ютер

Тривалість такту операції Т+=Р+*τ,

де Р+=1 - кількість процесорних тактів, τ-тривалість

процесорного такту.

Т+=τ

6.1.2 Операції «Множення» і «Ділення»

У списку операцій ІМС ВС1 операції

«*» і «/» відсутні, тому в КП вони реалізуються мікропрограмо. Операції «*» і

«/» простіше виконувати над даними в прямому коді. Вважатимемо, що операнди

завжди додатні числа, що дозволяє нам дещо спростити загальний алгоритм

операцій «*» і «/».

6.1.3 Операція «Множення»

Архітектура ВС1 орієнтована на

реалізацію першого алгоритму: множення починається з молодших розрядів

множника, сума часткових добутків зсувається вправо. Цьому алгоритму відповідає

мікропрограмна модель, зображена на рис.6.

Рис.6

Алгоритм множення в змістовній формі.

. Співмножники розміщені в регістрах R9, R10.

. Перевірка на рівність нулю значень співмножників.

. Множник з R10 пересилається в регістр RQ.

. Сумі часткових добутків (R10) присвоюємо значення «0».

. Вміст RQ зсуваємо вправо на один розряд.

. Аналізуємо молодший розряд множника (стан тригера Т). Якщо Т=1,

до суми часткових добутків додається множене (R9). Якщо Т=0, до суми часткових добутків додається «0». Утворені суми часткових добутків та множник в RQ зсуваються вправо на один розряд.

. Пункт 6 повторяються для всіх розрядів множника.

. Старша частина добутку буде розміщена в R10, молодша частина

добутку - в RQ. Вважаємо, що старша частина 2n-розрядного добутку (в R10) дорівнює 0. Тому добуток буде n-розрядним і пересилається з RQ в R10.

. Кінець.

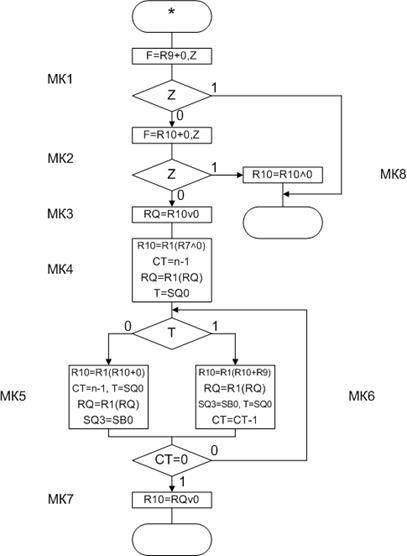

Граф мікропрограми (ГМП) операції множення показаний на рис.7.

З нього випливає: кількість мікрокоманд k*=7; число процесорних тактів

![]() , де p*min=1

, де p*min=1

p*max=4+(24-1)*1+1=28

=> p*=](28+1)/2[=15

Тривалість такту операції множення

буде Т*=Р**τ=15τ

Рис.7

6.1.4 Операція «Ділення»

Використовуємо першу схему ділення:

ділене (залишки) зсуваються вліво, дільник - нерухомий. Мікропрограмна модель

операції зображена на рис.8. Вважаємо, що ділене має завжди формат слова. При

реалізації алгоритму ділене повинно представлятися у форматі подвійного слова.

Старшу частину діленого розміщуємо в R10,

молодшу - в RQ.

Тому вміст R7=0, a

RQ≠0.

Рис.8.

Реалізація алгоритму починається з перевірки на рівність нулю діленого (R10) та дільника (R9). Якщо умови не виконуються, то ділене пересилається в RQ і в R10 завантажується нуль. Таким чином формується ділене в подвоєному форматі.

У процесі операції в регістрах R10 i RQ формується залишок і при їх подвоєнні звільняються молодші розряди RQ, в які послідовно записуються значення цифр частки, починаючи зі старших розрядів. Значення цифр частки протилежне знаку утвореного нового залишку. На рис.8 відтворена схема формування подвоєного залишку і цифри частки. ГМП ділення, що показаний на рис.9 реалізує алгоритм без відновлення залишку. З нього випливає: