Материал: m012203d

Frequenzzähler, 750-404/000-003

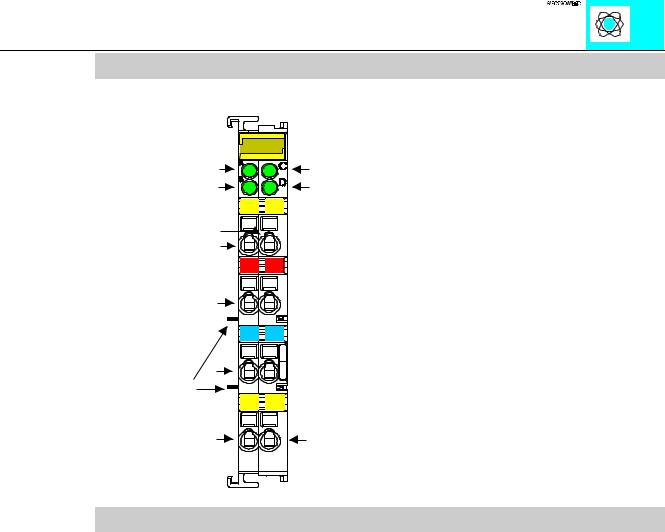

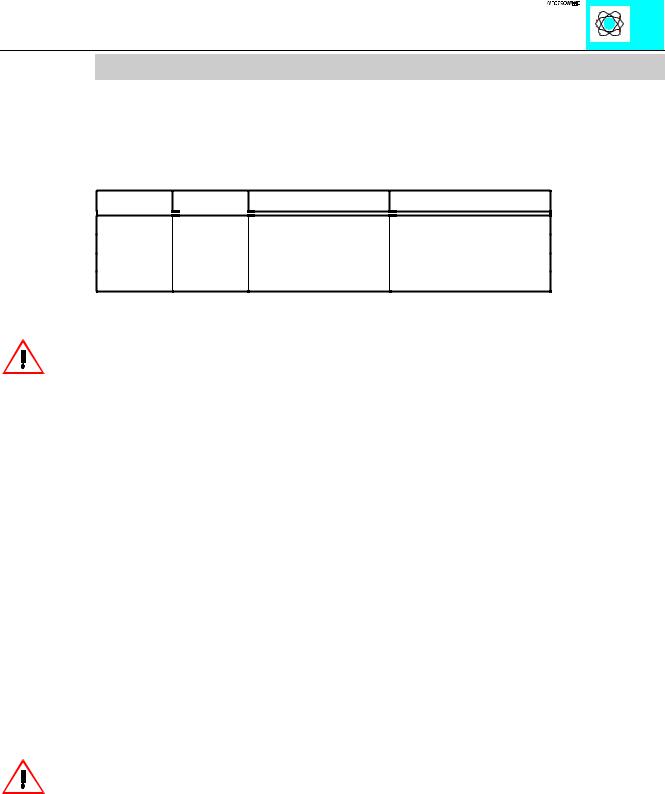

Status Gate |

|

Status CLOCK |

Q1 |

|

Q2 |

|

G |

+E2Clk |

Clock |

|

|

Gate |

+ |

+ |

|

||

|

24V |

24V |

24V |

|

|

|

- |

- |

|

0V |

0V |

0V |

|

|

power jumper |

Q1 |

Q2 |

contacts |

S |

S |

|

|

|

Q1 |

|

Q2 |

750-404

000-003

Technische Beschreibung

Die vorliegende Zählerklemme kann auch mit der Einstellung Frequenzzähler bestellt werden. Sie hat dann die zwölfstellige Bestellnummer 750-404/000-003.

Das Zählermodul 750-404/000-003 mißt die Periode des 24 V DC Eingangssignals am Eingang CLOCK und wandelt es in einen Frequenzwert um. Die Messung ist eingeschaltet, wenn der GATE Eingang offen ist oder 0 V anliegen. Bei beschaltetem GATE Eingang wird nicht gezählt.

Die Ausgänge A1 und A2 sind digitale Ausgänge und können über das Steuerbyte aktiviert werden.

Durch eine LED wird angezeigt, ob die Einund Ausgänge gesetzt sind.

Um niedrige Frequenzen detektieren zu können, ist die maximale Zeit zwischen zwei Daten Updates einstellbar.

Vorwärts / Rückwärtszähler 750-404 |

8 |

:$*2Ç, 2Ç6<67(0

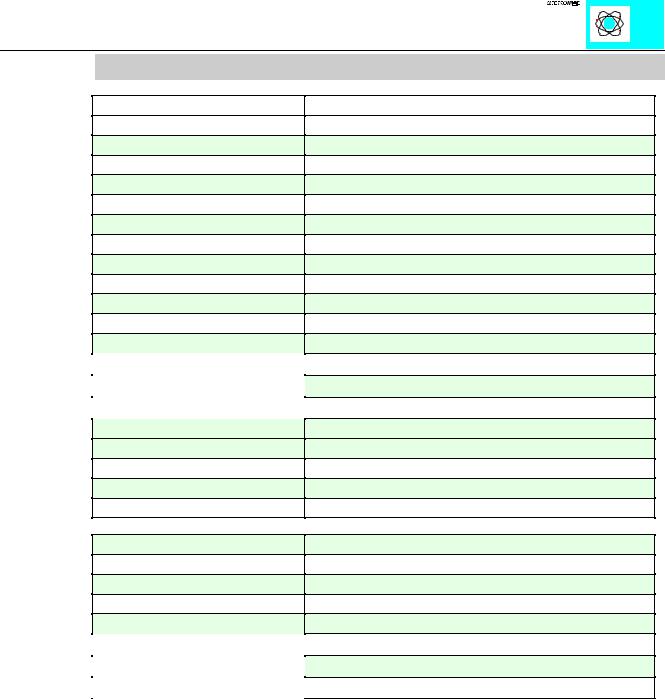

Technische Daten

Artikelnr.

Nennspannung

Signalspannung (0)

Signalspannung (1)

Eingangsstrom

Minimale Pulsweite

Ausgangsstrom

Spannungsabfall

Frequenzbereich

Integrationszeit = 1 Periode

Integrationszeit = 4 Perioden

Integrationszeit = 16 Perioden

Meßfehler

Bereich |

0.1 |

- |

100 Hz |

Bereich |

1 |

- |

1000Hz |

Bereich |

10 |

- 10000Hz |

|

Interne Bitbreite

interne Stromaufnahme

Betriebstemperatur

Anschlußtechnik

Abmessungen (mm) BxHxT

Frequenzbereich

Integrationszeit = 1 Periode

Integrationszeit = 4 Perioden

Integrationszeit = 16 Perioden

Meßfehler:

Bereich 0.1 |

- |

8000Hz |

|

Bereich |

0.25 - |

32000Hz |

|

Bereich |

1 |

- |

100000Hz |

750-404/000-003

24V DC (-15%/+20%)

-3V - 5V DC

15V - 30V DC

5mA typ.

10µs

0.5A (kurzschlußfest)

0.6V DC max. bei 0.5A

0.1 - 100Hz, Auflösung 0.001Hz

1 - 1,000Hz, Auflösung 0.01Hz

10- 10,000Hz, Auflösung 0.1Hz (1Hz)

<± 0.05%

<± 0.05 %

< ± 0.2 %

8 Bit Kontrolle/Status + 32 Bit Daten

80mA max. bei 5V DC

0°C....+55°C

CAGE CLAMP; 0.08 bis 2.5mm2

12 x 64* x 100 (*ab Oberkante Tragschiene)

0.1 - 8,000Hz, Auflösung 0.001Hz

0.25 - 32,000Hz, Auflösung 0.01Hz

1- 100,000Hz, Auflösung 0.1Hz (1Hz)

<± 1%

<± 1.5 %

<± 1.5 %

Vorwärts / Rückwärtszähler 750-404 |

9 |

:$*2Ç, 2Ç6<67(0

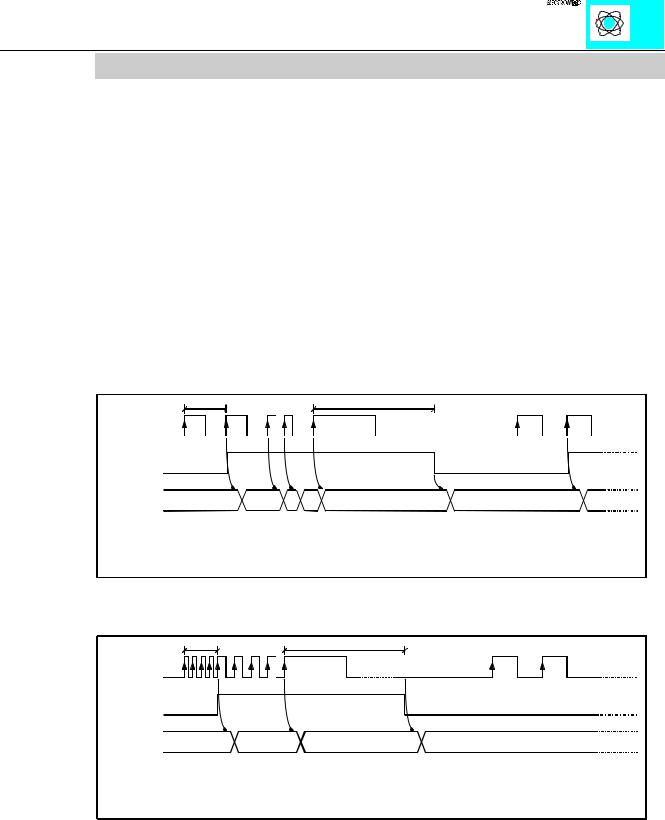

Funktionsbeschreibung

Das Zählermodul erfaßt die Zeit zwischen einer oder mehreren steigenden Flanken des CLOCK Eingangssignals und berechnet die Frequenz dieses Signals.

Die Berechnung und das Update des Prozeßabbilds werden bei jeder 1., 4. oder 16. steigenden Flanke vorgenommen. Dies ist abhängig von der Integrationszeit, die im Steuerbyte eingestellt wurde. Bei der ersten Detektion einer steigenden Flanke startet die zyklische periodische Messung. Hier kann noch kein gültiger Frequenzwert geliefert werden. In diesem Fall sendet das Modul 0xFFFFFFFFH als Eingangsinformation. Der gleiche Eingangswert wird zurückgegeben, wenn ein statisches High oder Low Signal am CLOCK Eingang anliegt.

Wenn keine Signalwechsel am CLOCK Eingang vorkommen, kann das Modul ein Update des Prozeßabbilds auch nach definierten parametrierbaren Zeitspannen vornehmen. In diesem Fall wird das Modul ebenfalls den ungültigen Wert 0xFFFFFFFFH aussenden.

Das folgende Bild zeigt einen Prozeßdatenzyklus.

|

|

73 |

|

7 |

|

|

,1387 )5(4 |

|

|

|

|

|

|

'$7$ 9$/,' |

|

|

|

|

|

|

352&(66 '$7$ |

[)))))))) |

' ' |

' ' |

[)))))))) |

' ' |

|

|

|

|

|

|

|

|

|

|

|

|

' ' ' ' |

|

|

' ' |

,QSXW 'DWD |

|

|

|

|

|

73 |

I |

FXUUHQW SHULRG |

|

|

|

|

7 |

|

0D[LPXP GDWD KROG WLPH SDUDPHWHUL]DEOH |

|

|

||

Zeitdiagramm für die Prozeßdaten Update Sequenz |

|

|

||||

(Integrationszeit = 1 Periode) |

|

|

||||

|

|

7 |

|

|

|

|

,1387 )5(4 |

|

|

|

|

|

|

'$7$ 9$/,' |

|

|

|

|

|

|

352&(66 '$7$ |

[)))))))) |

' ' |

' ' |

[)))))))) |

|

|

' ' |

,QSXW 'DWD |

|

|

|

|

|

73 |

I |

FXUUHQW SHULRG |

|

|

|

|

7 |

|

0D[LPXP GDWD KROG WLPH SDUDPHWHUL]DEOH |

|

|

||

Zeitdiagramm für die Prozeßdaten Update Sequenz (Integrationszeit = 4 Perioden)

Vorwärts / Rückwärtszähler 750-404 |

10 |

:$*2Ç, 2Ç6<67(0

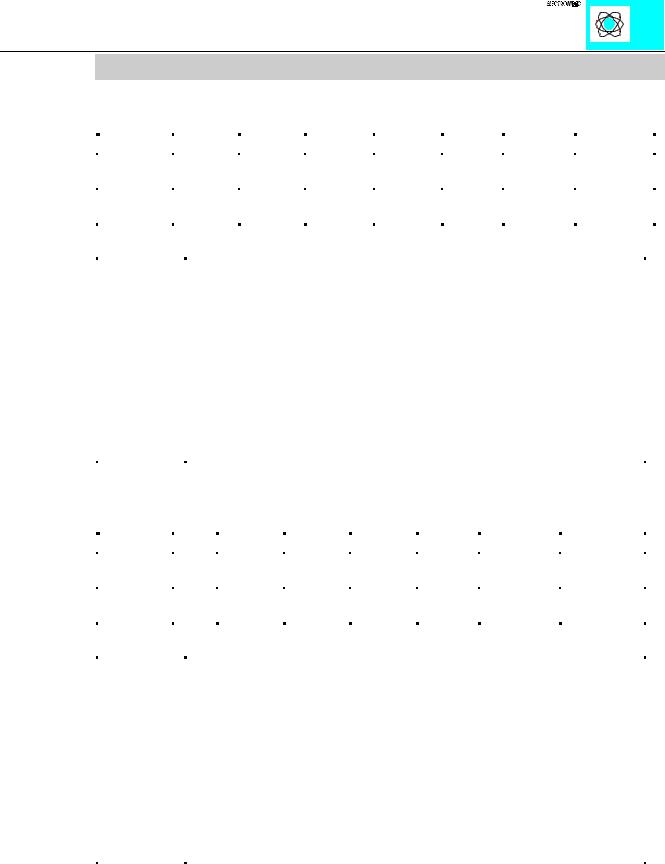

Aufbau der Einund Ausgangsdaten

Das Steuerbyte enthält folgende Bits:

|

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

|

REG_REQ |

0 |

0 |

TVD REQ |

SET_Q2 |

SET_Q1 |

RANGE_SEL |

RANGE_SEL |

=0 |

|

|

|

|

|

REQ1 |

REQ0 |

|

|

|

|

|

|

|

|

||

|

REG_REQ |

NRD/WR |

REG_A5 |

REG_A4 |

REG_A3 |

REG_A2 |

REG_A1 |

REG_A0 |

=1 |

|

|

|

|

|

|

|

|

Bit |

Beschreibung |

|

|

|

|

|

|

|

REG_REQ |

Zugang zu der Registerstruktur wird gefordert, b5 bis b0 enthält die Adresse des |

|

|

Registers |

|

REG_A5...A0 |

Register Adresse (0-63) |

|

TVD REQ |

Forderung, die maximale Zeit mit gültigen Daten zu ändern. |

|

SET_Q2 |

Control Ausgang A2 (0: A2 off, 1: A2 on) |

|

SET_Q1 |

Control Ausgang A1 (0: A1 off, 1: A1 on) |

|

RANGE_SEL |

Auswahl der Integrationszeit und Darstellung der gemessenen Frequenzwerte (s.u.) |

|

REQ1 |

|

|

RANGE_SEL |

Auswahl der Integrationszeit und Darstellung der gemessenen Frequenzwerte(s.u.) |

|

REQ0 |

|

STATUS Byte

|

b7 |

b6 |

b5 |

b4 |

b3 |

b2 |

b1 |

b0 |

|

REG_ACK |

0 |

ST_GAT |

TVD ACK |

ST_Q2 |

ST_Q1 |

RANGE_SEL |

RANGE_SEL |

=0 |

|

E |

|

|

|

ACK1 |

ACK0 |

|

|

|

|

|

|

|

|||

|

REG_ACK |

0 |

REG_A5 |

REG_A4 |

REG_A3 |

REG_A2 |

REG_A1 |

REG_A0 |

=1 |

|

|

|

|

|

|

|

|

Bit |

Beschreibung |

|

|

|

|

REG_ACK |

Bestätigung der Registeranforderung, b5 bis b0 enthalten die Adresse der Register |

|

REG_A5...A0 |

Register Adresse (0-63) |

|

ST_GATE |

Status des GATE Eingangs (0=enabled, 1=disabled) |

|

TVD ACK |

Bestätigung eines Wechsels von T VD |

|

ST_A2 |

Status Ausgang A2 |

|

ST_A1 |

Status Ausgang A1 |

|

RANGE_SEL |

Bestätigung der Bereichsauswahl, Frequenzwerte sind gültig (s.u.) |

|

ACK1 |

|

|

RANGE_SEL |

Bestätigung der Bereichsauswahl, Frequenzwerte sind gültig (s.u.) |

|

ACK0 |

|

Vorwärts / Rückwärtszähler 750-404 |

11 |

:$*2Ç, 2Ç6<67(0

Struktur der Eingangsund Ausgangsdaten

Die Eingangsdaten enthalten die CLOCK Frequenz als binären Wert. Die Darstellung ist abhängig davon, wie die RANGE_SEL Bits im Steuerbyte gesetzt sind. Auch die Methode der Messung wird über diese Bits gewählt. Die folgende Tabelle zeigt die unterschiedlichen Betriebsarten.

5$1*(B6(/

5$1*(B6(/ 0HWKRGH GHU 0HVVXQJ

,QWHJUDWLRQ •EHU 3HULRGH

,QWHJUDWLRQ •EHU 3HULRGHQ

,QWHJUDWLRQ •EHU 3HULRGHQ

,QWHJUDWLRQ •EHU 3HULRGHQ

'DUVWHOOXQJ GHU :HUWH

)UHTXHQ] LQ +] )UHTXHQ] LQ +] )UHTXHQ] LQ +] )UHTXHQ] LQ +]

ACHTUNG:

Wenn ein neuer Frequenzbereich gefordert wird, gibt es eine Wartezeit bis gültige Daten gelesen werden. Zunächst muß das RANGE_SEL ACK Bit den neuen Frequenzbereich enthalten. Die maximale Verzugszeit kann nach der folgenden Formel berechnet werden

TDmax= 2 * |

Anzahl der Perioden die integriert werden |

aktueller Frequenzwert |

Wenn das Gate enabled ist, enthalten die Eingangsdaten den letzten gültigen Frequenzwert. In diesem Status kann kein neuer Bereich angefordert werden.

Der gültige Frequenzbereich geht von 0.1 Hz (100 D) bis 10 kHz (100000D).

Um statische CLOCK Signale zu erkennen, wurde ein Watchdog Timer implementiert. Der Default Wert für den Timer ist 10 s. Der Timer wird bei jedem Power On neu initialisiert.

Die Applikation kann die Wathcdog Zeit während des Betriebs über das Steuerbyte verändern.

Dieser Vorgang wird gestartet, indem der entsprechende Wert in die Ausgangsbytes OUTPUT_DATA 1 und OUTPUT_DATA 0 geschrieben wird, bevor das TVD REQ Bit in das Steuerbyte geschrieben wird.

Ein erfolgreicher Parametertransfer wird durch das TVD ACK Bit im Statusbyte bestätigt.

ACHTUNG:

Der Bereich des Watchdog Timers geht von 0 bis 16383ms (0x0000H to 0x3FFFH) in Schritten von 1ms per digit.

Werte die den erlaubten Bereich des Watchdog Timers verlassen werden mit 0x3FFF gekennzeichnet.

Wenn die maximal mögliche Frequenz der Bereiche vergrößert wird (s. Tabelle mit maximalen Frequenzbereichen) gibt das Modul den ungültigen Wert 0xFFFFFFFF H. zurück.

Vorwärts / Rückwärtszähler 750-404 |

12 |

:$*2Ç, 2Ç6<67(0