Материал: ЛР 1 подготовка

МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра РС

отчет

по лабораторной работе №1

по дисциплине «Цифровая электроника»

Тема: «Создание простейшей схемы с помощью Quartus 2»

Студент гр. 9492 |

|

Скотаренко Д.Д. |

Преподаватель |

|

Мамчур Р.М. |

Санкт-Петербург

2021

Цель работы.

Изучить основы построения логических схем в пакете Quartus 2.

1) Задание:

;

В-23

;

В-23

2) Таблица истинности:

-

X2

X3

X4

out

0

0

0

0

0

0

1

0

0

1

0

1

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

1

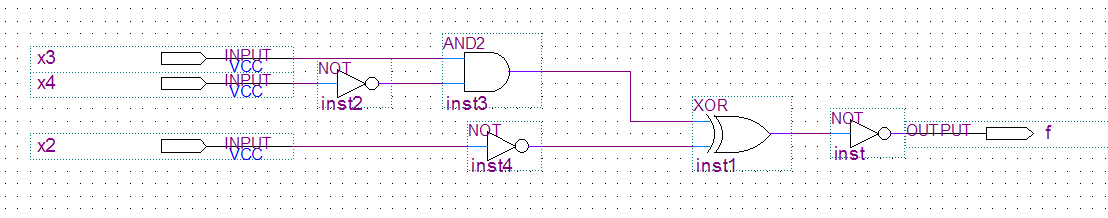

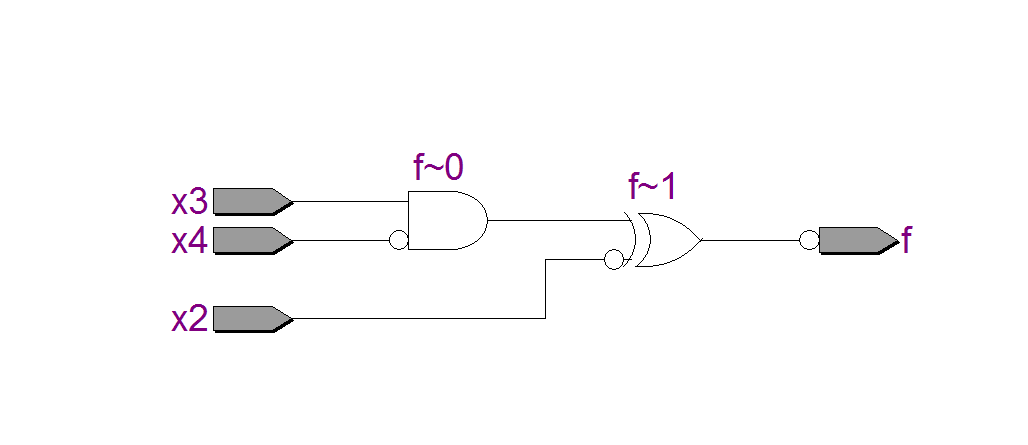

3) Схема в графическом редакторе:

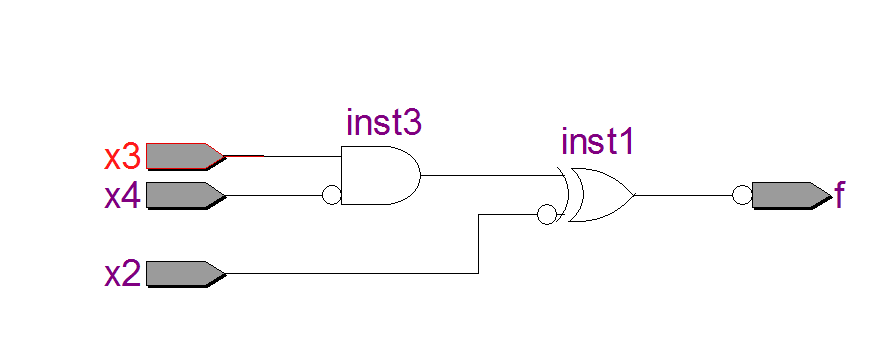

4 )

Представление схемы в RTL

viewer:

)

Представление схемы в RTL

viewer:

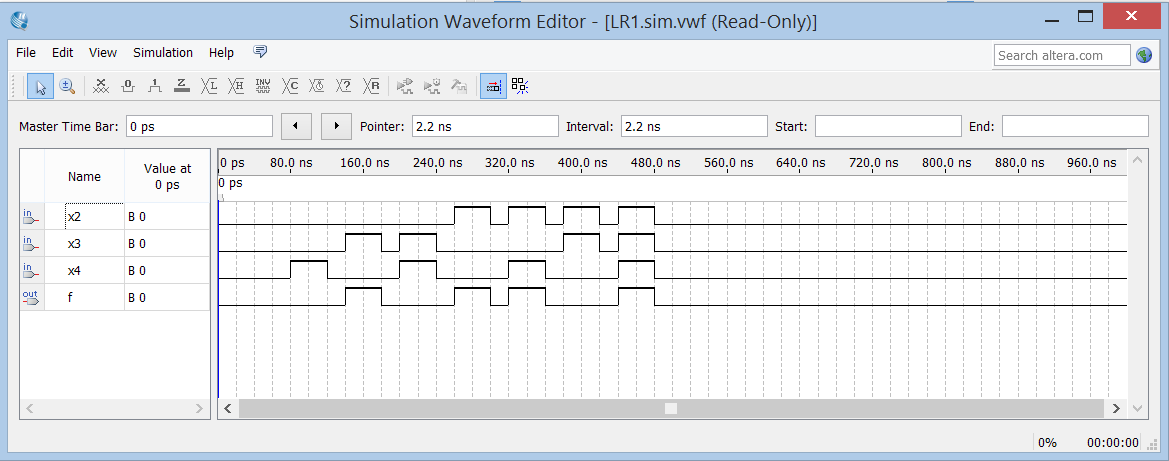

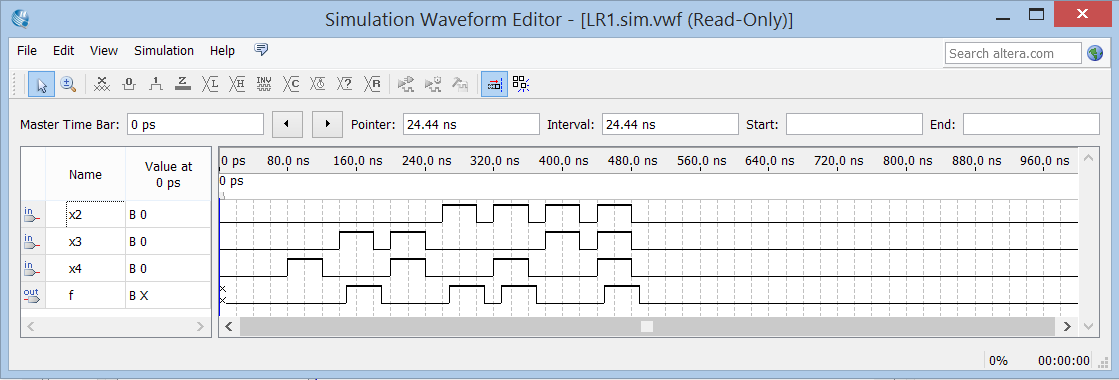

5 )

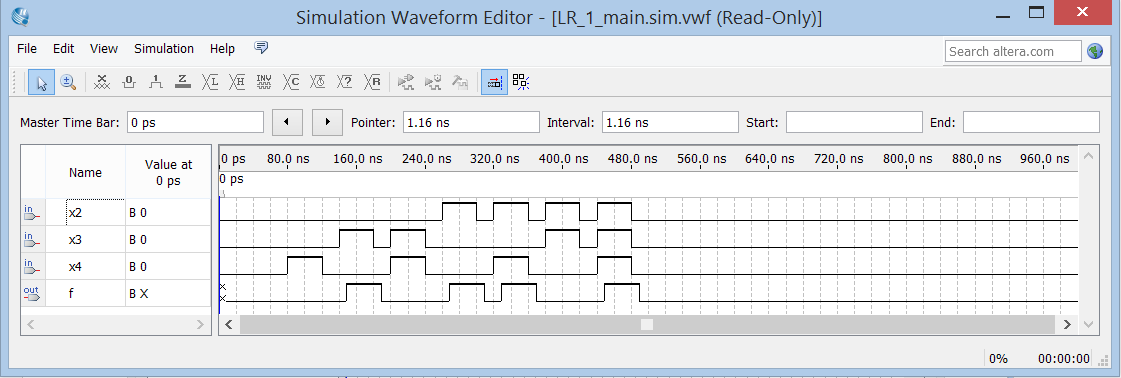

Осциллограммы работы схемы с без учёта

задержек и с учётом задержек:

)

Осциллограммы работы схемы с без учёта

задержек и с учётом задержек:

6 )

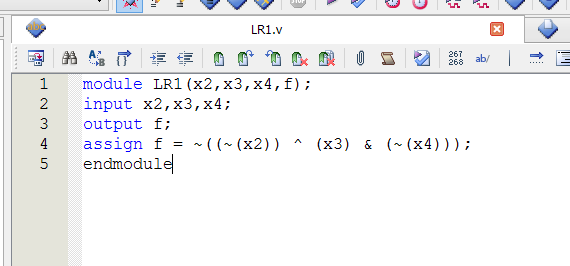

Описание схемы на языке Verilog:

)

Описание схемы на языке Verilog:

7) Представление Verilog-схемы в RTL-viewer:

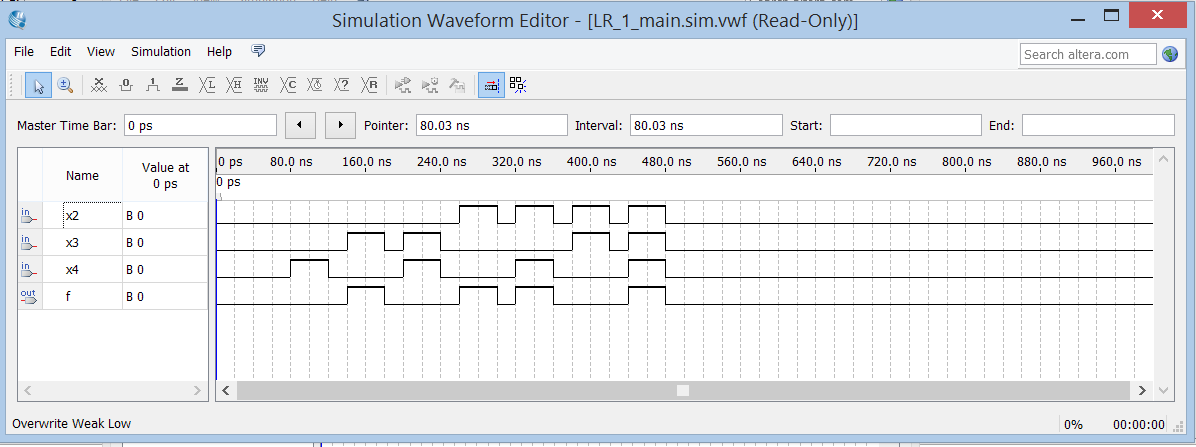

8) Осциллограммы работы Verilog-схемы без учёта задержек и с их учётом:

Вывод:

В ходе данной лабораторной работы мы изучили методы построения простейших схем в графическом редакторе Quartus II. Также мы научились строить осциллограммы работы схемы без учёта временных задержек и с их учётом. В дальнейшем, мы изучили представление схем в RLT-viewer и определять по ним правильность построения нашей схемы по блок-диаграммам или на Verilog. Далее мы научились описывать простейшие схемы на языке Verilog, и работать с ними также, как со схемами из блок-диаграмм. Для схемы на Verilog также были построены осциллограммы работы без учёта задержек и с их учётом. В итоге, все значения из таблицы истинности совпали со значениями выходных сигналов схемы на Verilog и схемы из блок-диаграммы.