Материал: 835

140

шее энергопотребление. Динамическая память используется в качестве основной памяти.

Обычные виды SRAM и DRAM называют также асинхронными — потому, что установка адреса, подача управляющих сигналов и чтение/запись данных могут выполняться в произвольные моменты времени — необходимо только соблюдение временных соотношений между этими сигналами. В эти временные соотношения включены так называемые охранные интервалы, необходимые для стабилизации сигналов, которые не позволяют достичь теоретически возможного быстродействия памяти. Существуют также синхронные виды памяти, получающие внешний синхросигнал, к импульсам которого жестко привязаны моменты подачи адресов и обмена данными; помимо экономии времени на охранных интервалах, они позволяют более полно использовать внутреннюю конвейеризацию и блочный доступ.

Микросхемы памяти имеют четыре основные характеристики — тип, объем, структуру и время доступа. Тип обозначает статическую или динамическую память, объем показывает общую емкость микросхемы, а структура — количество ячеек памяти и разрядность каждой ячейки. Например, 28/32-выводные DIPмикросхемы SRAM имеют восьмиразрядную структуру (8k*8, 16k*8, 32k*8, 64k*8, 128k*8), и кэш для 80486 процессора объе-

мом 256 кБ будет состоять из восьми микросхем 32k*8 или четырех микросхем 64k*8. Две микросхемы по 128k*8 поставить уже нельзя, так как нужна 32-разрядная шина данных, что могут дать только четыре параллельных микросхемы. Распространенные SRAM в 100-выводных корпусах PQFP имеют 32-разрядную структуру 32k*32 или 64k*32 и используются по две или по четыре в платах для Pentium. Аналогично, 30-контактные SIMM имеют 8-разрядную структуру и ставятся с процессорами 80286, 80386SX и 80486SLC по два, а с 80386DX, 80486DLC и обычны-

ми 80486 — по четыре. 72-контактные SIMM имеют 32-раз- рядную структуру и могут ставиться с 80486 по одному, а с

Pentium и Pentium Pro — по два. 168-контактные DIMM имеют

64-разрядную структуры и ставятся в Pentium и Pentium Pro по одному. Установка модулей памяти или микросхем кэша в количестве больше минимального позволяет некоторым платам уско-

141

рить работу с ними, используя принцип расслоения (Interleave — чередование).

Время доступа характеризует скорость работы микросхемы и обычно указывается в наносекундах через тире в конце наименования. Часто на микросхемах указывается минимальное из всех возможных времен доступа — например, распространена марки-

ровка 70 нс EDO DRAM, как 50, или 60 нс EDO DRAM — как 45,

хотя такой цикл достижим только в блочном режиме, а в одиночном режиме микросхема по-прежнему срабатывает за 70 или 60 нс. Аналогичная ситуация имеет место в маркировке PB SRAM: 6 нс вместо 12, и 7 нс — вместо 15. Микросхемы SDRAM обычно маркируются временем доступа в блочном режиме (10 нс или

12 нс).

Модули динамической памяти, помимо памяти для данных, могут иметь дополнительную память для хранения битов четности (Parity) для байтов данных — такие SIMM иногда называют 9- и 36-разрядными модулями (по одному биту четности на байт данных). Биты четности служат для контроля правильности считывания данных из модуля, позволяя обнаружить часть ошибок (но не все ошибки).

Другой разновидностью контроля является ECC (Error Correction Code) — специальный дополнительный код, обнаруживающий и исправляющий большую часть ошибок в основном памяти. Для хранения ECC обычно требуется больше памяти, однако для несложных типов ECC могут использоваться биты четности.

72-контактные SIMM имеют четыре специальных линии PD (Presence Detect — обнаружение наличия), на которых при помощи перемычек может быть установлено до 16 комбинаций сигналов. Линии PD используются некоторыми платами для определения наличия модулей в разъемах и их параметров (объема и быстродействия). В модулях DIMM, в соответствии со спецификацией JEDEC, технология PD реализуется при помощи перезаписываемого ПЗУ с последовательным доступом (Serial EEPROM) и носит название Serial Presence Detect (SPD). ПЗУ представляет собой 8-выводную микросхему, размещенную в углу платы DIMM, а его содержимое описывает конфигурацию и параметры модуля. Системные платы с чипсетами 440LX/BX и выше могут

142

использовать SPD для настройки системы управления памятью. Некоторые системные платы могут обходиться без SPD, определяя конфигурацию модулей обычным путем — это стимулирует выпуск рядом производителей DIMM без ПЗУ, не удовлетворяющих спецификации JEDEC.

5.1 Виртуальная память

Очевидно, что объем памяти, напрямую адресуемый 16разрядным словом не может превысить 216 Б, или 64 кБ. И естественно, что с увеличением сложности и требовательности к ресурсам программного обеспечения стал увеличиваться реальный объем оперативной памяти ПК. Возникла проблема организации доступа к памяти, лежащей за пределом адресного пространства, доступного размеру данного машинного слова. Для решения этой проблемы использовался ряд подходов.

Под виртуальной памятью будем понимать память, построенную аппаратно-программными средствами.

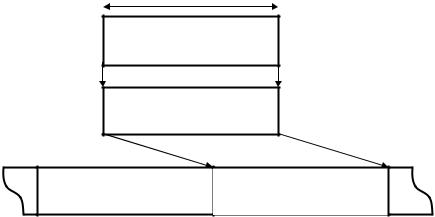

Самый простой подход в организации виртуальной памяти (см. рис. 5.1) состоит в том, что память строится банками (конст-

руктивные разделы памяти) или страницами (логические разде-

лы) и с помощью некоторого аппаратного или программного переключателя выбирается нужный раздел фиксированного (64 кБ) объема. Физический адрес команды или операнда в этом случае будет определяться по формуле:

Aфиз = Aпрог + Nстр Z ,

где Z — размер страницы в байтах.

Для организация расширенной памяти используется дополнительная физическая память, дополнительные разряды в адресной шине и некоторая программная система, управляющая аппаратным переключателем. Общий объем памяти при 16-разрядном переключателе может достигать очень большого размера: 6464К кБ. Этот подход легко реализуется и на аппаратном и на программном уровнях, но он не позволяет отдельной программе выделить объем больше 64 кБ без дополнительного аппаратнопрограммного механизма.

143

16 разрядов

Программный адрес

Aпрог

Переключатель

страниц

(N–1) стр |

N стр |

(N+1) стр |

Z= 64 кБ |

Z= 64 кБ |

Рис. 5.1 — Страничная организация памяти

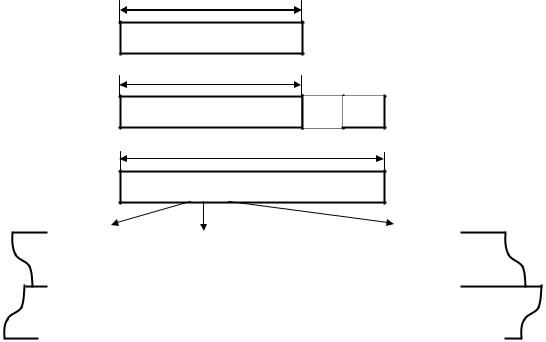

В современных машинах вместо переключателя страниц, обеспечивающего переключение памяти фиксированными по объему разделами, используются специальные базовые или сегментные регистры. Содержимое регистра определяет начало сегмента или раздела, выделенного программе (рис. 5.2). Адрес сегмента фактически задает смещение физического адреса относительно адреса, заданного в программе. Размер сегмента выделяется задаче программно, обычно операционной системой. Физический адрес определяется:

Aфиз = Aпрог + Aсегм K ,

где К — некоторый коэффициент, лежащий для различных семейств машин в пределах 4..64. Этот коэффициент определяет минимальное взаимное смещение сегментов. На рис. 13 в двух младших восьмеричных разрядах записаны 0, что эквивалентно

умножению адреса сегмента на 100(8) или 64(10).

Существование банков памяти по 64 кБ каждый означает деление памяти на конструктивные разделы, в то время как логические разделы — сегменты — могут иметь произвольный размер и не совпадать с конструктивными.

При дефиците оперативной памяти виртуальная память может использовать дисковое пространство, динамически считывая с диска необходимый фрагмент выполняемой программы или, наоборот, удаляя не используемую в данный момент часть программы в специальную область на жестком диске, которая называется областью свопинга (swap space). Этот процесс называется

144

свопинг (swapping) или подкачка — временное хранение активной задачи на жестком диске.

16 разрядов

Программный адрес

16 разрядов

Адрес сегмента |

0 |

0 |

24 разряда |

|

|

Физический адрес

|

(N–1) банк |

|

N банк |

• • • |

N+P) банк |

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

1 сегмент |

|

|

2 сегмент |

|

|

3 сегмент |

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 5.2 — Странично-сегментная организация виртуальной памяти

Виртуальная организация памяти позволяет существенно увеличить объем доступной программам памяти (реально — до десятков ГБайт). Таким образом, идея виртуальной памяти (в том смысле, который используется сейчас) позволяет расширить адресное пространство или просто заменить оперативную память более медленной и дешевой дисковой, причем это будет происходить «прозрачно» от прикладной программы.

Как уже говорилось, дисковая память несколько дешевле и медленнее оперативной. На сравнении быстродействия и среднего объема различных видов памяти основано понятие «иерархия памяти». На самом верху иерархической лестницы расположена сверхоперативная память — регистры процессора. Обращение к ним самое быстрое, т.к. они входят в состав процессора. Но количество их невелико — от одного до 128 аккумуляторов.

Следующий уровень — внутренний кэш объемом от 32 Б до 2 МБ. Это память без произвольного доступа, работа с ней происходит на аппаратной уровне. В ней хранятся наиболее часто