Материал: 4183

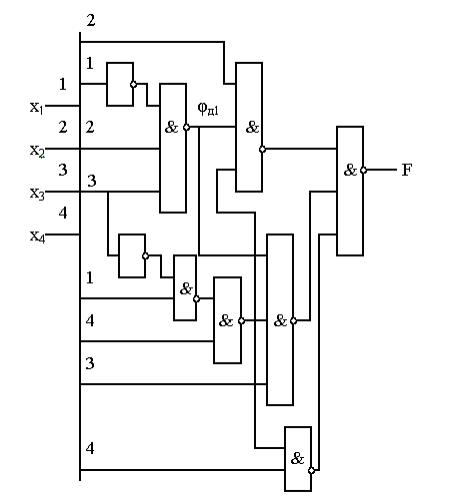

Рисунок 36 Многоярусная схема на элементах И-НЕ

Практическое задание. Выполнить проектирование методом допустимых конфигураций многоярусной схемы на элементах И-НЕ для булевых функций

Лабораторная работа 7 Проверка полноты простого функционального теста, построение тестового набора для не проверяемой неисправности

методом активизации одномерного пути

Теперь приступим к изучению свойств теста. Прежде всего нас интересует полнота проверки неисправностей. Это очень важное свойство. Обычно тесты, предлагаемые проектировщиками, не являются полными. Тест не показывает наличие в схеме неисправности, а она есть. Тогда пользователь начинает сам искать тестовые наборы, позволяющие определить наличие неисправности в схеме или даже позволяющие определить место неисправности. Промоделируем эту ситуацию. Пусть задан функциональный проверяющий тест, например, такой – 2 набора множества М1 и 2 набора множества Мо.

36

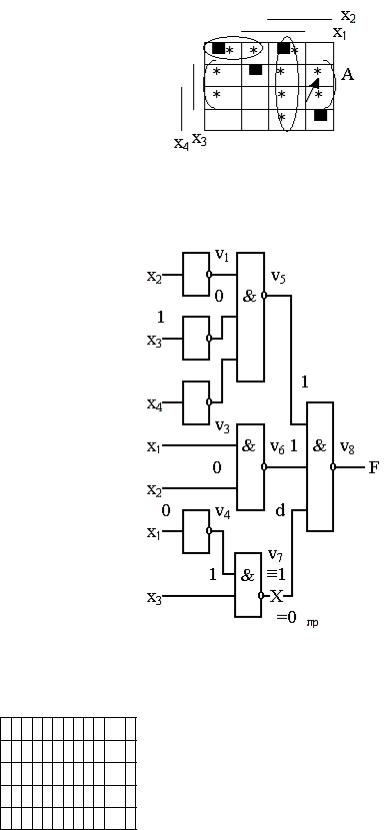

Рисунок 37. Булева функция и проверяющий тест проектировщика.

Например, пусть задан следующий тест, показанный на Рис. 43. Построим схему.

Рисунок 38 Схема с не обнаруживаемою неисправностью.

Проведем логическое моделирование схемы на этом тесте.

X1 х2 х3 х4 v1 v2 v3 v4 v5 v6 v7 v8

00001111011 |

1 |

11000110101 |

1 |

10101010111 |

0 |

01010101111 |

0 |

≡1 |

|

Обнаружена непроверяемая неисправность, на элементе v7 на всех тестовых наборах реализован сигнал 1, т. Е. даже если этот элемент будет находиться в неисправности 1, на функциональном тесте схема сработает верно.

Обнаружено место и тип неисправности, она не проверяема функциональным тестом. Существует метод построения теста для заданной

37

неисправности – метод активизации одномерного пути. Для метода должны быть заданы: схема, в ней указаны место и тип неисправности. Тест строится по схеме и на ней. Находим элемент v7, отмечаем его и записываем тип неисправности. Неисправность 1 проверяется исправным 0 на его выходе. Элемент реализует функцию И-НЕ, чтобы на его выходе появился сигнал 0 на его входы нужно подать 1 и 1, распространяем эти сигналы до входных полюсов схемы. Итак, переменная х1 = 0, переменная х3 = 1. если элемент исправен на его выходе сформируется сигнал 0, если он неисправен, то сформируется сигнал 1. Однако, выход элемента v7 не доступен для внешнего наблюдения. Обозначаем сигнал на этом выходе через d(do not known) и находим один из возможных путей к выходу схемы в целом. В данном случае путь всего один, через элемент v8. Этот элемент тоже реализует функцию И-НЕ. Чтобы сигнал d со входа сформировал сигнал d на выходе элемента v8 нужно на другие его входы подать сигналы 1. Путь сформирован, но сигналы 1 на входах элемента v8 не являются входными переменными схемы и нужно этот путь активизировать, т. Е. подобрать значения входных переменных, чтобы вызвать значения 1 на выходах элементов v6 и v5. Переменная х3 равна 1, значит на выходе элемента v2 значение равно 0, что определяет значение 1 на выходе элемента v5. И, наконец, переменная х1 равна 0, что определяет значение 1 на выходе v6.Путь активизирован, искомый тест таков:

х1х2х3х4F

0 х 1 х 1= dиспр

Метод активизации одномерного пути пригоден для произвольных схем из произвольных элементов. Например, схема следующая:

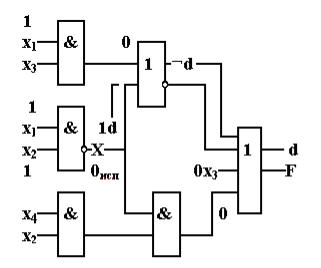

Рисунок 39 Схема для метода активизации одномерного пути на первом пути.

Итак, задана неисправность 1 на элементе И-НЕ, для ее проверки необходимо реализовать исправный 0 на этом полюсе, т.е. задать значения 1 входным переменным х1 и х2. На выходе элемента получили сигнал d. Его необходимо провести на выход схемы в целом, выбираем верхний путь.

38

Чтобы провести сигнал через элемент ИЛИ-НЕ на его второй вход нужно подать сигнал 0, тогда на его выходе появится сигнал d. Чтобы этот сигнал передать дальше, необходимо на входах выходного элемента сформировать сигналы 0. Тогда на выходе этого элемента появиться сигнал d. Прямой проход завершен. Нужно его активизировать, т. Е. подобрать значения входных сигналов схемы, чтобы сформировать требуемые сигналы на внутренних полюсах. Но это не возможно, т. К. сигнал 0, сформированный на полюсе х3 выходного элемента, одновременно поданный на входной полюс элемента v, формирует сигнал 1 на его выходном полюсе, что противоречит требуемому 0 для продвижения сигнала d через элемент v.

Попробуем провести сигнал d по второму возможному пути.

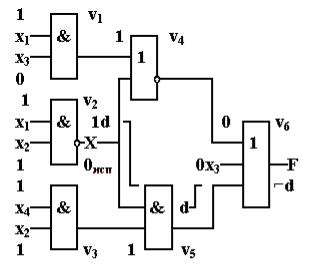

Рисунок 40. Схема с рассмотрением второго пути.

Пропуском сигнала d через элемент v5(И) является значение 1 на втором полюсе. Остается провести сигнал d через выходной элемент. Значения сигналов на двух других полюсах равны 0, на выходе схемы появилось значение d. Нужно выполнить активизацию сформированных прямым проходом сигналов. Значение 0 на выходе элемента v4 формируется значением 1 на выходе элемента v1(И-НЕ), которое в свою очередь формируется значением х3=0 на его входе. Значение 1 на входе элемента v5 формируется значением х4=1 на входе элемента v3(И). Активизация завершена.

Сформулируем метод активизации одномерного пути.

1.Заданы схема, место и тип неисправности.

2.Формируем путь к выходу схемы и проводим путь от места неисправности к выходу схемы, если таких путей несколько, то выбираем произвольно один, остальные запоминаем.

3.Строим проверяющий неисправность сигнал, противоположный заданному типу и выбираем входные воздействия, способные сформировать этот исправный сигнал на выходе заданного элемента.

4.Осуществляем прямой проход, осуществляя продвижение сигнала d с

места неисправности до выхода схемы по выбранному пути. Для

39

продвижения сигнала d через очередной элемент подбираем значения сигналов на остальных входах этого элемента с тем, чтобы его выход зависел только от сигнала d. Продвигаемся через все элементы выбранного пути к выходному элементу. Активизация пути завершена.

5.Теперь необходимо ее обеспечить. В процессе активизации были заданы конкретные значения сигналов на входах элементов схемы, не все они являются входными сигналами схемы. Нужно найти и согласовать с уже заданными значениями входов схемы с тем, чтобы обеспечить заданные значения сигналов во время прямого прохода.

6.Если возникли противоречия, то нужно выбрать другой путь и выполнить его активизацию.

Практическое задание. Построить произвольный функциональный проверяющий тест (2 набора множества М1 и два набора множества М0), провести логическое моделирование схемы для задания и выбрать одну из не проверяемых неисправностей и, наконец, для нее выполнить построение проверяющего теста методом активизации одномерного пути.

Лабораторная работа 8 Построение полного минимального теста схем

Цель занятия – изучение еще одного свойства схем – наличие неисправностей. Изучается классический метод Чегиса – Яблонского.

Теоретические положения и пример. Неисправности в схемах наиболее ожидаемый характер их работы.

Мы ограничимся характерными неисправностями – появлением тождественного 0 или 1 на входах и выходах всех элементов в схеме, более того ограничимся однократными неисправностями. Классический метод Чегиса и Яблонского основан на построении функций однократных неисправностей на всех наборах схемы, а затем на основе этих функций построение и решение таблицы покрытий с точностью хотя бы одного кратчайшего покрытия. Таким образом, удается построить минимальный тест

– множество входных наборов, проверяющих наличие хотя бы одной неисправности в схеме.

Мы немного усовершенствуем алгоритм, при построении таблицы функций неисправностей воспользуемся следующими утверждениями.

Утверждение 1. Неисправности 1 на входах элементе верхнего яруса схемы приводят к исчезновению интервала, поданного на этот вход.

Утверждение 2. Неисправности 1 на входах элементов второго уровня приводят к расширению интервала по переменной, поданной на этот вход.

Рассмотрим пример. Так как необходимо строить значения функций неисправностей на всех входных наборах, то ограничимся функцией трех переменных.

40