Материал: 3369

5 |

35 |

2 |

20 |

300 |

Дайте определение скважности и коэффици- |

|

|

|

|

|

ента заполнения импульсной последователь- |

|

|

|

|

|

ности. Приведите графики импульсной после- |

|

|

|

|

|

довательности, когда Т=20мс, aQ,=4 и Q2=5. |

|

|

|

|

|

|

6 |

40 |

6 |

10 |

350 |

Поясните, как изменяется период колебаний Т |

|

|

|

|

|

и частота f импульсов, если: а) увеличить дли- |

|

|

|

|

|

тельность импульса (tn=const); б) увеличить |

|

|

|

|

|

длительность паузы |

|

|

|

|

|

|

7 |

45 |

7 |

8 |

400 |

Укажите преимущества и недостатки |

|

|

|

|

|

двоичной системы счисления. |

|

|

|

|

|

|

8 |

50 |

8 |

14 |

450 |

Поясните, как различают цифровые устройст- |

|

|

|

|

|

ва по вводу и выводу информации. |

|

|

|

|

|

|

9 |

55 |

5 |

20 |

500 |

Приведите графики ввода информации в по- |

|

|

|

|

|

следовательной и параллельной и форме при |

|

|

|

|

|

числе входов, равном 2. |

10 |

60 |

7 |

15 |

550 |

Приведите график потенциального цифрового |

|

|

|

|

|

сигнала 10101101, представленного в по- |

|

|

|

|

|

следова тельной и параллельной форме. |

|

|

|

|

|

|

2. По заданной таблице истинности представить функцию в виде логического выражения. Форма представления функции – СДНФ.

Произвести минимизацию функции с помощью карт Вейча. Записать упрощенное, сокращенное выражение в форме ДНФ и составить логическую схему функции в базисе И, ИЛИ, НЕ.

|

Х1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

Аргументы |

Х2 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

Х3 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

11 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

F(Х) |

|

|

|

|

|

|

|

|

|

12 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

15 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

16 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

17

3. Произвести преобразование чисел из одной системы счисления в другую: десятичное число перевести в двоичную и шестнадцатеричную системы; двоичную систему счисления – в десятичную и шестнадцатеричную; шестнадцатеричную – в десятичную и двоичную.

№ |

Заданное число в системе счисления |

||

|

|

|

|

задачи |

десятичной |

двоичной |

шестнадцатеричной |

|

|

|

|

7 |

5 |

0010011 |

7 |

|

|

|

|

8 |

15 |

1000001 |

9 |

|

|

|

|

9 |

85 |

0101000 |

8 |

|

|

|

|

0 |

50 |

1100011 |

7 |

|

|

|

|

1 |

00 |

0100110 |

8 |

|

|

|

|

2 |

29 |

1101100 |

3 |

|

|

|

|

4. Перечислите и поясните основные параметры логических элементов (ЛЭ). Поясните, как можно повысить нагрузочную способность элемента ТТЛ. Приведите номера серий ИС, изготовленных по данной технологии.

5. Приведите схему эмиттерно-связанной логики (ЭСЛ) и укажите на ней состояние всех транзисторов при поступлении на вход уровней: вход 1 – U0, вход 2 и вход 3 - U1. Кратко поясните действие схемы.

6.Приведите схему эмиттерно-связанной логики (ЭСЛ) и укажите на ней состояние всех транзисторов при подаче на все входы напряжения U0. Кратко поясните действие схемы.

7.Приведите схемы логических элементов (ЛЭ) на МДП -транзисторах. Поясните их действие. Укажите достоинства подобных ЛЭ.

8.Дайте сравнительный анализ (укажите достоинства и недостатки) интегральных схем, имеющих следующие технологии изготовления: ТТЛ, ЭСЛ, И2Л, МДП, КМОП. Сведите данные в таблицу.

18

9. Укажите достоинства, приведите схему ЛЭ инжекционной логики (И2Л), поясните ее действие.

10. Поясните, как следует поступать с неиспользуемыми входами ИС, чтобы не нарушать их работоспособность.

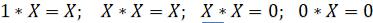

11. Приведите формулы, по которым можно определить при числе n аргументов число наборов их значений и число значений функций. Подсчитайте эти значения при n = 1, n = 2, n = 3. Приведите таблицу истинности логической операции Ии, пользуясь таблицей, докажите справедливость свойств конъюнкции:

12. Приведите таблицу истинности логической операции ИЛИ 13. Укажите назначение и применение шифраторов. Приведите схему

шифратора на элементах ИЛИ - НЕ, составьте таблицу истинности устройства. Кратко поясните работу схемы.

14.Укажите назначение и область применения дешифратора.

15.Поясните возможность расширения разрядности дешифратора до №=255, используя ИМС. Укажите назначение входа V.

16.Поясните назначение коммутатора, выполняющего роль мультиплексора. Приведите его условное графическое обозначение, поясните назначение всех выводов схемы. Составьте схему мультиплексора, подключающего один из входов До - Дз к выходу У. Поясните, как выбирается чис¬ло адресных входов и укажите значения переменных на входах, для подключения входов Д0 - Дз к выходу.

17.Поясните, какое устройство обеспечивает подключение одного из входов к одному выходу. Приведите схему, позволяющую подключить 16 входов к выходу и укажите на ней значения логических уровней на соответствующих адресных входах, если требуется подключить вход Д9 к выходу устройства.

18.Приведите условное графическое обозначение демультиплексора, поясните назначение всех его выводов. Укажите возможность наращивания разрядности демультиплексора до 16 выходов. Кратко поясните построение подобной схемы.

19.Поясните назначение компаратора. Кратко поясните действие схемы.

20.Укажите назначение и область использования триггеров. Перечислите типы интегральных триггеров, поясните назначение входов всех типов триггеров.

19

21. Приведите схему асинхронного RS - триггера, построенного на элементах И - НЕ, поясните его действие. Приведите его условное графическое изображение и таблицу истинности.

22. Приведите схему тактируемого RS – триггера, поясните его действие, используя временные диаграммы. Приведите его условное графическое обозначение.

23. Приведите схему тактируемого RS-триггера, поясните его действие, используя временные диаграммы. Приведите его условное графическое обозначение.

24. Приведите схему двухступенчатого синхронного RS -триггера, поясните его действие. Приведите его условное графическое обозначение.

Укажите различие в действии одноступенчатого и двухступенчатого (с динамическим С - входом) триггеров.

25. Приведите схему триггера со счетным запуском (Т-триггера). Поясните его построение, действие. Приведите таблицу истинности и условное графическое обозначение.

26. Приведите схему триггера задержки (D - триггера). Поясните его действие, используя временные диаграммы. Приведите таблицу истинности и его условное графическое обозначение.

27. Приведите схему двухступенчатого Д - триггера, поясните его функционирование. Приведите условное графическое обозначение триггера.

28. Приведите логическую структуру и таблицу переходов для j к - триггера. Поясните работу схемы при следующих условиях:

а) лог. 1 подается на входы J и С, на вход К подается лог. 0. Исходное состояние триггера Q0 = 0;

б) лог. 1 подается на входы К и С, на вход J подается лог. 0. Исходное состояние триггера Q0 = 0.

Приведите условное графическое обозначение триггера.

Условия задач и тексты вопросов переписываются полностью, задачи должны снабжаться текстами пояснений к их решению. В расчетной части задачи следует вначале приводить формулы в общем виде, подставить цифровые значения, записать результат с единицами измерения.

Схемы следует вычерчивать карандашом, с применением чертежных инструментов. Элементы схем должны приводиться с соблюдением требований ГОСТ.

20

В конце работы следует указать перечень использованной литературы, поставить дату выполнения работы и подпись.

Формы записи логических функций:

1.совершенная дизъюнктивная нормальная форма (СДНФ);

2.совершенная конъюнктивная нормальная форма (СКНФ). СДНФ представляет собой логическую сумму простых конъюнкций

(произведений) аргументов, на которых функция принимает значение, равное 1. Для записи функции в виде логического выражения с использованием за-

данной таблицы истинности необходимо:

1.записать простые конъюнкции аргументов. При этом аргумент записывается без инверсии, если в таблице он имеет значение 1, и с инверсией, если в таблице он имеет значение 0;

2.составляется логическая сумма (дизъюнкция) простых конъюнкций. Форму записи называют совершенной, если каждый член логического

3.выражения содержит все аргументы или их инверсии. Минимизация состоит в получении самой короткой формы записи логи-

ческой функции, реализация которой приведет к логической схеме с наименьшим числом логических элементов, что экономит элементную базу, снижает стоимость устройства при обеспечении заданного уровня надежности.

Все методы минимизации основаны на законах алгебры логики. Чаще других используют два метода: метод Квайна; метод Вейча, которым следует воспользоваться для выполнения задания.

Задания №1-37

1.Укажите назначение сумматоров, их условное графическое обозначение (УГО). Приведите структурную схему сумматора последовательного действия, поясните ее. Укажите назначение D - триггера. Дайте оценку схемы рассмотренного сумматора. Поясните, как можно ускорить процесс сложения чисел. Приведите необходимую схему.

2.Приведите схему рис. 8.44 [2], укажите ее назначение, перечислите использованные в схеме логические элементы. Обозначьте во всех точках схемы значения логических переменных для случая: А=1, В=1. Дайте краткие пояснения. Укажите, с помощью какой схемы можно производить сложение не только вида А+В, но и учитывать перенос из предыдущего разряда. Приведите подобную структурную схему.

3-4 Составьте таблицу истинности полного одноразрядного сумматора. Составьте уравнения в форме СДНФ и схему в базисе И, ИЛИ, НЕ. Укажите