Материал: Захаров, Сайфутдинов - Вычислительная техника

полученные после выполнения всей программы вычислений, передаются на устройства вывода (УВыв) информации. В качестве УВыв могут использоваться экран дисплея, принтер, графопостроитель и др.

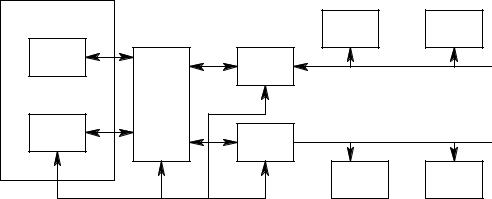

Вкомпьютерах третьего поколения произошло усложнение структуры за счет разделения процессов ввода-вывода информации и процесса ее обработки (рис. 6.3).

Вструктуре имеются устройства: управления обмена информацией (УВВ), каналы ввода-вывода (КВВ). КВВ получили наибольшее распространение применительно к большим ЭВМ. Здесь наметилась тенденция к децентрализации управления и параллельной работе отдельных устройств, что позволило повысить быстродействие компьютеров.

Процессор |

УВВ ... |

УВВ |

АЛУ |

КВВ |

|

|

|

|

|

ОЗУ |

|

УУ |

КВВ |

|

|

|

|

|

ВЗУ ... |

ВЗУ |

Рис. 6.3. Структурная схема компьютера третьего поколения

Среди каналов ввода-вывода выделяются мультиплексные каналы, способные обслуживать большое количество медленно работающих устройств ввода-вывода, и селекторные каналы, обслуживающие в монопольных режимах скоростные внешние запоминающиеустройства (ВЗУ).

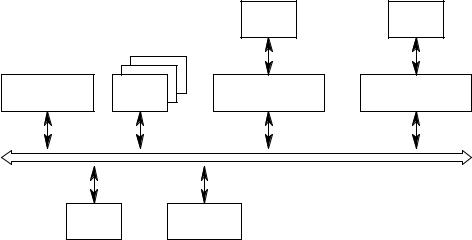

В ПЭВМ, относящихся к компьютерам четвертого поколения, произошло дальнейшее изменение структуры (рис. 6.4).

Соединение всех устройств обеспечивается с помощью общей шины, представляющей собой линии передачи данных, адресов, сигналов управления и питания. Единая система аппаратурных соединений значительно упростила структуру, сделав ее еще более децентрализованной. Все передачи данных по шине осуществляются под управлением сервисных программ.

121

|

|

ВУ |

... |

ВУ |

|

|

|

|

|

Процессор |

ОП |

Контроллер ... |

Контроллер |

|

Общая шина

КПД Таймер

Рис. 6.4. Структурная схема ПЭВМ

Ядро ПЭВМ образуют процессор и основная память, состоящая из ОЗУ и постоянного запоминающего устройства (ПЗУ). ПЗУ предназначено для постоянного хранения программ управления. Подключение всех внешних устройств (ВУ): дисплея, клавиатуры, внешних ЗУ и др., обеспечивается через соответствующие адаптеры — согласователи скоростей работы сопрягаемых устройств или контроллеры — специальные устройства управления периферийной аппаратурой. Контроллеры в ПЭВМ играют роль каналов ввода-вывода. В качестве особых устройств следует выделить таймер — устройство измерения времени и контроллер прямого доступа к памяти (КПД) — устройство, обеспечивающее доступ к основной памяти, минуя процессор.

Все приведенные структуры не выходят за пределы классической структуры фон Неймана и их объединяют следующие общие принципы построения:

структура памяти;

способы доступа к памяти и внешним устройствам;

система и форматы команд;

организация интерфейса;

возможность изменения конфигурации компьютера.

122

6.4. Центральный процессор

Процессор – устройство, непосредственно осуществляющее обработку информации и выполняющее функции управления работой ЭВМ в соответствии с заданной программой.

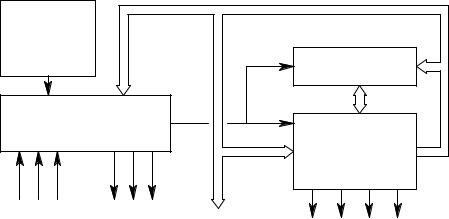

Процессор состоит из арифметико-логического устройства (АЛУ), устройства управления (УУ) и блока внутренних регистров (БВР) (рис. 6.5). Узлы соединены шинами, по которым передаются адреса – шина адреса (ША), данные – шина данных (ШД) и сигналы управления – шина управления (ШУ).

Арифметико-логическое устройство (АЛУ) предназначено для выполнения различных арифметических и логических операций над словами (операндами). Арифметические операции АЛУ: сложение, вычитание, умножение, деление кодов двоичных чисел с фиксированной и плавающей запятой в двоичной (шестнадцатеричной) и двоично-десятичной СС.

Генератор |

данных |

|

тактовых |

|

|

импульсов |

АЛУ |

|

|

шина |

|

Устройство |

|

|

Внутренняя |

|

|

управления |

Блок |

|

|

внутренних |

|

|

регистров |

|

|

|

|

Шина управления |

Шина данных |

|

внешняя |

внешняя |

Шина адреса |

Рис. 6.5. Структура процессора |

||

В АЛУ выполняются операции: нормализации числа, сдвига арифметического (без сдвига кода знака) и логического (сдвиг кода всего числа со знаком) и др. Кроме основных логических операций дизъюнкции (ИЛИ), конъюнкции (И) и инверсии (НЕ), в АЛУ предусматриваются другие операции, необходимые для логической обработки алфавитно-цифровой информации: сравнение слов на равенство, сортировка их по признакам и т. п. В отличие от арифметических операций, логические операции

123

являются поразрядными: они выполняются одновременно над одноименными разрядами слов независимо от значений соседних разрядов.

Классификация АЛУ

Все существующие АЛУ можно разбить на следующие классы:

1.По способу представления чисел различают АЛУ, в которых двоичные, шестнадцатеричные или (и) десятичные числа представляются в формах с фиксированной, плавающей или (и) естественной запятой.

2.По последовательности обработки разрядов операндов АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды поступают последовательным кодом и их обработка (например, суммирование) производится разряд за разрядом последовательно во времени. В параллельных АЛУ операнды поступают параллельным кодом и их разряды обрабатываются одновременно.

3.По принципам построения основных (базовых) блоков различают АЛУ с комбинационным и накапливающим сумматором, АЛУ на однородных вычислительных средах (матричные), АЛУ с табличным выполнением операций и др.

4.По характеру использования блоков различают АЛУ со специализированными блоками (блочные) и АЛУ с многофункциональными блоками. В блочных АЛУ для выполнения каждой операции или каждой группы однотипных операций предусмотрены отдельные блоки. Например, блоки суммирования двоичных и десятичных чисел с фиксированной и плавающей точкой, блок умножения, блок деления, блок логических операций и другие. Такая специализация блоков сама по себе, а также возможность одновременной работы нескольких блоков, существенно увеличивает быстродействие АЛУ.

В многофункциональных АЛУ одни и те же узлы и блоки используются для выполнения различных операций. При настройке на конкретную операцию производится коммутация этих узлов в требуемую схему. Многофункциональные АЛУ более компактны, но их быстродействие ниже, чем у блочных АЛУ ввиду меньшей специализации и дополнительных задержек в узлах коммутации.

Основу АЛУ составляет операционный блок, на вход которого поступают данные (операнды). В операционном блоке над поступающими операндами производятся все операции, предусмотренные назначением АЛУ. Устройство управления вырабатывает последовательность сигналов управления под воздействием генератора

124

тактовых импульсов. Каждый сигнал управления поступает в операционный блок в определенный тактовый интервал и инициирует определенную микрооперацию над операндами (прием в регистр, сдвиг, инвертирование и т. п.). Каждая операция над операндами в АЛУ представляет собой определенную последовательность микроопераций.

Требуемая операция над операндами в АЛУ задается кодом операции. Этот код вызывает формирование в устройстве управления соответствующей последовательности сигналов управления.

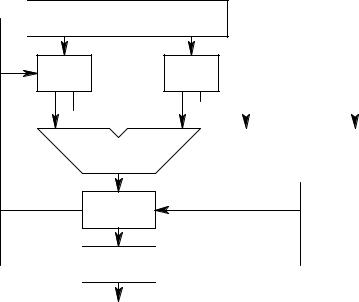

Состав операционного блока определяется его предназначением — перечнем операций, формами представления операндов. Для выполнения операций над операндами в состав АЛУ входят (рис. 6.6): входные регистры А и В (РгА, РгВ) для приема операндов, n-разрядный сумматор (СМ), регистры для приема и хранения промежуточного и окончательного результата операции Pг S и Рг вых, блок логических операций – для формирования сигналов оповещения о промежуточных и окончательных значениях операндов (положительный или отрицательный результат, равен нулю или переполнение разрядной сетки и др.). Логические операции выполняются в регистрах с соответствующими логическими схемами или в блоке логических операций. Схема соединения узлов, указанных на рис. 6.6, меняется в зависимости от выполняемой операции.

Блок внутренних регистров

Блок внутренних регистров

Рг А |

Рг В |

|

|

|

|

|

|

|

|

|

|

СМ |

|

Блок логических |

||

|

операций |

|||

|

|

|

||

|

|

|

|

|

Рг S

Рг вых

Рг вых  Результат

Результат

Рис. 6.6. Состав многофункционального АЛУ

125

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |