Материал: Счётчики

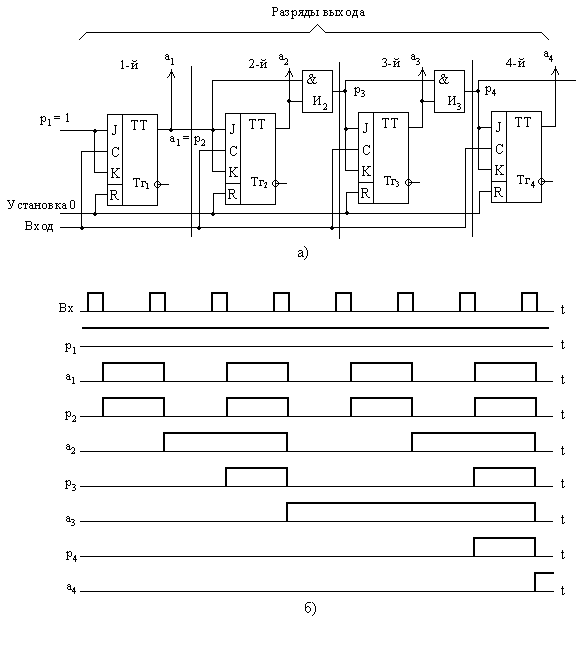

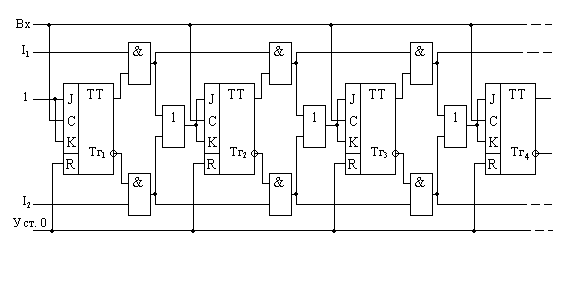

В данной схеме устранен недостаток предыдущей схемы счетчика. Отрицательным фронтом входного импульса одновременно переключаются те триггеры, на входы которых в данный момент поступает сигнал переноса pi = l. Таким образом может быть обеспечено более высокое быстродействие, чем в предыдущей схеме.

Фактором, ограничивающим быстродействие данной схемы счетчика, является последовательное формирование переносов.

рис 8.43

Формирование переноса в i-м разряде начинается с момента завершения формирования переноса в предыдущем (i - 1)-м разряде и поступления сформированного переноса из (i - 1)-го в i-й разряд. При этом i-й разряд выдает перенос в следующий (i + l)-й разряд с задержкой относительно момента поступления переноса в i-й разряд. Эта задержка связана с задержкой распространения сигнала в элементе Иi. Таким образом, процесс продвижения переносов вдоль разрядов в счетчике последовательный (из разряда в разряд) и в каждом разряде имеет место задержка. Общее время задержки распространения переносов xпер определяется задержкой в одном разряде xпер1 и числом разрядов, через которые проходят переносы.

В наихудшем случае, когда переносы последовательно проходят через все разряды счетчика (начиная со второго), общая задержка xпер = xпер1(n - 1).

После переключения триггеров под действием предыдущего импульса, поданного на вход счетчика, только через время xпер на входах триггеров оказываются сформированными переносы и может быть подан очередной импульс на вход счетчика. Таким образом, временем xпер ограничивается минимальный временной интервал между входными импульсами, и xпер ограничивает максимальную частоту подачи импульсов на вход, т. е. быстродействие счетчика.

В тех случаях, когда необходимо обеспечить высокое быстродействие, применяют меры к уменьшению xпер. Уменьшение xпер может быть обеспечено применением в цепи передачи переносов элементов И с малым временем задержки распространения сигнала, а также использованием в счетчике последовательно- параллельной цепи передачи переносов. Рассмотрим принцип организации такой последовательно-параллельной передачи переносов.

Запишем логические выражения, по которым формируются переносы в разрядах счетчика

p3 = a2 . p2; p4 = а3 . p3; p5 = a4 . p4; p6 = a5 . p5; ...

Подставляя выражения р3, р5, ... в выражения p4, р6, ... получаем

p3 = а2 . p2; p4 = а3 . a2 . p2; p5 = a4 . p4; p6 = a5 . a4 . p4; ...

При использовании этих выражений перенос p2 выхода первого разряда одновременно поступает во второй и третий разряды, участвуя в формировании р3 и p4. Аналогично р4 передается одновременно в четвертый и пятый разряды и участвует в формировании р5 и p6 и т. д.

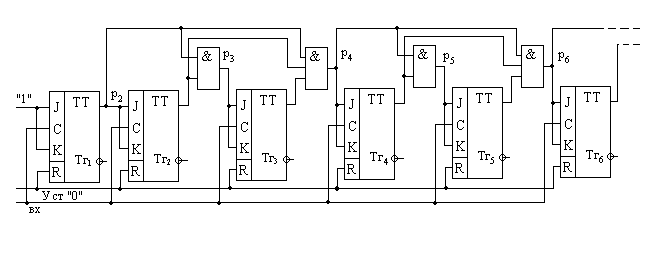

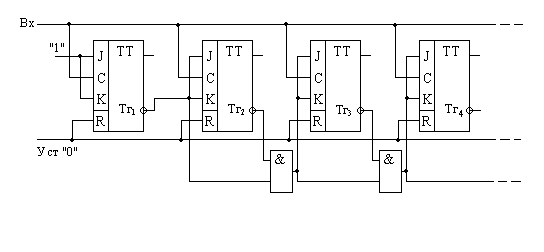

Очевидно, при этом примерно вдвое уменьшается число разрядов, через которые переносы передаются последовательно, уменьшается xпер. На рис. 44 приведена схема счетчика, в которой цепь передачи переносов построена в соответствии с приведенными выше логическими выражениями.

Развивая этот принцип, можно записать следующие логические выражения для переносов:

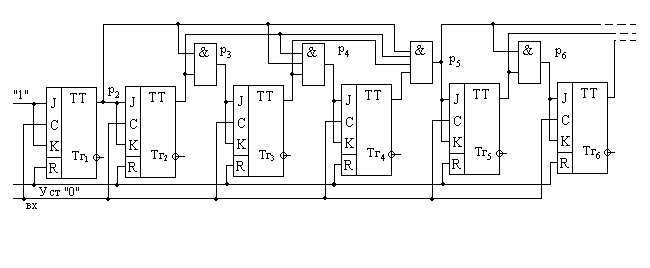

p3 = a2 . p2; p4 = а3 . a2 . p3; p5 = a4 . a3 . a2 . p2;

p6 = a5 . p5; p7 = a6 . a5 . p5; p8 = a7 . a6 . a5 . p5, ...

рис 8.44

рис 8.45

Схема счетчика на рис. 45 построена с использованием этих выражений. Такой счетчик обеспечивает еще большее снижение xпер.

Следует иметь в виду, что использование рассмотренного принципа повышения быстродействия вызывает усложнение схемы счетчика, связанное с использованием в цепи передачи переносов элементов И с большим числом входов.

Вычитающий и реверсивный счетчики.

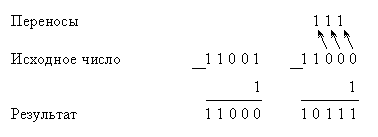

В вычитающем счетчике поступление на вход очередной лог. 1 (очередного импульса) вызывает уменьшение хранившегося в счетчике числа на единицу. Покажем примеры такого вычитания единицы:

Из первого примера видно, что если в младшем разряде числа содержится 1, то получающееся в результате вычитания 1 число отличается от исходного лишь в младшем разряде.

Таблица 8.22 |

|||

ai |

pi |

ci |

pi+1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

Если в младшем разряде числа содержится 0, то процесс вычитания сопровождается возникновением переносов. В отличие от операции суммирования, в которой перенос прибавляется в разряд, в который он поступает, в операции вычитания перенос имеет смысл заема из следующего, более старшего разряда и вычитается из этого разряда. Последовательная передача таких заемов из разряда в разряд продолжается до тех пор, пока в очередном разряде, в который передается заем, не обнаруживается 1.

Так, во втором из приведенных выше примеров такая 1 обнаруживается в четвертом разряде. В результате заема этой 1 в четвертом разряде образуется 0, а занятая из этого разряда 1 передается в третий разряд, где она имеет уже значение 2. Из этих двух единиц в третьем разряде остается одна, а другая передается во второй разряд, где она также приобретает значение 2 и т. д.

Таким образом, в результате вычитания часть числа левее первого из разрядов, содержащих 1, остается неименной, цифры остальных разрядов инвертируются.

![]()

Функционирование i-го разряда счетчика при выполнении операции вычитания единицы представлено в табл. 8.22. Из этой таблицы истинности следуют логические выражения:

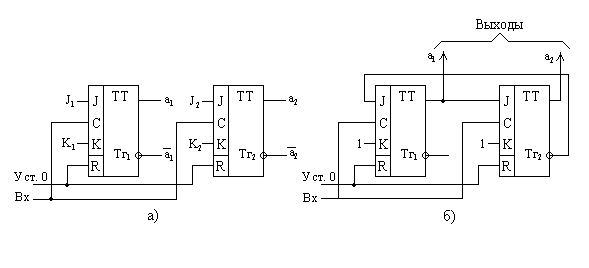

рис 8.47

рис 8.46

Цифры разрядов ci определяются тем же логическим выражением, что и в суммирующем счетчике. Следовательно, как и в суммирующем счетчике, перенос должен подаваться на счетный вход, образованный соединением информационных входов J и K триггера. Отличие выражения pi+l (по сравнению с соответствующим выражением суммирующего счетчика) состоит в том, что вместо ai использовано i. Таким образом, в вычитающем счетчике на элементы И, формирующие переносы, подаются сигналы с инверсных выходов триггеров.

На рис. 8.46 показана схема вычитающего счетчика с последовательной передачей переносов. Для повышения скорости работы счетчика могут быть использованы последовательно-параллельные цепи передачи переносов. Вычитающий счетчик, как и суммирующий, имеет период циклической работы, равный 2n импульсов.

Реверсивный счетчик - счетчик, допускающий в процессе работы переключение из режима суммирования в режим вычитания, и наоборот. На рис. 8.47 приведена схема такого счетчика. В ней предусмотрены две цепи передачи переносов, одна из которых соответствует схеме суммирующего счетчика, другая - схеме вычитающего счетчика. Управляющие сигналы Il и I2 включают в работу одну или другую цепь.

При Il = l и I2 = 0 оказывается закрытым элемент И2 и, следовательно, отключена цепь передачи переносов режима вычитания. Счетчик работает в режиме суммирования. При Il = 0 и I2 = 1 закрыт элемент И1 и отключена, таким образом, цепь передами переносов режима суммирования, счетчик работает в режиме вычитания.

Счетчик с периодом работы, не выражаемый целой степенью двух.

Пусть счетчик должен иметь период циклической работы, равный N, причем N не представляется целой степенью двух. Необходимое число триггеров определяется как минимальное n, удовлетворяющее неравенству 2n > N.

Счетчик с таким числом триггеров может иметь период 2n, больший требуемого N. Поэтому после установления в счетчике числа N - 1 необходимо в следующем такте работы обеспечивать сброс счетчика в нулевое состояние.

рис 8.48

Покажем метод синтеза такого счетчика. Пусть требуется синтезировать счетчик с периодом N = 3. Число триггеров n = 2 (это минимальное значение, удовлетворяющее неравенству 2n > N). На рис. 8.48,а представлена незаконченная схема счетчика без указания способа включения информационных входов триггеров J1, К1 и J2, К2.

Рассмотрим метод, позволяющий определить, каким образом должны включаться информационные входы триггеров. Под действием входных импульсов счетчик переходит из одного состояния (с одной комбинацией состояний триггеров) в другое (с другой комбинацией состояний триггеров). Комбинация состояний триггеров определяет двоичное число, значение которого при переходе счетчика в новое состояние увеличивается на единицу или устанавливается равным нулю после достижения максимального значения N - l. Такие переходы счетчика с периодом цикла N = 2 показаны в табл. 8.23.

Переход счетчика в новое состояние связан с переключением триггеров. Для перевода триггеров в требуемые состояния необходимы на его входах определенные логические уровни. В табл. 8.24 показаны все возможные переходы состояния триггера и требуемые для этих переходов логические уровни на входах J и K. Знак “-” означает, что логический уровень на входе может быть произвольным (лог. 0 или 1). Пользуясь этой таблицей, легко построить таблицы истинности для входов J и K всех триггеров счетчика. При этом логические уровни на входах J и K являются функциями текущего состояния и на картах Вейча (табл. 8.25) под а2 и a1 понимается состояние триггеров перед поступлением на вход счетчика очередного импульса.

Пусть к моменту подачи импульса на вход счетчика триггеры находились в состоянии a2 = 0, al = 0. Под действием входного импульса должно быть обеспечено новое состояние a2 = 0, al = l.

Таблица 8.23 |

|

Таблица 8.24 |

||||

Номер входного импульса |

Состояние триггеров |

|||

текущее |

следующее |

|||

a2 |

a1 |

a2 |

a1 |

|

1 |

0 |

0 |

0 |

1 |

2 |

0 |

1 |

1 |

0 |

3 |

1 |

0 |

0 |

0 |

4 |

0 |

0 |

0 |

1 |

... |

... |

... |

... |

... |