Материал: Программное обеспечение модуля управления и отладки комплекса систем железнодорожной автоматики

Программное обеспечение модуля управления и отладки комплекса систем железнодорожной автоматики

СОДЕРЖАНИЕ

ВВЕДЕНИЕ

. НАЗНАЧЕНИЕ И ОБЛАСТЬ ПРИМЕНЕНИЯ КОМПЛЕКСА КИИБ

. РАЗРАБОТКА ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ МОДУЛЯ УПРАВЛЕНИЯ И ОТЛАДКИ

.1 Форма управления функционированием ПО - MainView

.2 Форма просмотра памяти данных устройства - Form_view

.3 Форма просмотра энергонезависимой памяти устройства - Form_eeprom

.4 Форма просмотра памяти программ устройства - Form_prog

.5 Форма выборочного просмотра памяти данных устройства - Form_watch

.6 Форма отображения состояния выводов устройства - Form_pins

.7 Форма внесения ошибок в работу устройства - Form_mistakes

.8 Форма «Об авторе» - Form_author

. ТЕСТИРОВАНИЕ МОДЕЛИ PIC

.1 Тестирование системы команд

.2 Тестирование периферийных устройств

ЗАКЛЮЧЕНИЕ

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

ПРИЛОЖЕНИЕ

ВВЕДЕНИЕ

Создание микропроцессорных и компьютерных СЖАТ, неразрывно связано с совершенствованием и развитием методов обеспечения требуемого уровня их безопасности и надежности. Основным методом проверки работоспособности и оценки надежности и безопасности таких систем являются испытания на безопасность функционирования.

Общей целью испытаний является обеспечение заданного уровня безопасности и надежности. Испытания должны проводиться на всех этапах создания систем. При этом неограниченное увеличение числа контрольно-испытательных работ не обеспечивает роста надежности и безопасности СЖАТ. Вследствие этого вся совокупность испытаний требует оптимизации, определения оптимального сочетания видов испытаний, их объема, количества и места в ходе технологических процессов проектирования и разработки СЖАТ, исходя из необходимости обеспечения требуемой безопасности, надежности, стоимости, длительности цикла изготовления и других факторов.

Испытания на функциональную безопасность представляют собой комплекс мероприятий по подтверждению количественных и качественных показателей безопасности функционирования в соответствии с заявленным разработчиком системы уровнем обеспечения безопасности.

Целью имитационных испытаний на безопасность функционирования является подтверждение того, что испытываемое устройство или система при возникновении заданного класса неисправностей аппаратных и программных средств, отказах внешних датчиков и неправильных действиях человека-оператора не формирует сигналы управления, нарушающие условия безопасности движения поездов.

Контролируемые испытания микроэлектронных схем с внесением отказов в работу элементов на аппаратном уровне требуют значительных материальных и временных затрат на имитацию отказов и их устранение. Поэтому испытания на имитационных моделях являются наиболее приемлемым вариантом как по затратам, так и по удобству обработки результатов и скорости проведения испытаний.

Для решения данных проблем при проведении испытаний программно-технических средств ЖАТ на безопасность функционирования в испытательной лаборатории «Безопасность и ЭМС технических средств» Белорусского государственного университета транспорта разработан «Комплекс для проведения имитационных испытаний микропроцессорных систем железнодорожной автоматики на функциональную безопасность» (КИИБ).

Комплекс аппаратно-программных средств КИИБ предназначен для проведения ускоренных имитационных испытаний на функциональную безопасность в соответствии с IEC 61508, EN 50126, ОСТ 32.146 микропроцессорных систем управления ответственными технологическими процессами, в том числе систем управления движения поездов.

Комплекс успешно применяется в испытательной лаборатории «Безопасность и ЭМС технических средств» в течение пяти последних лет. Имеется положительный опыт испытаний устройств и систем на базе микроконтроллеров Microchip, Atmel, цифровых сигнальных процессоров ADSP и др., в том числе многопроцессорных систем. Применение КИИБ при экспертизе и испытаниях позволило обнаружить ряд неисправностей, приводящих к опасному отказу устройства в целом. Некоторые из них, например отказы в микропроцессорной системе ССС-200-60, не были обнаружены при использовании других методов экспертизы и испытаний.

Тем не менее, данная версия КИИБ имеет ряд недостатков, среди которых отсутствие графической оболочки и работа на устаревшей платформе (библиотеки VCL). Главным недостатком КИИБ является проблемный механизм расширения базы моделей микроконтроллеров, что обусловлено внутренней структурой комплекса.

Исходя из сказанного выше, можно сделать вывод о необходимости создания универсального программного продукта способного моделировать работу микроэлектронных устройств и их взаимодействия между собой при внесении различных отказов или сбоев в работу этих устройств.

1. НАЗНАЧЕНИЕ И ОБЛАСТЬ ПРИМЕНЕНИЯ КОМПЛЕКСА КИИБ

При сегодняшнем уровне развития IT-индустрии такие устройства, как микроконтроллеры, широко используются во многих областях техники. В новейших системах управления они являются одними из самых важных элементов. Современные микроконтроллеры достаточно дешевы и надежны, системы управления, построенные на основе микроконтроллеров, используются даже в отраслях, критичных к безопасности, таких, как железнодорожный транспорт. Поэтому для микропроцессорных систем железнодорожной автоматики проводится анализ на функциональную безопасность, целью которого является доказательство безопасности функционирования системы при возникновении отказов в структуре микроконтроллеров.

Основными особенностями отказов в программируемых элементах являются:

· взаимная зависимость аппаратных и программных средств, что приводит к тому, что один и тот же отказ проявляется по-разному в зависимости от загруженного программного обеспечения. Причем характер искажений, внесенных отказом в алгоритм работы микроконтроллера, может быть очень сложным по причине многократного использования отказавших аппаратных ресурсов программным обеспечением. Это значительно затрудняет анализ и увеличивает затраты на доказательство безопасности.

· зависимость результата отказа от типа исследуемого микроконтроллера, так как на функционирование программного обеспечения после отказа оказывают влияние такие характеристики микроконтроллера, как его архитектура и методы обработки информации внутри БИС. Поэтому при переносе программного обеспечения на другую элементную базу необходимы повторные испытания.

· большое количество учитываемых отказов, что требует автоматизации процесса тестирования микроконтроллера.

На основании данных факторов возникла проблема быстрого и качественного исследования влияния отказов микроконтроллеров на поведение систем управления. Программное обеспечение, предоставляемое разработчиками микроконтроллеров для отладки программ, не позволяет исследовать поведение микроконтроллера при отказе элементов его аппаратной части, что очень важно для исследований систем, критичных к безопасности.

Для анализа на безопасность микропроцессорных систем управления в испытательной лаборатории «Безопасность и ЭМС технических средств» Белорусского государственного университета транспорта была разработана новая версия «Комплекса для проведения имитационных испытаний микропроцессорных систем (МПС) железнодорожной автоматики на функциональную безопасность» КИИБ, в которой устранены недостатки предыдущей версии. Структурная схема КИИБ 4.0 представлена на рисунке 1.1.

КИИБ позволяет контролировать:

· наличие одиночных и кратных неисправностей технических средств, приводящих к нарушению функциональной безопасности системы;

· наличие ошибок программных средств, приводящих к нарушению функциональной безопасности системы;

· устойчивость функционирования при воздействии электромагнитных помех и при искажениях входных сигналов;

· уровень обнаружения отказов и сбоев заданной кратности средствами контроля и диагностики,

· возможность накопления отказов заданной кратности во внутренней структуре;

· тип искажения вычислительного процесса при наличии отказов технических средств.

С помощью КИИБ можно проводить:

· функциональные испытания МПС (проверка полноты и корректности выполнения основных функций);

· испытания на функциональную безопасность технологических алгоритмов, реализованных программным способом;

· испытания на функциональную безопасность программного обеспечения МПС;

· испытания на функциональную

безопасность МПС.

Блок загрузки выполняет подготовку работы системы моделирования и тактирование работы устройств. Непосредственно после запуска этого блока производится загрузка файлов модели, конфигурации и программ, в соответствии с которыми блоком формируются модели устройств.

Блок коммутации и протоколирования предназначен для передачи информации между элементами комплекса и создания протокола обмена сигналами между устройствами в виде файла *.stl.

Блок подачи входных сигналов подключается к системе как обычное устройство. Он предназначен для генерации аналоговых и цифровых сигналов, которые могут быть переданы на любые устройства в зависимости от конфигурации внутренних соединений устройств.

Блок отладки модели позволяет отслеживать общее состояние одного выбранного устройства с помощью разработанных средств визуализации, а также производить управление работой устройства с помощью внешних воздействий.

Блок автоматического тестирования предназначен для внесения в испытываемые устройства отказов и сбоев в соответствии с заданной программой испытаний. В соответствие с этой загруженной программой данный модуль управляет работой всех участвующих в моделировании устройств.

Виды отказов и сбоев каждого испытываемого устройства, а также поведение данного устройства при возникновении неисправностей реализуются при разработке соответствующих моделей. Программа испытаний, включающая перечень вносимых неисправностей, их последовательность имитации и кратность, содержится во внешнем файле. Такая организация комплекса позволяет обеспечить высокую скорость моделирования, гибкость, возможность параллельного проведения испытаний на нескольких компьютерах, объединенных в локальную сеть.

Разработанная структура для новой версии КИИБ позволяет устранить такие недостатки предыдущей версии, как отсутствие средств визуализации и узкая специализация используемых моделей.

2. РАЗРАБОТКА ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ МОДУЛЯ УПРАВЛЕНИЯ И ОТЛАДКИ

Для удобства анализа разработанное программное обеспечение удобно разбить на структурные части, каждая из которых выполняет уникальную функциональность. Каждую из таких структурных частей представляет разработанная VCL-форма и набор функций, характеризующих ее работу.

Общую структуру ПО можно представить следующим образом:

· Форма управления функционированием ПО (MainView) - главная форма, с ее помощью можно управлять работой остальных перечисленных ниже форм;

· Форма просмотра памяти данных устройства (Form_view);

· Форма просмотра энергонезависимой памяти устройства (Form_eeprom);

· Форма просмотра памяти программ устройства (Form_prog);

· Форма выборочного просмотра памяти данных устройства (Form_watch);

· Форма отображения состояния выводов устройства (Form_pins);

· Форма внесения ошибок в работу устройства (Form_mistakes);

· Форма «Об авторе» (Form_author);

2.1 Форма управления функционированием ПО - MainView

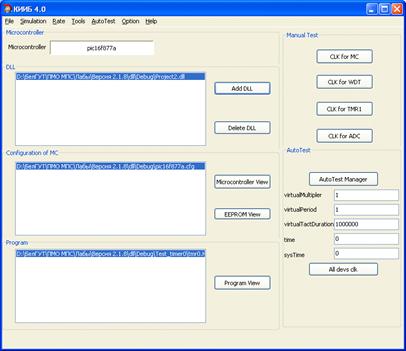

Внешний вид разработанной формы представлен на рисунке

2.1.

Все органы управления и отражения оперативной информации о работе приложения на форме разбиты на функциональные блоки, разделенные между собой графическими границами. Рассмотрим эти блоки подробнее:

· Главное меню - позволяет осуществлять вызов функций приложения. Назначение основных функций, содержащихся в меню, будет описано ниже.

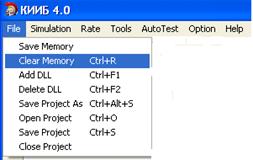

Вкладка «File» объединяет функции, позволяющие выполнять работу с файлами,

необходимыми для создания модели (рисунок 2.2).

Вкладка «AutoTest» содержит функцию запуска режима автоматического

тестирования (рисунок 2.4).

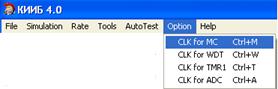

Вкладка «Option» объединяет функции, отвечающие за отладку модели устройства в ручном

режиме (рисунок 2.5).

Вкладка «Help» содержит функцию, вызывающую окно с

данными об авторе разработанного проекта (рисунок 2.6).

· Блок «Microcontroller» - содержит информационную панель, на которой отражается марка микроконтроллера семейства PIC16, выбранный в качестве действующей модели.

· Блок «DLL» - содержит информационную панель, на которой

отражены загруженные файлы расширения *.dll. Фактически его загрузка создает

новое устройство, которое может участвовать в моделировании. Для управления

загрузкой таких файлов имеются кнопки «Add DLL» (позволяет загрузить файл модели устройства) и «Delete DLL» (позволяет удалить выделенное в информационном окне

устройство). Перечисленные функции продублированы в главном меню проекта

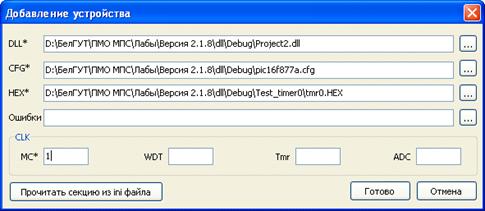

(рисунок 2.2). При нажатии кнопки загрузки файла перед пользователем возникает

диалог (рисунок 2.7).

Все поля разработанного диалога, отмеченные «*», являются обязательными для заполнения.

Данный диалог предлагает пользователю указать путь к файлу расширения *.dll; путь к файлу расширения *.cfg, который является файлом конфигурации выбранного микроконтроллера семейства PIC16; путь к файлу расширения *.hex, в котором находится загружаемая в микроконтроллер программа. Предоставляется возможность загрузить файл с вносимыми в работу микроконтроллера ошибками (ini-файл).

Блок CLK предлагает пользователю задать частоты (в МГц), на которых будут работать основные модули устройства: непосредственно сам микроконтроллер (MC), сторожевой таймер (WDT), таймер 1 (Tmr), АЦП (ADC). С помощью кнопки «Прочитать секцию из ini файла» все требуемые параметры могут быть загружены непосредственно из файла.

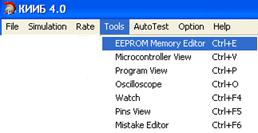

· Блок «Configuration of MC» представлен информационной панелью, на которой отражаются загруженные конфигурации каждой из задействованных моделей устройств. После успешной загрузки файла конфигурации у пользователя появляется возможность просмотра состояния памяти данных устройства (кнопка «Microcontroller View») и его энергонезависимой памяти (кнопка «EEPROM View»). Данные функции доступны и из главного меню (рисунок 2.3).

· Блок «Program» представлен информационной панелью, на которой отражаются загруженные файлы программ каждой из задействованных моделей устройств. После успешной загрузки программы появляется возможность просмотра состояния памяти программ выбранной модели устройства (кнопка «Program View»). Данная функция может быть вызвана из главного меню (рисунок 2.3).

· Блок «Manual Test» позволяет управлять работой одной модели устройства в режиме ручной отладки. Содержит 4 органа управления: кнопка имитации такта микроконтроллера («CLK for MC»), кнопка имитации такта для сторожевого таймера («CLK for WDT»), кнопка имитации такта для таймера 1 («CLK for TMR1»), кнопка имитации такта для АЦП («CLK for ADC»). Данная функциональность может быть вызвана и из главного меню (рисунок 2.5).