Материал: 835

155

Первоначально микросхемы DRAM-памяти, например FPM или EDO, работали независимо от тактовых импульсов, передаваемых по шине, т.е. асинхронно. При работе памяти этих типов обычна ситуация, когда микросхемы памяти уже подготовили данные, запрошенные контроллером, и готовы начать их передачу, но ждут для этого прохождения по шине очередного тактового импульса. Причем контроллер памяти не управляет временными параметрами этого процесса и не в состоянии определить, сколько времени нужно микросхемам памяти, чтобы подготовить данные для передачи, и на каком такте она начнется.

SDRAM — это синхронная память. Ее работа построена так, что все операции выполняются по тактовым импульсам. И в этом случае контроллер памяти, например, точно знает, в течение скольких тактов микросхемы памяти будут готовить запрошенные данные для передачи, и на каком такте начнется собственно их передача. Жесткая синхронизация с тактовым сигналом упрощает логику управления работой подсистемы памяти, сокращает расход времени на передачу служебной информации и, в конечном счете, повышает скорость работы памяти.

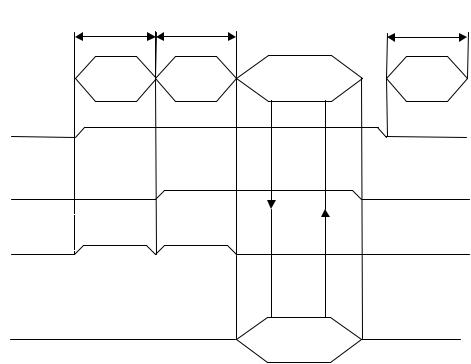

В SDRAM-памяти цикл чтения-записи данных осуществляется за несколько шагов.

tRC |

tCL |

Микросхема |

|

памяти |

|

Выборка |

Выборка |

сроки |

столбца |

RAS |

|

Командная |

CAS |

|

|

шина |

|

|

|

|

|

Адрес |

Адрес |

|

Адресная |

||

|

сроки |

столбца |

|

|

шина |

||

|

|

|

|

|

|

|

|

Шина

данных

|

tRP |

Чтение-запись |

Зарядка |

данных |

|

чтение |

запись |

Чтение-запись

Рис. 5.3

156

1. На адресной шине выставляется адрес строки, а на командной активируется стробирующий сигнал строк RAS (Row

Address Strobe).

2.Приняв сигнал RAS, микросхема памяти определяет, что на адресной шине выставлен адрес строки, с которой ей предстоит работать, и записывает его в свой внутренний регистр, после чего необходимость в удержании последнего на адресной шине пропадает.

3.Микросхема считывает данные с конденсаторов нужной строки и записывает их в буферный усилитель. Естественно, что для выполнения этой операции ей требуется какое-то время, называемое RAS-to-CAS Delay (задержка сигнала CAS после сигнала RAS), которое обычно составляет 2—3 тактовых цикла и обозна-

чается tRCD.

4.На адресной шине выставляется адрес столбца (или столбцов), а на командной активируется стробирующий сигнал столбцов CAS (Column Address Strobe).

5.Микросхема памяти, приняв сигнал CAS, определяет, с каким элементом (или элементами) строки данных, записанной ранее в буферный усилитель, ей предстоит работать, и готовится

ктому, чтобы выдать его (их) значения на шину данных. Для совершения этой операции ей так же требуется время, называемое CAS Latency (задержка после сигнала CAS), которое, как правило, составляет 2—3 цикла и обозначается tCL.

6.Чтение или запись данных. При чтении данные, ранее подготовленные микросхемой к выдаче, подаются на шину данных и считываются контроллером памяти. При записи данные, выданные ранее контроллером памяти на шину данных, записываются в соответствующие ячейки строки, находящейся в буферном усилителе.

7.Снятие сигнала CAS. Исчезновение сигнала CAS с командной шины означает, что все операции ввода-вывода данных закончились.

8.Снятие сигнала RAS. Исчезновение сигнала RAS означает, что прекращена работа со строкой данных, находящейся в буферном усилителе.

9.Зарядка конденсаторов. На этом этапе значения ячеек строки, находящейся в буферном усилителе, записываются в со-

157

ответствующие конденсаторы в микросхеме памяти, после чего микросхема будет снова готова к выполнению очередного цикла чтения-записи данных. Длительность этого этапа называется RAS Precharge Time (время заряда до сигнала RAS), поскольку, как только он завершится, на командную шину можно снова подавать сигналRAS. Она составляет2—3 тактовых цикла иобозначаетсяtRP.

В последнее время все рабочие характеристики модулей SDRAM-памяти записываются в установленные на них SPD- микросхемы (Serial Presence Detect). Системная плата может считать данные, прошитые в SPD-микросхемах, и в соответствии с ними автоматически установить режим работы с модулями SDRAM-памяти. Однако ряд рабочих параметров SDRAMпамяти все же можно настроить средствами программ настройки BIOS современных системных плат, что можно использовать для разгона или, наоборот, замедления памяти — в том случае, если она работает неустойчиво. Отметим наиболее важные из них.

DRAM Clock. Частота тактового сигнала шины памяти. Стандартно — 100, 133 МГц или By SPD (в соответствии со значением, хранящимся в SPD-микросхеме).

SDRAM RAS-to-CAS Delay. Время задержки сигнала CAS

после сигнала RAS — 2 или 3 тактовых цикла.

SDRAM CAS Latency. Время задержки после сигнала CAS — 2, 2,5 или 3 тактовых цикла.

SDRAM RAS Precharge Time. Время заряда до сигнала RAS — 2 или 3 тактовых цикла.

DRAM Timing. Схема работы SDRAM-памяти в пакетном режиме. Характерные значения — 5-1-1-1, 5-2-2-2.

Данные из SDRAM-памяти могут читаться в режиме произвольного или пакетного (burst) доступа. При произвольном доступе по шине данных однократно передается один элемент данных (например, одно слово), после чего цикл чтения заканчивается. При этом от момента подачи сигнала RAS до момента начала передачи данных по шине в идеальном случае проходит пять тактовых циклов: ожидание в течение времени tRCD — 2 такта, подача на адресную шину адреса столбца (или столбцов) и активирование на командной шине сигнала CAS — 1 такт, ожидание в течение времени tCL — 2 такта.

158

При пакетном доступе после передачи по шине первого элемента данных цикл чтения не заканчивается, а продолжается. При этом каждый последующий такт контроллер памяти считывает еще один элемент данных, который находился в той же строке данных, что и первый, и вместе с ним был «выдан» микросхемой памяти на шину данных. Как правило, при пакетном доступе за один цикл чтения обрабатывается до четырех или восьми элементов. В идеальном случае при передаче четырех элементов эта схема обозначается как «5-1-1-1», а при восьми —

«5-1-1-1 — 1-1-1-1».

DRAM Burst Length. Количество элементов, передаваемых за один цикл в пакетном режиме, — 4 или 8.

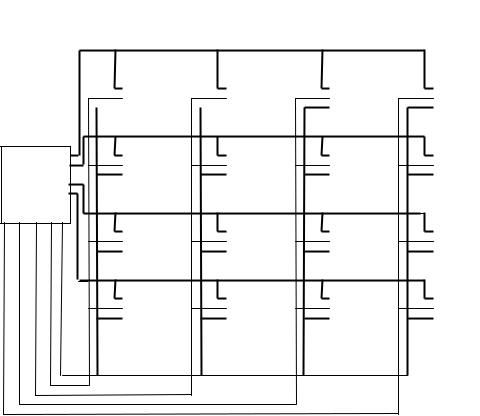

Bank Interleave. Чередование банков памяти. Стандартно: Disabled — не использовать чередование банков, 2 Bank — чередование между двумя банками, 4 Bank — между четырьмя банками.

Отдельные микросхемы памяти объединяются в логические банки, с которыми можно работать одновременно. Такой прием называется «чередованием банков» (Bank Interleaving) и ускоряет работу памяти. Например, если требуется последовательно считать данные сначала из первого банка, а потом из второго, то контроллер памяти может начать считывать данные из второго банка, не дожидаясь окончания цикла чтения из первого.

5.2.6 Память РС 100/ РС 133

РС 133. Из всех широко используемых в настоящее время типов ОЗУ память SDRAM (Synchronous Dynamic RAM) — самая старая. Ширина шины данных SDRAM — 64 бит, выпускается она в виде 168-контактных DIMM-модулей (Dual In-line Memory

Module).

Тактовая частота первой памяти этого типа (она обозначалась как РС 66 SDRAM) — 66 МГц, пропускная способность — 533 Мбайт/c. По мере совершенствования технологии производства тактовая частота шины SDRAM-памяти увеличивалась сначала до 100 МГц (PC 100, пропускная способность — 800 Мбайт/с), а потом и до 133 МГц (РС 133, пропускная способность —

1066 Мбайт/с).

159

Если сравнивать память PC 133 с современными типами ОЗУ — DDR SDRAM и RDRAM — по пропускной способности, то с первого взгляда можно прийти к выводу, что у PC 133, проигрывающей по этому параметру в 2—3 раза, нет никаких перспектив на рынке памяти для современных ПК. Однако, как показали проведенные испытания, это совершенно не так. PC 133 вполне конкурентоспособна при построении систем, предназначенных для работы с офисными программами (проигрыш по сравнению с DDR SDRAM и RDRAM составил всего лишь 1—4 %), двумерной графикой (2—10/6—10 %), мультимедийными пакетами

(5—11/5—12 %) и даже ЗD-приложениями (5—9/6—11 %).

Контроллер памяти

|

|

Модуль |

|

|

|

Модуль |

|

|

|

|

Модуль |

|

|

Модуль |

|

|||||||||

|

|

Памяти |

|

|

|

Памяти |

|

|

|

|

Памяти |

|

|

Памяти |

|

|||||||||

|

|

DIMM0 |

|

|

|

DIMM1 |

|

|

|

|

DIMM2 |

|

|

DIMM3 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

SDRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Адресная шина

Шинаданных

Рис. 5.4

Более того, как ни мощны современные процессоры, но и они не всегда могут в полной мере реализовать возможности, казалось бы, такой медленной памяти, как PC 133. Так, если в приложении работа ЦП с ОЗУ никак не оптимизируется, то очень часто шина памяти РС 133 для Pentium 4 2,0 ГГц будет задействована чуть больше чем наполовину (56 %), для Athlon ХР1900+ —