Материал: Захаров, Сайфутдинов - Вычислительная техника

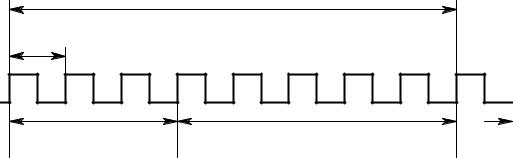

Общее время выполнения команды |

|

|

Цикл генератора тактовой частоты |

|

|

Интервал выборки |

Интервал выполнения |

t |

команды |

операции |

|

Рис. 7.5. Интервалы выполнения команды |

|

|

|

|

|

Таблица 7.1 |

|

|

|

|

Наименова- |

Цикл |

|

Активные |

генератора |

Выполняемая микрооперация |

линии |

|

ние |

тактовой |

магистрали |

|

интервала |

|

||

|

частоты |

|

управления |

|

1 |

Пересылка адреса команды из программ- |

2 и 5 |

|

|

ного счетчика по МА в регистр адреса |

|

Выборка |

|

памяти |

|

команды |

|

|

|

2 |

Пересылка кода адресуемой команды из |

3 и 6 |

|

из памяти |

|

ячейки памяти по МД в регистр команд |

|

|

|

|

|

|

|

Наращивание содержимого программного |

1 |

|

|

счетчика (формирование адреса следую- |

|

|

|

щей команды) |

|

|

|

|

|

|

3 |

Пересылка адреса операнда из регистра |

4 и 5 |

|

|

команд по МА в регистр адреса памяти |

|

|

|

|

|

Выполнение |

4 |

Пересылка адресуемого операнда из ячей- |

6 и 8 |

операции |

|

ки памяти по МД в операционный блок |

|

|

5 |

Выполнение заданной операции над |

9 |

|

|

операндом в операционном блоке |

|

|

|

|

|

|

6 |

Запись результата операции в аккумулятор |

12 |

|

|

|

|

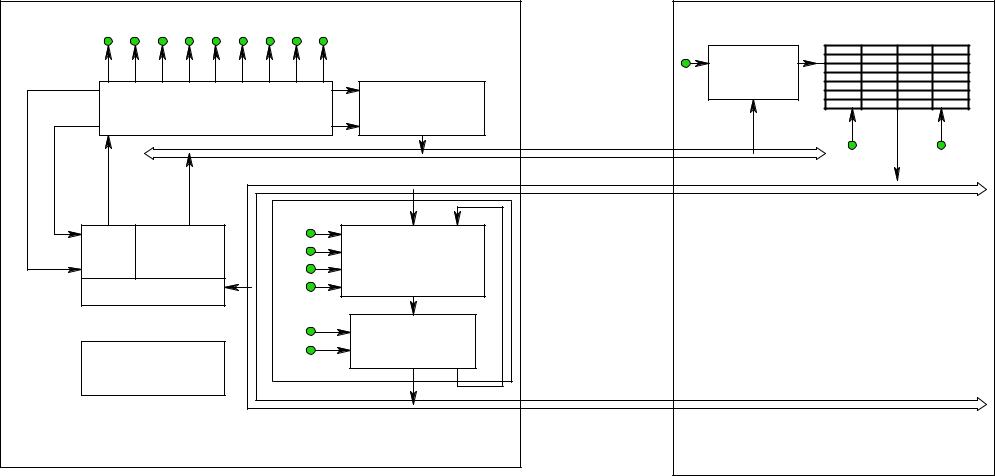

В первом цикле адрес команды, хранящийся в программном счетчике, пересылается по МА в регистр адреса памяти. С этой целью УУ выдает одновременно два управляющих сигнала по линиям 2 и 5 (рис. 7.6).

146

|

5 |

6 |

7 |

8 |

9 |

10 11 |

12 |

13 |

|

Блок ячеек памяти |

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

4 |

|

|

|

|

|

|

1 |

|

Регистр |

|

|

|

|

|

|

|

|

|

адреса |

|

||

|

|

|

|

|

|

|

|

Программный |

|

||

|

3 |

Устройство управления |

2 |

|

|

||||||

|

|

|

|

|

|

|

|

счетчик |

|

|

|

|

|

|

|

|

|

|

|

|

Магистраль адресов |

|

|

|

|

|

|

|

|

|

|

|

Магистраль данных |

6 |

7 |

|

|

|

|

|

|

|

АЛУ |

|

|

|

|

|

|

|

Адрес |

|

|

8 |

|

|

|

|

|

|

КОП |

|

|

|

9 |

|

Операционный |

|

|

||

|

|

операнда |

|

|

|

|

|

||||

147 |

|

|

|

|

|

|

10 |

|

блок |

|

|

Регистр команд |

|

|

11 |

|

|

|

|

||||

|

|

|

|

|

|

|

12 |

|

Аккумулятор |

|

|

|

Блок регистров |

|

|

13 |

|

|

|

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||

|

общего назначения |

|

|

|

|

|

|

||||

|

|

|

|

МИКРОПРОЦЕССОР |

|

ОСНОВНАЯ ПАМЯТЬ |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 7.6. Структурная схема МП |

|

|

Во втором цикле, путем одновременной активизации линий 3 и 6, код команды, адрес которой теперь имеется в регистре адреса памяти, пересылается из адресуемой ячейки памяти по МД в регистр команд. В этом же цикле путем активизации линии 1 от УУ одновременно наращивается содержимое программного счетчика так, чтобы получился адрес следующей команды программы. Обычно этот адрес получается прибавлением одной и той же константы (например, 1) к адресу текущей команды. Эта константа формируется автоматически.

Второй цикл завершает интервал выборки команды из памяти в микропроцессор. Код команды находится в регистре команд. Одна часть этого кода содержит КОП, а другая часть — адрес операнда (числа) в памяти, над которым должна выполняться требуемая операция. Далее начинается интервал выполнения операции, заложенной в данной команде. Конкретная последовательность выдачи управляющих сигналов от УУ на интервале выполнения операции полностью зависит от КОП.

Врассматриваемомпримереинтервал выполнения операциисодержит циклы 3, 4, 5 и6.

Втретьем цикле адрес операнда из регистра команд пересылается по МА в регистр адреса памяти подачей сигналов от УУ по линиям 4 и 5.

Вчетвертом цикле адресуемый операнд пересылается из соответствующей ячейки памяти по МД в операционный блок путем активизации линий 6 и 8.

Впятом цикле над операндом, засланным в операционный блок, осуществляется требуемая операция прибавления единицы. Увеличение содержимого операционного блока на единицу достигается самим операционным блоком при подаче на него управляющего сигнала по линии 9 от УУ.

Вшестом цикле увеличенное на единицу содержимое операционного блока пересылается в аккумулятор под действием управляющего сигнала по линии 12 от УУ. На этом выполнение команды завершается.

Так как в этот момент программный счетчик уже содержит адрес следующей команды, то в очередном цикле генератора тактовой частоты немедленно начинается первый шаг новой команды. Эта новая команда может, например, осуществить суммирование числа в аккумуляторе (т. е. результата предыдущей команды) с числом из какой-нибудь ячейки памяти и записать полученную сумму в другую ячейку памяти или же в один из регистров общего назначения. Выполняя одну команду за другой, МП продолжает работать до тех пор, пока не встретится команда останова или оператор принудительно не остановит микроЭВМ нажатием соответствующей клавиши.

148

7.5. Организация интерфейса в микроЭВМ

Интерфейс (interface) – совокупность средств сопряжения и связи, обеспечивающая эффективное взаимодействие систем или их частей. В интерфейсе предусмотрены вопросы сопряжения на механическом (число проводов, элементы связи, типы соединений, разъемы, номера контактов и т. п.) и логическом (сигналы, их длительность, полярность, частоты и амплитуда, протоколы взаимодействия) уровнях. В современных интерфейсах для формирования стандарта подключения устройств к системе широко используются наборы микросхем, генерирующих стандартные сигналы.

Внутримашинный интерфейс – система связи и сопряжения узлов и блоков компьютера, представляет собой совокупность электрических линий связи, схем сопряжения с компонентами компьютера, протоколов (алгоритмов) передачи и преобразования сигналов.

В функции интерфейса входят дешифрация адреса устройств, синхронизация обмена информацией, согласование форматов слов, дешифрация кода команды, связанной с обращением к периферийному устройству, электрическое согласование сигналов и другие операции. Интерфейс должен осуществлять совместимость между всеми компонентами микроЭВМ по быстродействию, форме представления обмениваемой информации, архитектуре центрального процессора и электрическим характеристикам.

Из всего многообразия типов микроЭВМ можно выделить две основные организации интерфейса между процессором, памятью и периферийными устройствами: двухшинную, или интерфейс с изолированной системой шин, и одношинную, или интерфейс с общей шиной.

Интерфейс с изолированной шиной. Особенностью этого интерфейса является раздельная адресация памяти и периферийных устройств при обмене информацией путем использования отдельных групп команд для обмена информацией с периферийными устройствами и памятью. Обмен с периферийными устройствами производится с помощью двухбайтных команд ввода IN PORT и вывода OUT PORT, а управление обменом — под воздействием управляющих сигналов ввода и вывода,

149

формируемых системным контроллером при выполнении соответствующих команд. Адрес из МП передается по МА, передача данных выполняется по МД между аккумулятором и буферным регистром интерфейсного модуля (портом) периферийного устройства. Обмен информацией между МП и памятью производится по командам передачиданных.

Основным недостатком организации интерфейса с изолированной шиной является осуществление обмена обязательно через аккумулятор МП, что, как правило, требует выполнения четырех команд.

Интерфейс с общей шиной. При данной организации интерфейса все адресное пространство делится между периферийными устройствами и ячейками памяти, причем обращение к периферийным устройствам осуществляется посредством набора команд, используемых для передачи данных с памятью. Достоинствами данного интерфейса являются:

возможность расширения набора команд для обращения к периферийным устройствам, что позволяет сократить объем программ и повысить быстродействие;

возможность обмена информацией между любыми регистрами МП;

возможность внепроцессорного обмена данными между ячейками памяти. Недостатком интерфейса с общей шиной является усложнение дешифрирую-

щих схем и сокращение области памяти.

Общая шина (ОШ) это — магистраль, которая связывает между собой все периферийные устройства, запоминающие устройства и процессор. Все устройства, включая процессор, подсоединены в общую шину параллельно.

Взаимодействие устройств на ОШ основано на принципе ведомый-ведущий (задатчик — исполнитель). Задатчик получает ОШ в свое распоряжение на промежуток времени для определения операции ввода-вывода с исполнителем. Одно и то же устройство может быть и задатчиком, и исполнителем (в зависимости от типа операции). На ОШ можно организовать автономный обмен данными непосредственно между двумя ВУ без привлечения для этого ресурсов процессора и ОП.

Все передачи по ОШ осуществляются асинхронно по методу запрос-ответ. В случае неполучения ответного сигнала от исполнителя задатчик фиксирует ошибку в работе ОШ и выполняет операцию прерывания.

150

Смотрите также:

| 00539 |

| 02.03 |

| 0501 Конунников ЛР1-1 |

| 10Лекция 10 |

| 1136 |

| 1304 |

| 131 |

| 1362 |

| 15.02.16 1 пара |

| 1741 |