Материал: Лаба шифратор-дешифратор

Входы |

Выходы |

||||||

Е |

Х1 |

Х0 |

Y3 |

Y2 |

Y1 |

Y0 |

|

1 |

x |

x |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

|

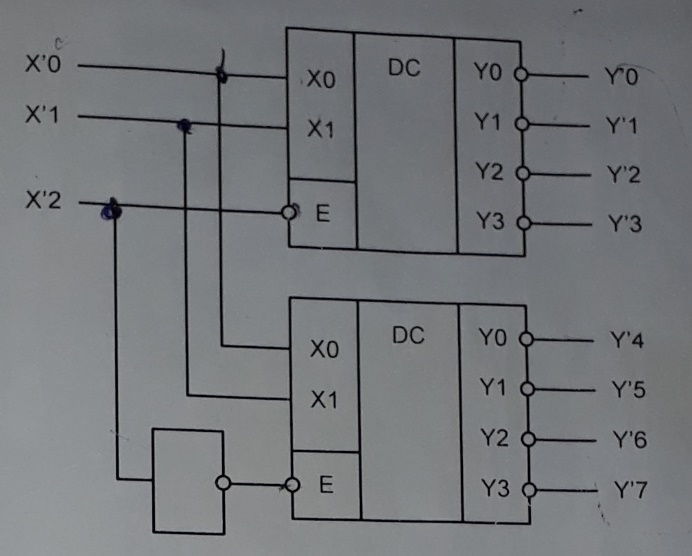

На рис. 3.4 приведена схема наращивания разрядности дешифратора. Для построения дешифратора 3х8 на основе двух полных дешифраторов 2х4 нужно соединить параллельно их входы Х0 и Х1. Входной сигнал Х2 подключается непосредственно ко входу разрешения Е младшего дешифратора и через инвертор ко входу разрешения Е старшего дешифратора.

Рисунок 3.4 условное обозначение дешифратора 3х8

В зависимости от состояния сигнала Х2 только один из выходных дешифраторов будет реагировать на комбинацию сигналов на входах Х0 и Х1. Только выбранный дешифратор сформирует единицу на одном из своих выходов, номер которого определяется сигналами х0 и х1. Например, если на входах X2 X1 X0 присутствует число 101, то единичный сигнал в разряде Х2 запретит работу младшего дешифратора и на его выходах установятся единичные сигналы. На вход разрешения старшего дешифратора единичный сигнал Х2 поступает после инвертирования и разрешает его работу. В результате нулевой уровень появится на выходе Y5.

Дешифраторы находят широкое применение в вычислительной технике. В составе компьютеров, например, дешифраторы позволяют адресоваться к определенному устройству, с которым в данный момент осуществляется обмен информацией. Для этого достаточно подключить вход разрешения работы этого устройства к соответствующему выходу дешифратора, а входы дешифратора использовать для задания адреса устройства.

Технические характеристики дешифратора КР531ИД14:

Напряжение питания: 5В ±5%

Выходное напряжение низкого уровня: 0..0.5В

Выходное напряжение высокого уровня 2.7..5В

Токи потребления: до 90мА

Входной ток: 2мА для низкого уровня, 0.05мА для высокого уровня

Потребляемая мощность: до 450мВт

Время задержки: от 7.5 нс до 12нс

Коэффициент разветвления по выходу: 20

4.Выполнение работы:

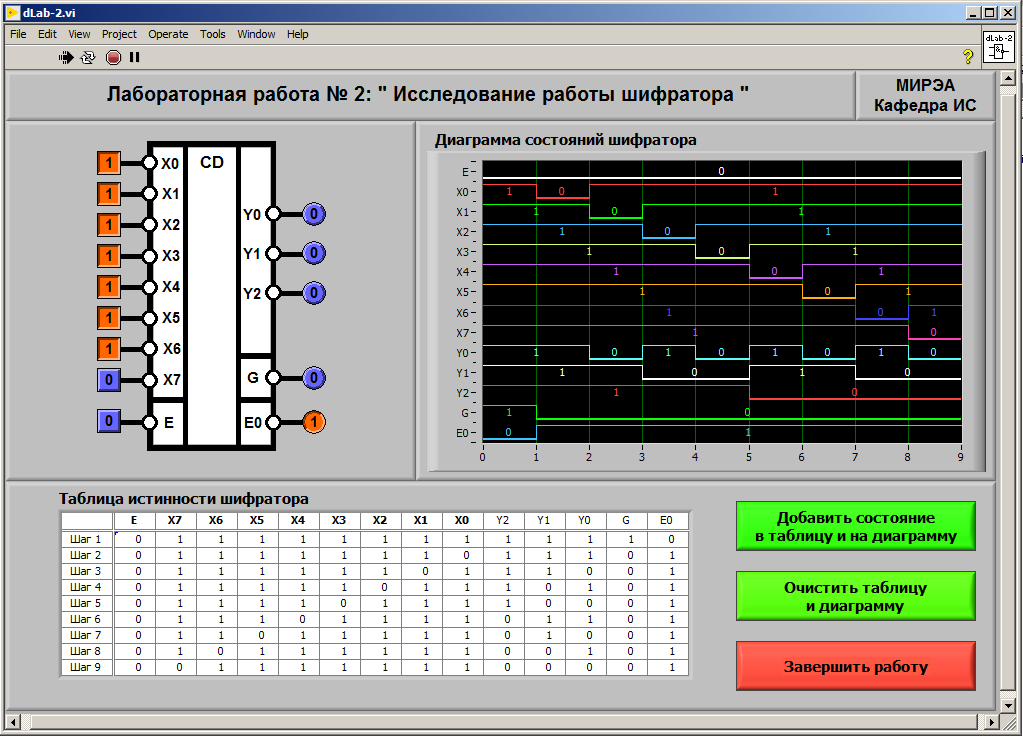

Исследование работы шифратора:

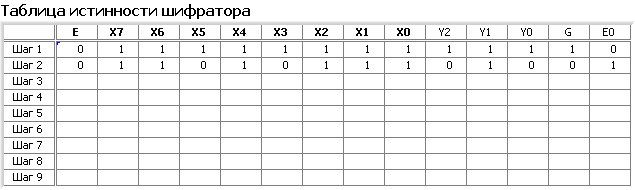

Результат выполнения пунктов 1-6 представлен на рисунке 4.1

Рисунок 4.1 Иллюстрация работы шифратора

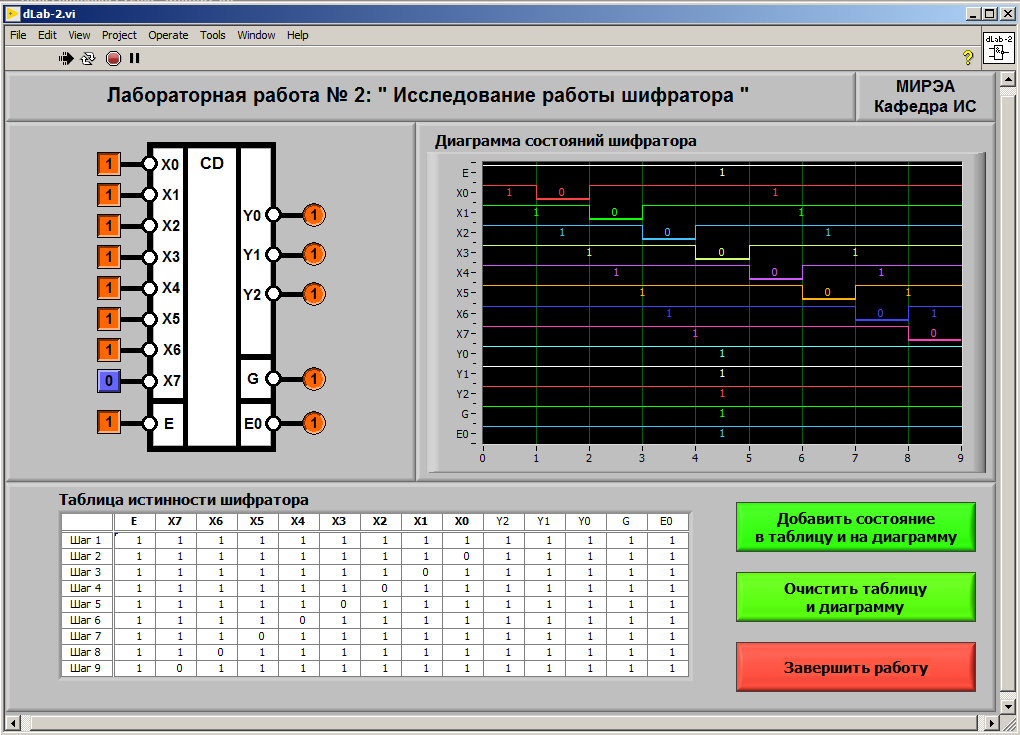

Результат выполнения пункта 8 представлен на рисунке 4.2.

Рисунок 4.2 Иллюстрация работы шифратора

Проверка приоритетности

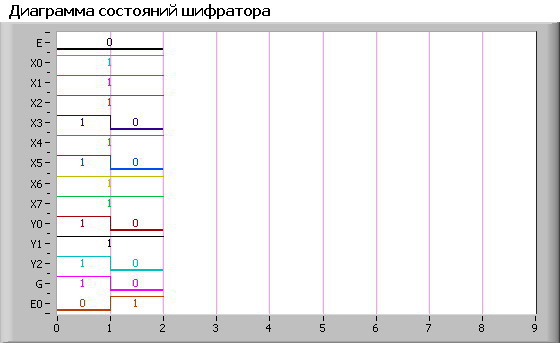

Диаграмма состояний проверки приоритетности шифратора показана на рис. 4.3

Рисунок 4.3 Диаграмма состояний

Таблица истинности шифратора представлена на рисунке 4.4

Рисунок 4.4 Таблица истинности шифратора

Активные сигналы поданы на входы X3 и X5. Состояние инверсных выходов Y0, Y1, Y2 соответственно равны 0, 1, 0, что соответствует двоичному числу 101 (5), что указывает на то, что вход с большим порядковым номером обладает большим приоритетом.

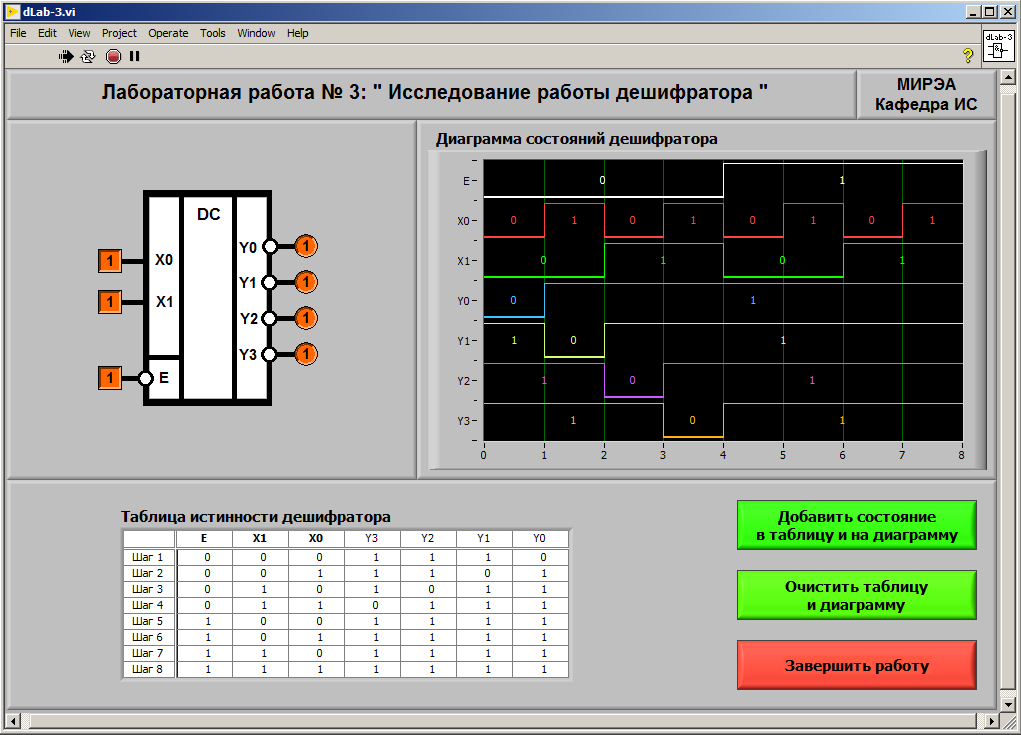

Исследование работы дешифратора:

Результат

выполнения пунктов 1-7 представлен на

рисунке 4.5

Рисунок 4.5 Иллюстрация работы дешифратора

Вывод:

При выполнении лабораторной работы была исследована работа шифратора и дешифратора.